Determinismo da fase de inicialização:Sintetizador PLL e calibração no nível do sistema

Na primeira parte desta série de artigos, exploramos como alcançar fases (determinísticas) conhecidas para todos os canais dentro de chips integrados com blocos de processamento de sinal digital múltiplo (DSP), conversores digital-analógico de banda larga (DACs) e analógico de banda larga conversores -para-digital (ADCs). Começamos com um diagrama de blocos do sistema de alto nível empregando uma estrutura de árvore de relógio de subarray e descrevemos um método de sincronização multichip. Nesta segunda parte, exploraremos os ajustes de fase do sintetizador PLL, escalabilidade para múltiplos subarrays e algoritmos de calibração de nível de sistema.

Ajustes de fase do sintetizador PLL

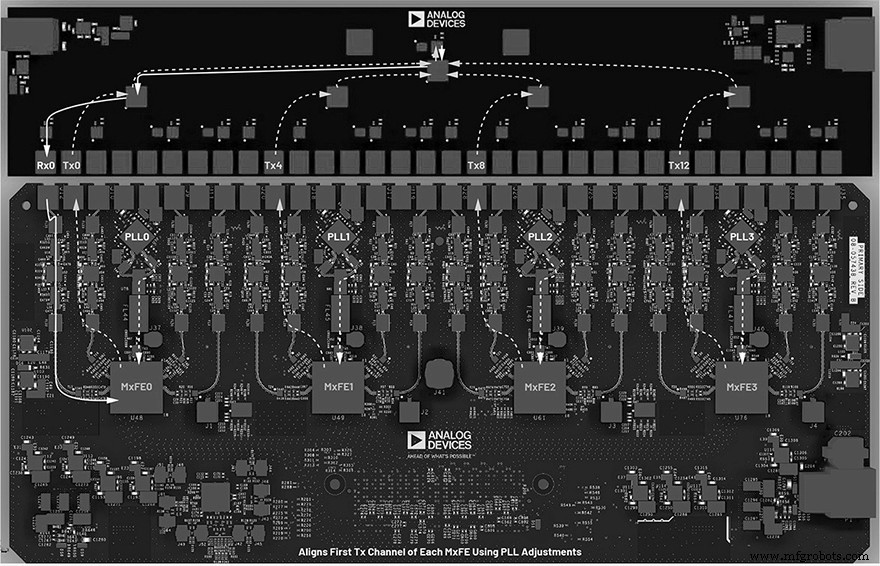

Os CIs de sintetizador PLL escolhidos foram selecionados para permitir ajustes de fase de clock de amostragem relativos injetados em cada CI digitalizador. O desvio térmico e o desvio de fase PLL resultante entre o relógio de amostra e o SYSREF de cada IC são compensados pela criação de um mecanismo de feedback que garante que o primeiro canal de transmissão de cada IC do digitalizador esteja alinhado por fase ao primeiro canal de transmissão do primeiro IC do digitalizador. Para atingir esse loop de feedback, o primeiro canal de transmissão de cada IC emite um sinal que se diferencia dos outros canais de transmissão, conforme mostrado na Figura 1. Esses quatro sinais são combinados e enviados para um receptor comum, que para este sistema é denominado Rx0 .

clique para ver a imagem em tamanho real

Figura 1. Um recurso de ajuste de fase do sintetizador PLL permite que o primeiro canal de transmissão de cada IC do digitalizador seja alinhado ao submatriz. (Fonte:Dispositivos analógicos)

Os dados de recepção simultânea são obtidos para todos os canais de recepção, o que permite aos usuários aplicar técnicas de correlação cruzada e determinar os deslocamentos de fase complexos entre esses quatro canais de transmissão, Φ TxOffset . Os CIs de sintetizador PLL contêm dentro deles um oscilador controlado por voltagem (VCO) que está operando em uma frequência ƒ VCO_PLL .

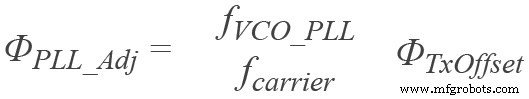

Os deslocamentos de fase medidos Φ TxOffset são então relacionados ao ajuste de fase PLL necessário Φ PLL_Adj e a frequência RF ƒ operadora de tal modo que:

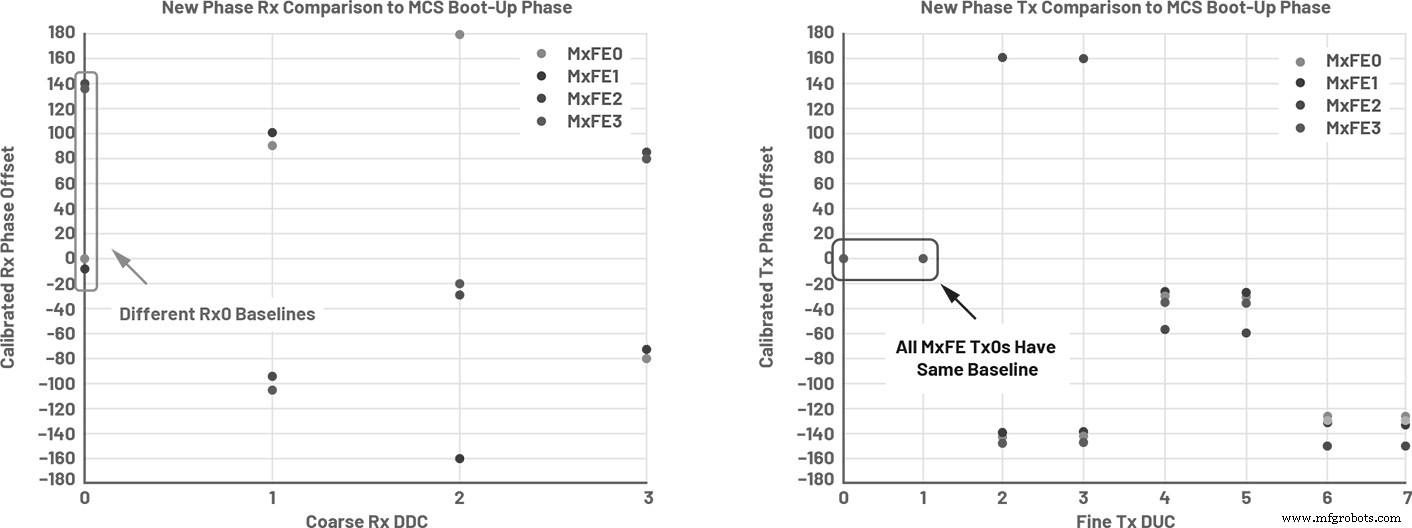

Usando esta fórmula, as fases do sintetizador PLL podem ser ajustadas por um novo valor conhecido para estabelecer uma linha de base de transmissão comum entre todos os CIs digitalizadores para todos os ciclos de energia, como mostrado na Figura 2. Os círculos abertos para cada canal mostrado na Figura 2 correspondem ao primeiro ciclo de energia, enquanto todos os outros pontos sólidos correspondem aos ciclos de energia subsequentes. Como pode ser visto nesta figura, os deslocamentos de fase de transmissão calibrados para o primeiro (e segundo) canalizadores de todos os CIs digitalizadores são alinhados por fase. O segundo canalizador de cada CI digitalizador também está alinhado nesta instância, porque dois canalizadores são usados para cada DAC no sistema.

Adicionar esta etapa de ajuste de fase do sintetizador PLL antes das rotinas MCS discutidas na seção anterior cria, assim, uma fase determinística em todos os gradientes térmicos induzidos dentro do sistema, forçando o sistema para a mesma relação de fase de relógio de amostra-SYSREF, que se manifesta como uma transmissão linha de base do alinhamento em todos os CIs do digitalizador.

clique para ver a imagem em tamanho real

Figura 2. Ajustando a fase PLL, o usuário pode alinhar o primeiro canal de transmissão de todos os CIs digitalizadores. (Fonte:Dispositivos analógicos)

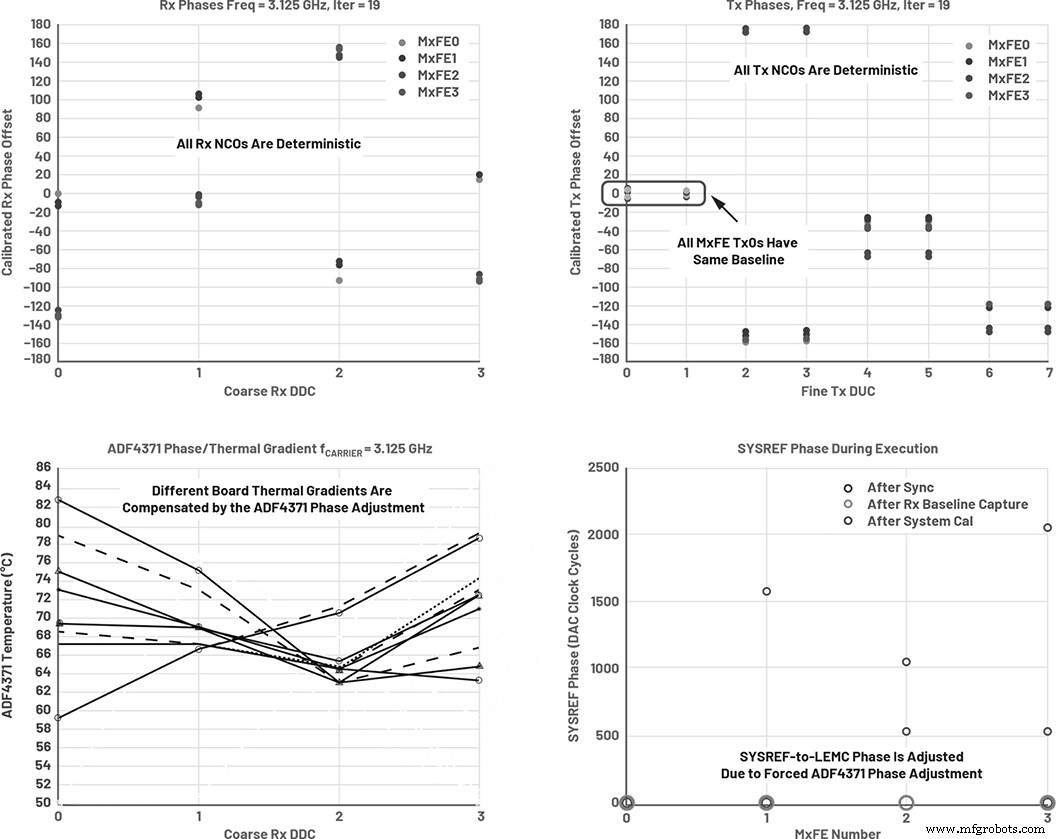

A Figura 3 mostra que um gradiente térmico induzido pode ser detectado por meio da unidade de medição de temperatura (TMU) em cada chip de sintetizador PLL. Como pode ser visto a partir do traço azul no canto inferior esquerdo da Figura 3, temperaturas amplamente variáveis em toda a plataforma foram intencionalmente induzidas pela aplicação de diferentes fluxos de ar do ventilador ao sistema. Usar o ajuste de fase PLL para cada IC, no entanto, demonstra que, independentemente do fluxo de ar aplicado à placa, os desvios de fase NCO calibrados para cada canal de recepção e transmissão são determinísticos ao forçar o primeiro canalizador de transmissão de cada IC digitalizador a ser alinhado a cada de outros. Isso é revelado pela observação do aglomerado compacto da mesma cor de pontos nos dois gráficos superiores na Figura 3, apesar dos diferentes gradientes térmicos aplicados à placa durante diferentes ciclos de energia.

clique para ver a imagem em tamanho real

Figura 3. O recurso MCS usado em conjunto com o recurso de ajuste de fase PLL demonstra o determinismo de fase de inicialização para todos os canais de recepção e transmissão, independentemente do gradiente térmico induzido na plataforma. (Fonte:Dispositivos analógicos)

Mostrado na parte inferior direita da Figura 3 estão os registros IC do digitalizador pesquisados, que mostram a relação de fase SYSREF-LEMC medida após a aplicação do deslocamento de fase do sintetizador PLL. Observe nos traços laranja no gráfico inferior esquerdo que os ajustes de fase do sintetizador PLL compensam totalmente quaisquer fases SYSREF diferentes de zero medidas resultantes de um gradiente térmico induzido diferente.

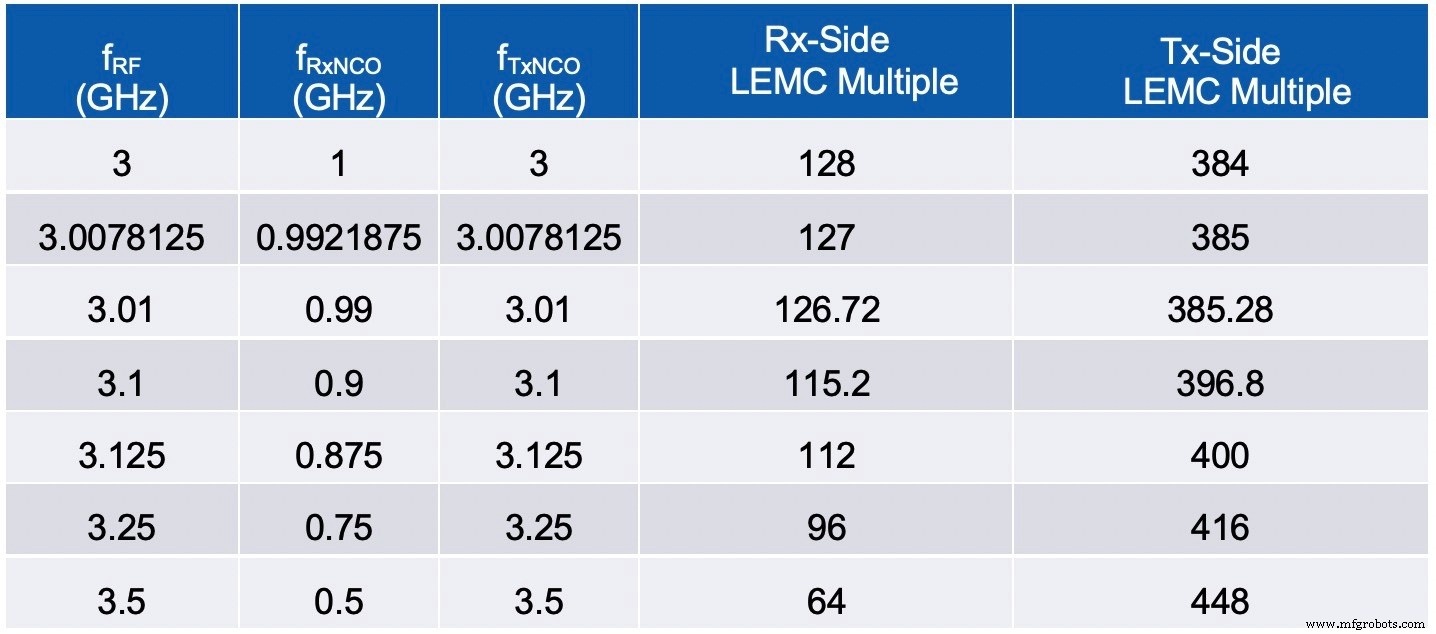

Muitas frequências foram medidas, todas demonstrando fase de recepção e transmissão determinística. As frequências específicas escolhidas para este artigo são mostradas na Figura 4 e foram escolhidas de modo que MCS seja demonstrado em muitos gradientes térmicos induzidos ao usar múltiplos não inteiros do relógio de referência ou o LEMC.

Figura 4. As frequências RF usadas neste artigo são escolhidas para demonstrar as funções MCS em uma ampla gama de fontes de relógio, incluindo múltiplos não inteiros do relógio de referência e LEMC. (Fonte:Dispositivos analógicos)

Escalabilidade para Múltiplos Subarrays

Os dados mostrados neste artigo se concentram principalmente no desempenho do MCS no nível do submatriz, mas também é necessário garantir que esses recursos de sincronização sejam realizáveis no nível do array maior e em vários submatrizes. Para atingir este nível mais alto de sincronização, uma árvore de relógio de nível de array é necessária para garantir que as solicitações SYSREF para cada subarray mostrado na Figura 1 na Parte 1 cheguem de forma síncrona em cada IC de buffer de relógio de subarray. Então, dado este critério, cada submatriz pode emitir os SYSREFs e relógios BBP necessários, conforme descrito anteriormente, de modo que esses sinais cheguem aos CIs digitalizadores de submatriz e BBP dentro do mesmo ciclo de relógio de amostra na matriz maior. Esta árvore de clock de nível de array requer que a distribuição de clock para cada subarray possua os blocos de ajuste de atraso necessários para alcançar a distribuição de solicitação SYSREF síncrona para cada um dos CIs de chip de clock de subarray downstream. Dessa maneira, vários BBPs conectados a vários subarrays são finalmente sincronizados.

Algoritmo de calibração no nível do sistema

Embora os algoritmos MCS mostrados nas seções anteriores forneçam fase determinística de energização para cada canal de recepção e transmissão, essas fases não são necessariamente alinhadas por fase em todos os canais dentro do domínio de RF devido a quaisquer diferenças nos comprimentos de rastreamento de front-end de RF entre os canais . Portanto, embora os algoritmos MCS realmente simplifiquem o processo de calibração de matriz, ainda há uma necessidade de se submeter a uma rotina de calibração em nível de sistema para alinhar as fases de cada canal de RF dentro do sistema.

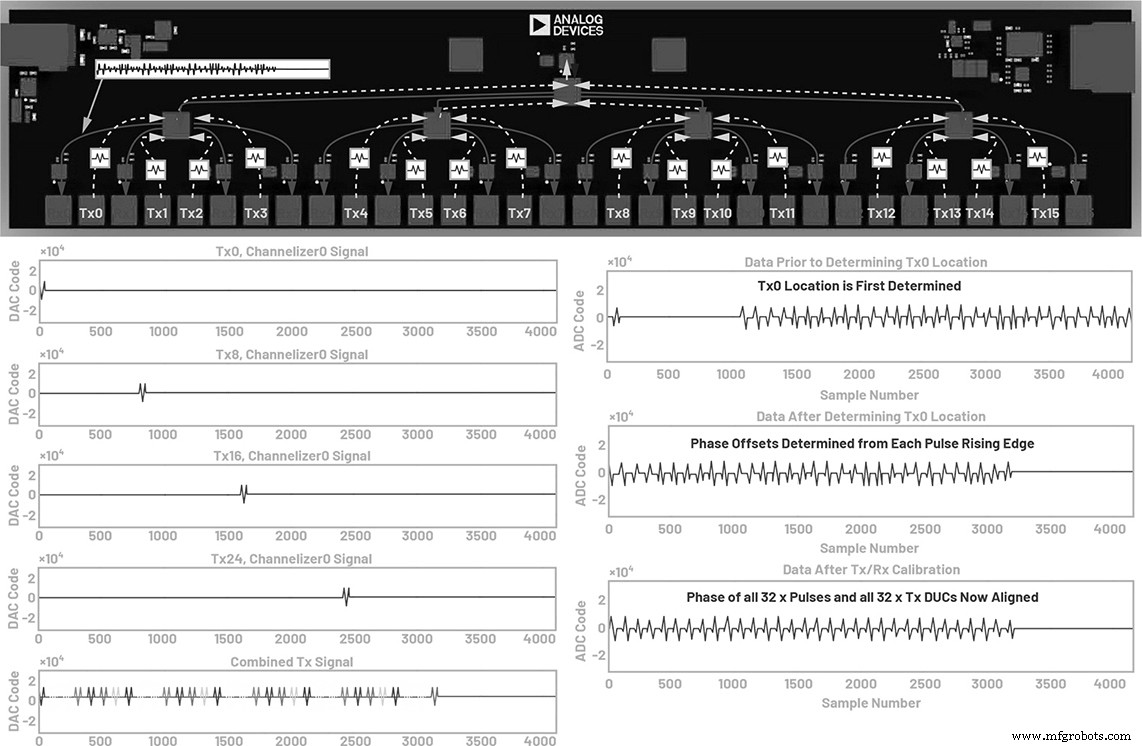

Portanto, é necessário desenvolver um algoritmo de calibração eficiente em nível de sistema, além de realizar os algoritmos MCS. O método de calibração em nível de sistema para este artigo utiliza uma forma de onda de banda base específica e é totalmente independente, sem a necessidade de qualquer equipamento externo. O sistema descrito neste artigo é capaz de injetar formas de onda de banda base separadas em cada canalizador na plataforma. Utilizando esse recurso, uma forma de onda de banda base que consiste em um pulso de um período para cada canalizador de transmissão é injetada no subarray, conforme mostrado na parte inferior esquerda da Figura 5. Cada canalizador de transmissão, portanto, emite apenas um pulso. No entanto, as formas de onda são escalonadas em todos os canalizadores de transmissão, de modo que apenas um pulso de um período é emitido por vez em todo o sistema. A saída de todos os canalizadores de transmissão é combinada dentro do domínio de RF e então dividida e enviada de volta para todos os canais de recepção, como mostrado no topo da Figura 5. Finalmente, uma captura de dados de recepção simultânea é realizada para todos os canais de recepção e os dados são salvos para uma matriz de 4096 × 16, onde 4096 é o tamanho da amostra coletada para todos os 16 canais de recepção.

clique para ver a imagem em tamanho real

Figura 5. Um algoritmo de calibração de nível de sistema é usado em conjunto com MCS para atingir rapidamente o alinhamento de todos os canais de recepção e transmissão no sistema. (Fonte:Dispositivos analógicos)

Esses dados são então analisados verticalmente ao longo da primeira coluna (correspondendo a Rx0) para localizar o pulso do canalizador Tx0, como é mostrado no subplot superior no canto inferior direito da Figura 5. Após o pulso Tx0 ser identificado, todos os outros locais de pulso são conhecidos e a fase complexa da borda ascendente de cada pulso é calculada e salva em um vetor 1 × 16 que corresponde aos deslocamentos de fase medidos presentes em todos os canais de transmissão em todo o sistema. Com esse conhecimento, e usando Tx0 como referência de linha de base, as fases complexas de todos os canais de transmissão são então modificadas com base nos deslocamentos medidos.

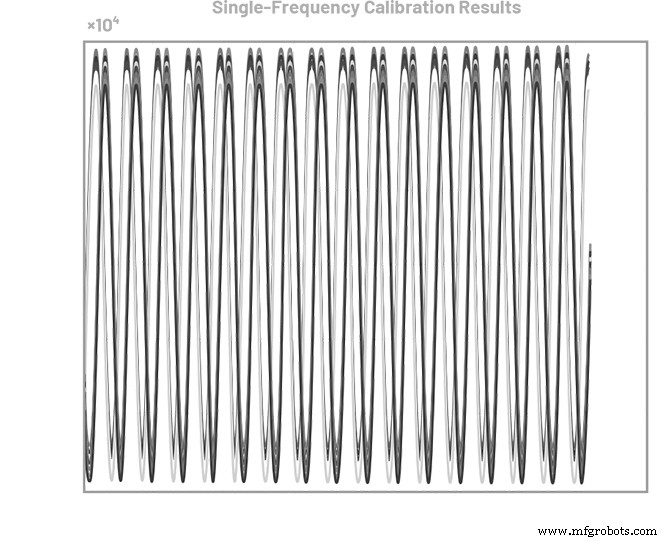

Da mesma forma, uma vez que o mesmo sinal combinado está sendo enviado para todos os canais de recepção, os dados são então analisados horizontalmente ao longo da matriz (olhando através de todos os canais de recepção). As fases complexas de todos os canais de recepção são então medidas em relação a Rx0 e salvas em um vetor 1 × 16 correspondente aos deslocamentos de fase de recepção medidos presentes no sistema. As fases do complexo NCO de recepção são então ajustadas em todo o submatriz para alinhar todos os canais em relação a Rx0, como é mostrado pelos códigos ADC em fase (I) e fase em quadratura (Q) para todos os 16 canais de recepção na Figura 6. Pode-se notar que, embora o gráfico na fase da Figura 6 alinhe todos os canais, não necessariamente alinha em amplitude todos os canais. No entanto, usando os filtros de resposta de impulso finito (FIR) no chip agora presentes nesses CIs digitalizadores, pode-se, alternativamente, alcançar o alinhamento de amplitude e fase entre os canais sem a necessidade de alocar recursos de FPGA que consomem muita energia para obter o mesmo resultado.

clique para ver a imagem em tamanho real

Figura 6. O alinhamento de fase I&Q de recepção de 16 canais é obtido com o auxílio de MCS e um algoritmo de calibração de nível de sistema independente. (Fonte:Dispositivos analógicos)

Este algoritmo de calibração em nível de sistema é atualmente obtido em MATLAB

®

e leva aproximadamente três segundos para ser concluído. No entanto, se implementado em linguagem de descrição de hardware (HDL), este tempo de calibração pode ser reduzido ainda mais, mantendo um algoritmo completamente autocontido. Além disso, ao confiar nos algoritmos MCS, se a frequência e amplitude do sistema forem conhecidas na inicialização, os usuários podem carregar os valores de deslocamento de fase de uma tabela de pesquisa em vez de precisar passar pelas medições descritas neste método de calibração em nível de sistema. Nesse caso, o método de calibração em nível de sistema pode ser usado para preencher os deslocamentos de fase salvos em uma tabela de pesquisa durante uma calibração de fábrica.

Conclusão

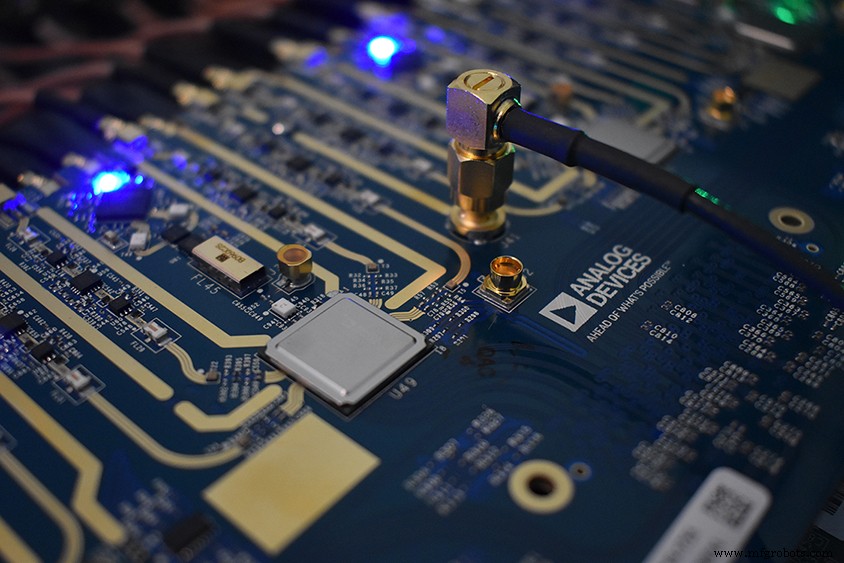

Um processo de MCS bem-sucedido foi demonstrado usando quatro CIs AD9081 MxFETM da Analog Devices como a espinha dorsal do subarray. Gradientes térmicos na plataforma são compensados com a ajuda de blocos de ajuste de fase em quatro sintetizadores PLL ADF4371. Um IC de relógio HMC7043 é usado para distribuir os SYSREFs e os relógios BBP necessários para a interface JESD204C. Os algoritmos MCS dentro do AD9081 permitem calibrações simplificadas no nível do sistema e fornecem fase determinística de energização para múltiplas frequências e gradientes térmicos presentes no sistema. Um algoritmo de calibração de nível de sistema eficiente também é apresentado, usado para preencher LUTs durante a calibração de fábrica e, portanto, reduz drasticamente o tempo de inicialização do sistema. Essa plataforma é mostrada na Figura 7 e é chamada de Quad-MxFE. O sistema está disponível para compra na Analog Devices. Este trabalho é pertinente a qualquer sistema multicanal presente em qualquer radar phased array, guerra eletrônica, instrumentação ou plataforma 5G.

Figura 7. A plataforma Quad-MxFE está disponível para compra na Analog Devices. (Fonte:Dispositivos analógicos)

Referências

1 Del Jones. “JESD204C Primer:O que há de novo e para você - Parte 1.” Diálogo analógico , Vol. 53, No. 2, junho de 2019.

2 Del Jones. “JESD204C Primer:O que há de novo e para você - Parte 2.” Diálogo analógico , Vol. 53, No. 3, julho de 2019.

Integrado

- 3 motivos pelos quais DevOps e nuvem precisam um do outro; DevCloudOps

- Vetores e formas de onda CA

- Medição de frequência e fase

- Estruturas e classes em C ++

- Caixas de correio:introdução e serviços básicos

- Semáforos:introdução e serviços básicos

- Filas:introdução e serviços básicos

- Vídeo imersivo, IA e Tech Shaping Varejo Fase seguinte

- Torneamento duro e retificação cilíndrica foram feitos um para o outro

- Tipos comuns de fresadoras e quando usar cada uma