Compreendendo a taxa de erro do código ADC

Conforme os conversores analógico-digital (ADCs) de alta velocidade aumentaram na taxa de amostragem, também aumentou o problema de erros de código - também conhecidos como códigos sparkle - nos dados de saída do ADC. Um erro de código é definido como um erro no código de saída de um ADC que excede um limite definido. O limite é mais comumente definido como o nível em que um erro excede a amplitude esperada do ruído do ADC, de modo que o erro pode ser facilmente identificado na presença de ruído.

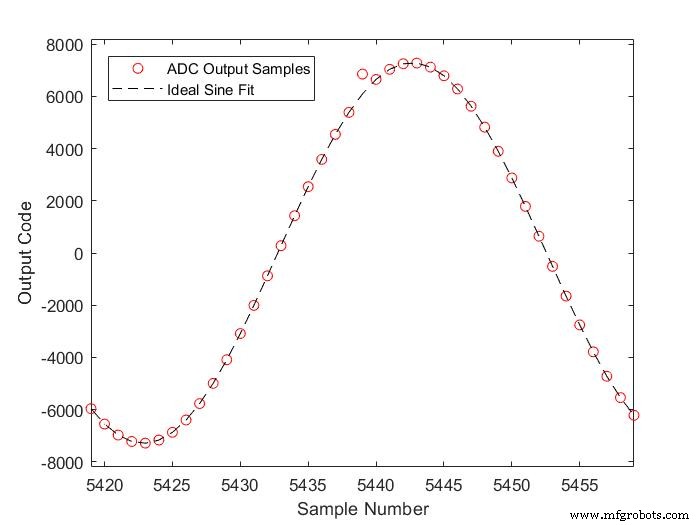

Outra maneira de explicar esta definição do limite de erro é que a amplitude do erro ocorre com uma probabilidade que excede a probabilidade esperada dessa amplitude, dado o ruído distribuído gaussiano assumido do ADC. Fig. 1 mostra um exemplo de erro de código encontrado nas amostras de saída de um ADC. A amostra errônea é claramente visível quando comparada ao ajuste de onda senoidal ideal e excede em muito o ruído das outras amostras no gráfico.

Fig. 1:Exemplo de uma saída ADC com um erro de código.

A taxa de erro de código (CER) de um ADC, também às vezes chamada de taxa de erro de palavra (WER) ou taxa de erro de metaestabilidade, é definida como o número médio de erros por amostra e é medida pela contagem do número médio de amostras entre erros consecutivos. É mais frequentemente definido como uma ordem de magnitude, como 10

–12

erros / amostra. O tempo médio entre erros, portanto, depende da taxa de amostragem do conversor. O CER medido é preciso apenas quando o ADC está funcionando na taxa de amostragem em que o CER foi medido. Em geral, reduzir a taxa de amostragem pode melhorar o CER em ordens de magnitude.

Vamos dar uma olhada na origem dos erros de código para ver por que a taxa de amostragem é um fator importante.

O que faz um ADC brilhar?

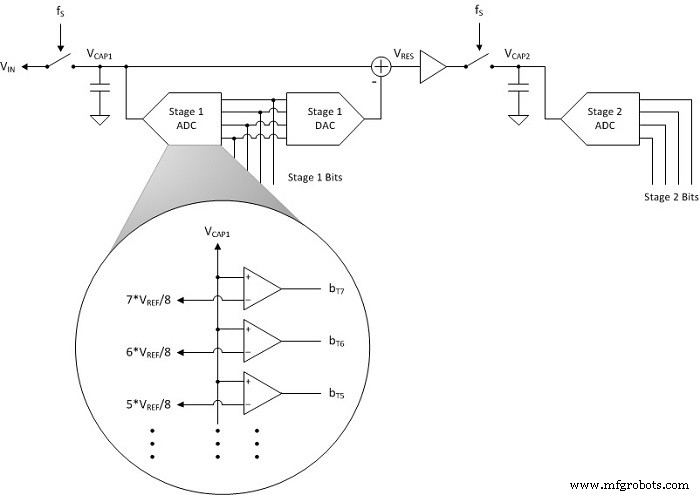

Uma arquitetura de ADC de várias etapas, como um ADC de flash em pipeline ou um ADC de registro de aproximação sucessiva (SAR), converte a tensão amostrada em bits digitais em estágios, e cada estágio consecutivo depende do resultado do estágio anterior. Considere um ADC básico de flash pipeline de alta velocidade, conforme mostrado na Fig. 2 . Este ADC simplificado mostra dois estágios de conversão em que cada estágio sucessivo produz um código digital que estima com mais precisão o sinal de entrada.

A operação do ADC mostrado é a seguinte:

-

O primeiro estágio mostra a tensão de entrada e converte grosseiramente o sinal de entrada analógico em um código digital usando o ADC de primeiro estágio. O flash ADC neste estágio funciona comparando a voltagem amostrada contra referências de voltagem estática, geradas a partir da voltagem de referência principal do ADC (V REF ), usando comparadores de alta velocidade. A saída dos comparadores de flash é uma amostra digital codificada por termômetro que representa a tensão de entrada.

-

O código do termômetro convertido é então enviado diretamente para o DAC de primeiro estágio. Este DAC emite a tensão analógica, que corresponde à amostra convertida grosseiramente.

-

Subtrair a saída do DAC de primeiro estágio da tensão de entrada original resulta na tensão de erro de quantização ou tensão residual (V RES ) O resíduo é então amplificado e reamostrado (pipeline) para o segundo estágio.

-

O ADC de segundo estágio quantiza V RES para obter uma estimativa mais precisa (resolução mais alta) da tensão de entrada analógica original.

Fig. 2:Exemplo de um diagrama de blocos de arquitetura de ADC flash em pipeline.

The V RES processo de criação apresenta um ciclo de decisão de alta velocidade. Dentro de um período de amostragem de relógio, a voltagem amostrada deve ser convertida em um código digital pelo ADC de primeiro estágio. O código digital deve ser emitido do DAC de primeiro estágio, subtraído da tensão de entrada original e reamostrado pelo segundo estágio. O loop de decisão de alta velocidade introduz erros de código porque o comparador no flash ADC tem um tempo de estabilização que é uma função da diferença entre a tensão amostrada e V REF .

Mais simplesmente, um comparador leva mais tempo para se estabelecer quando a tensão de entrada (V CAP1 ) está perto da tensão de referência (como 7 * V REF / 8) do comparador. Teoricamente, se V CAP1 está infinitesimalmente perto da tensão de referência do comparador, o comparador nunca se estabilizará porque estará operando em sua região linear.

O ruído impedirá que isso realmente ocorra, mas se o comparador demorar muito para se estabilizar, o DAC de primeiro estágio pode usar o código digital incorreto para emitir a tensão analógica quantizada. O resultado é um V RES que não corresponde ao código de saída digital real do ADC de primeiro estágio. O ADC de segundo estágio então converte o V RES errado , o que resulta em um erro de código.

O que afeta o CER?

Agora você deve ter detalhes suficientes para poder tirar algumas conclusões sobre o que afeta o CER. O CER depende claramente da taxa de amostragem. Uma taxa de amostragem mais rápida reduz o tempo em que o ciclo de decisão deve tomar uma decisão. Menos tempo para tomar uma decisão resulta em aumentos exponenciais na probabilidade de o comparador não ter se estabelecido a tempo.

–Matt Guibord é engenheiro de sistemas em conversores de alta velocidade na Texas Instruments.

Integrado