Design integrado com FPGAs:Recursos de hardware

Nota do editor:à medida que algoritmos avançados continuam a emergir para designs de produtos inteligentes, os desenvolvedores muitas vezes se encontram lutando para implementar sistemas incorporados capazes de atender às demandas de processamento associadas a esses algoritmos. FPGAs podem fornecer o desempenho necessário, mas projetar com FPGAs há muito tempo é considerado limitado ao alcance de especialistas em programação de FPGAs. Hoje, entretanto, a disponibilidade de FPGAs mais poderosos e ambientes de desenvolvimento mais eficazes tornou o desenvolvimento de FPGAs amplamente acessível. Neste trecho, Capítulo 4 do livro Architecting High-Performance Embedded Systems, o autor oferece uma revisão abrangente de dispositivos FPGA, linguagens de implementação e o processo de desenvolvimento de FPGA, bem como um passo a passo detalhado de como começar a implementar FPGAs por conta própria Projeto. O trecho completo é apresentado na seguinte série de parcelas:

Nota do editor:à medida que algoritmos avançados continuam a emergir para designs de produtos inteligentes, os desenvolvedores muitas vezes se encontram lutando para implementar sistemas incorporados capazes de atender às demandas de processamento associadas a esses algoritmos. FPGAs podem fornecer o desempenho necessário, mas projetar com FPGAs há muito tempo é considerado limitado ao alcance de especialistas em programação de FPGAs. Hoje, entretanto, a disponibilidade de FPGAs mais poderosos e ambientes de desenvolvimento mais eficazes tornou o desenvolvimento de FPGAs amplamente acessível. Neste trecho, Capítulo 4 do livro Architecting High-Performance Embedded Systems, o autor oferece uma revisão abrangente de dispositivos FPGA, linguagens de implementação e o processo de desenvolvimento de FPGA, bem como um passo a passo detalhado de como começar a implementar FPGAs por conta própria Projeto. O trecho completo é apresentado na seguinte série de parcelas: 1:Recursos de hardware (este artigo)

2:Linguagens de implementação

3:Processo de desenvolvimento

4:Construindo um projeto

5:Implementação

Adaptado de Architecting High-Performance Embedded Systems, de Jim Ledin.

Desenvolvendo seu primeiro programa FPGA

Este capítulo começa com uma discussão sobre o uso eficaz de dispositivos FPGA em sistemas embarcados de tempo real e continua com uma descrição dos elementos funcionais contidos em FPGAs padrão. A variedade de linguagens de design FPGA, incluindo Hardware Linguagens de descrição ( HDLs ), métodos de diagrama de blocos e linguagens de programação de software populares, incluindo C e C ++, são apresentados. O capítulo continua com uma visão geral do processo de desenvolvimento de FPGA e conclui com um exemplo completo de um ciclo de desenvolvimento de FPGA começando com uma declaração de requisitos do sistema e terminando com um sistema funcional implementado em uma placa de desenvolvimento de FPGA de baixo custo.

Depois de concluir este capítulo, você saberá como os FPGAs podem ser aplicados em arquiteturas de sistemas embarcados em tempo real e entenderá os componentes que constituem um circuito integrado FPGA. Você terá aprendido sobre as linguagens de programação usadas no projeto de algoritmos FPGA e compreenderá a sequência de etapas para desenvolver um aplicativo baseado em FPGA. Você também terá trabalhado em um exemplo completo de desenvolvimento de FPGA em uma placa de desenvolvimento de baixo custo usando ferramentas de software FPGA gratuitas.

Cobriremos os seguintes tópicos neste capítulo:

- Usando FPGAs em projetos de sistemas embarcados em tempo real

- linguagens de implementação FPGA

- O processo de desenvolvimento FPGA

- Desenvolvendo seu primeiro projeto FPGA

Requisitos técnicos

Os arquivos deste capítulo estão disponíveis em https://github.com/PacktPublishing/Architecting-High-Performance-Embedded-Systems.

Usando FPGAs em projetos de sistemas embarcados em tempo real

Como vimos nos Elementos de FPGAs seção do Capítulo 1 , Arquitetura de alto desempenho Sistemas Embarcados , um dispositivo FPGA típico contém um grande número de tabelas de pesquisa, flip-flops, elementos de bloco de RAM, fatias de DSP e outros componentes. Embora possa ser instrutivo entender os recursos detalhados de cada um desses componentes, tais preocupações não são necessariamente informativas durante o processo de desenvolvimento do FPGA. A restrição mais importante a se ter em mente é que um número de peça específico do FPGA contém um número finito de cada um desses elementos, e um projeto não pode exceder esses limites quando direcionado a esse modelo específico de FPGA.

Em vez disso, é mais produtivo ver o processo de desenvolvimento do FPGA da perspectiva da declaração de requisitos do sistema embarcado. Você pode começar a desenvolver o design do FPGA direcionado a um modelo de FPGA escolhido de forma arbitrária. À medida que o desenvolvimento prossegue, você pode atingir um limite de recursos ou identificar um recurso FPGA que o projeto exige e que não está presente no FPGA almejado atualmente. Nesse ponto, você pode selecionar um alvo diferente e mais capaz e continuar o desenvolvimento.

Alternativamente, conforme o desenvolvimento do design se aproxima da conclusão, você pode perceber que o FPGA alvo que você selecionou originalmente contém recursos excessivos e o design pode ser melhorado selecionando um FPGA menor, com benefícios potenciais em termos de custo menor, menos pinos, tamanho de pacote menor, e consumo de energia reduzido.

Em qualquer uma dessas situações, geralmente é simples mudar o FPGA de destino para um modelo diferente dentro da mesma família. As ferramentas de desenvolvimento e artefatos de design que você criou até agora devem ser totalmente reutilizáveis com o modelo FPGA recém-direcionado. Se for necessário mudar para uma família diferente de FPGAs do mesmo fornecedor, ou para um modelo de um fornecedor diferente, a transição provavelmente envolverá mais trabalho.

O objetivo desta discussão é enfatizar que não é muito importante identificar um modelo específico de FPGA no início de um esforço de desenvolvimento de sistema embarcado de alto desempenho. Em vez disso, as primeiras considerações devem se concentrar na validação da decisão de usar um FPGA como parte do projeto, então, se o FPGA for a melhor abordagem de projeto, prossiga com a seleção de um fornecedor de FPGA e família de dispositivos adequados.

Projetos de exemplo neste livro serão baseados na família Xilinx Vivado de ferramentas de desenvolvimento FPGA. Embora uma licença Vivado deva ser adquirida para desenvolver algumas famílias Xilinx FPGA, os dispositivos FPGA no Artix-7 com os quais estaremos trabalhando são suportados pela Vivado gratuitamente. A família Artix-7 FPGA combina os atributos de alto desempenho, baixo consumo de energia e custo total do sistema reduzido. Famílias de dispositivos FPGA semelhantes e conjuntos de ferramentas de desenvolvimento estão disponíveis em outros fornecedores de FPGA.

O desenvolvimento de FPGA é um processo bastante complexo, com uma variedade de tipos de entrada de dados de projeto e análise necessários. Para evitar discutir esses tópicos em um nível muito abstrato e apresentar resultados concretos em termos de projetos de exemplo de trabalho, usaremos o Vivado ao longo do livro. Assim que estiver familiarizado com as ferramentas e técnicas discutidas aqui, você poderá aplicá-las usando ferramentas semelhantes de outros fornecedores.

As seções a seguir irão discutir alguns dos principais recursos de diferenciação das famílias de FPGAs e modelos individuais dentro dessas famílias, incluindo a quantidade de bloco de RAM, a quantidade e os tipos de sinais de I / O disponíveis, recursos de hardware on-chip especializados e a inclusão de um ou mais núcleos de processador de hardware no pacote FPGA.

Bloco de RAM e RAM distribuída

Bloco RAM é usado para implementar regiões de memória em um FPGA. Uma região de memória particular é especificada em termos de largura em bits (normalmente 8 ou 16 bits) e a profundidade, que define o número de locais de armazenamento na região de memória.

A quantidade total de bloco de RAM em um FPGA é geralmente especificada em termos de kilobits ( Kb ) A quantidade de bloco de RAM disponível varia entre as famílias FPGA e entre os modelos de uma determinada família. Como seria de se esperar, peças maiores e mais caras geralmente têm uma quantidade maior de recursos que podem ser usados como bloco de RAM.

Em Xilinx FPGAs, e em vários graus em FPGAs de outros fornecedores, uma categoria distinta de memória chamada RAM distribuída está disponível além do bloco de RAM. RAM distribuída é construído a partir dos elementos lógicos usados nas tabelas de pesquisa e reaproveita os circuitos desses dispositivos para formar pequenos segmentos de RAM, cada um contendo 16 bits. Esses segmentos podem ser agregados para formar blocos de memória maiores quando necessário.

O bloco de RAM tende a ser usado para fins tradicionalmente associados à RAM, como a implementação de memória cache do processador ou como buffer de armazenamento para dados de E / S. A RAM distribuída pode ser usada para fins como o armazenamento temporário de resultados de computação intermediários. Como a RAM distribuída é baseada em circuitos de tabela de pesquisa, o uso de RAM distribuída em um projeto reduz os recursos disponíveis para implementar operações lógicas.

O bloco de RAM pode ter uma ou duas portas. O bloco de RAM de porta única representa o padrão de uso comum de um processador que lê e grava RAM durante a operação.

A RAM de bloco de porta dupla fornece duas portas de leitura / gravação, ambas podendo ler ou gravar ativamente a mesma região de memória simultaneamente.

A RAM de bloco de porta dupla é ideal para situações em que os dados estão sendo transferidos entre partes de um FPGA rodando em velocidades de clock diferentes. Por exemplo, um subsistema de E / S pode ter uma velocidade de clock na casa das centenas de MHz ao receber um fluxo de dados de entrada. O subsistema de E / S grava os dados de entrada no bloco de RAM conforme eles chegam por meio de um dos canais de E / S de alta velocidade do FPGA. Um subsistema separado dentro do FPGA, rodando em uma velocidade de clock diferente, pode ler dados da segunda porta do bloco de RAM sem interferir com a operação do subsistema de E / S.

Bloco de RAM também pode operar em primeiro a entrar, primeiro a sair ( FIFO ) modo. No exemplo do fluxo de dados seriais de entrada, o subsistema de E / S pode inserir palavras de dados no FIFO conforme elas chegam e o subsistema de processamento pode lê-las na mesma ordem. O bloco RAM no modo FIFO fornece sinais indicando se o FIFO está cheio, vazio, quase cheio ou quase vazio. As definições de quase completo e quase vazio são responsabilidade do projetista do sistema. Se você atribuir quase vazio para significar que menos de 16 itens são deixados no FIFO, você pode ter certeza de que sempre que o FIFO não indicar que está quase vazio, você pode ler 16 itens sem mais verificações de disponibilidade de dados.

Ao usar o bloco RAM no modo FIFO, é vital que a lógica de inserção de itens no FIFO nunca tente escrever quando o FIFO está cheio, e a leitura lógica do FIFO nunca tente ler quando o FIFO está vazio. Se algum desses eventos ocorrer, o sistema perderá dados ou tentará processar dados indefinidos.

Pinos de E / S FPGA e recursos associados

Como os FPGAs são destinados ao uso em aplicativos de alto desempenho, seus pinos de E / S geralmente são capazes de implementar uma variedade de padrões de E / S de alta velocidade. Durante a implementação de um projeto com um conjunto de ferramentas de desenvolvimento FPGA, o desenvolvedor do sistema deve executar tarefas que incluem a atribuição de funções a pinos específicos no pacote FPGA e a configuração de cada um desses pinos para operar com o padrão de interface apropriado. Etapas adicionais devem ser executadas para associar os sinais de entrada e saída dentro do código do modelo FPGA com os pinos de pacote corretos.

No nível do pino, os sinais de E / S individuais são de terminação única ou diferenciais.

Um sinal de terminação única é referenciado ao solo. Lógica Transistor-Transistor Tradicional ( TTL ) e Semicondutor de óxido de metal complementar ( CMOS ) sinais digitais operam em uma faixa de 0-5 VCC em relação ao aterramento.

FPGAs modernos normalmente não suportam a faixa de sinal legado de 5 VCC, mas, em vez disso, suportam sinais TTL e CMOS operando em uma faixa de tensão reduzida, reduzindo assim o consumo de energia e melhorando a velocidade. TTL de baixa tensão ( LVTTL ) sinais operam em uma faixa de 0-3,3 VCC. CMOS de baixa tensão ( LVCMOS ) os sinais são selecionáveis com tensões de sinalização de 1,2, 1,5, 1,8, 2,5 e 3,3 V. Esses tipos de sinais são denominados LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25 e LVCMOS33. Outros tipos de sinal de terminação única de alto desempenho estão disponíveis, incluindo Lógica do transceptor de alta velocidade ( HSTL ) e Lógica Terminada Stub-Series ( SSTL )

Sinais de terminação única são amplamente usados para fins de baixa frequência, como leitura de entradas de botões e LEDs de iluminação. Sinais de terminação única também são usados em muitos protocolos de comunicação de baixa velocidade, como I2C e SPI. Uma desvantagem importante dos sinais de terminação única é que qualquer ruído acoplado aos fios e aos traços da placa de circuito impresso que transportam o sinal tem o potencial de corromper a entrada para o receptor. Este problema pode ser substancialmente reduzido com o uso de sinalização diferencial.

Para as taxas de transferência de dados mais altas, a sinalização diferencial é a abordagem preferida.

Sinais diferenciais use um par de pinos de E / S e direcione sinais opostos aos dois pinos.

Em outras palavras, um pino é conduzido para uma tensão mais alta e o outro pino para uma tensão mais baixa para representar um bit de dados 0 e as tensões dos pinos são invertidas para representar um bit 1. O receptor diferencial subtrai os dois sinais para determinar se o bit de dados é 0 ou 1. Como os dois fios ou traços que transportam o sinal diferencial estão fisicamente localizados muito próximos, qualquer ruído que acoplar em um dos sinais se acoplará ao outro de uma maneira muito semelhante. A operação de subtração remove a grande maioria do ruído, permitindo uma operação confiável em taxas de transferência de dados muito mais altas do que os sinais de terminação única.

Vários padrões de sinais diferenciais são suportados por FPGAs padrão. Várias versões diferenciais de HSTL e SSTL são definidas, com uma variedade de níveis de tensão de sinalização para cada uma.

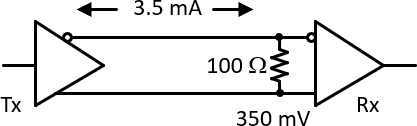

Sinalização diferencial de baixa tensão ( LVDS ) foi introduzido como padrão em 1994 e continua a ser usado em uma variedade de aplicações. Um transmissor de sinalização LVDS produz uma corrente constante de 3,5 mA e muda a direção da corrente que flui através do resistor no receptor para produzir mudanças de estado representando os valores de dados 0 e 1, conforme mostrado na Figura 4.1 :

Figura 4.1 - Interface LVDS

Na comunicação LVDS, como nos outros padrões de sinalização diferencial e de terminação única, é importante que a impedância do caminho de comunicação entre o transmissor e o receptor corresponda de perto à impedância de terminação, que é de 100 ohms no caso do LVDS. Se a impedância do canal de comunicação não corresponder à impedância da terminação, podem ocorrer reflexos na linha, impedindo a recepção confiável dos dados.

A impedância dos pares de traços de sinal diferencial é uma função da geometria dos traços de par e de sua relação com o plano de aterramento. Como veremos no Capítulo 6 , Projetando circuitos com KiCad , é simples projetar placas de circuito que satisfaçam os requisitos dos padrões de sinalização diferencial de alta velocidade.

Recursos de hardware especializados

Os FPGAs geralmente incluem uma seleção de recursos de hardware dedicados para funções que são comumente exigidas e são implementadas de forma mais eficiente no hardware em vez de usar funções FPGA sintetizadas ou impossíveis de implementar com componentes FPGA. Alguns exemplos desses recursos são os seguintes:

- Interfaces para RAM dinâmica externa ( DRAM ) para armazenar grandes quantidades de Essas interfaces geralmente suportam um padrão DRAM comum, como DDR3.

- Conversores analógico para digital.

- Loops de bloqueio de fase, usados para gerar várias frequências de relógio.

- Processamento de sinal digital multiplica-acumula ( MAC ) hardware.

Esses recursos de hardware permitem o desenvolvimento de sistemas complexos com recursos abrangentes. Hardware dedicado é fornecido para funções como a operação MAC porque o desempenho do hardware é significativamente melhor do que a funcionalidade equivalente sintetizada usando recursos lógicos FPGA.

Núcleos do processador

Algumas famílias de FPGAs incluem núcleos de processador de hardware com o objetivo de combinar a velocidade máxima de execução do software com as vantagens de desempenho dos algoritmos implementados em FPGA. Por exemplo, a família Xilinx Zynq-7000 integra um processador de hardware ARM Cortex-A9 junto com um tecido FPGA tradicional.

Projetos FPGA que não requerem um processador de hardware podem implementar um processador usando os recursos FPGA, referido como um processador soft . Os processadores soft são altamente configuráveis, embora geralmente não sejam capazes de corresponder ao desempenho de um processador implementado no hardware.

A próxima seção irá apresentar as principais linguagens de programação e métodos de entrada de dados usados para desenvolver algoritmos FPGA.

Reimpresso com permissão da Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin é o CEO da Ledin Engineering, Inc. Jim é um especialista em software embarcado e design, desenvolvimento e teste de hardware. Ele também tem experiência em avaliação de segurança cibernética de sistemas embarcados e testes de penetração. Ele tem um B.S. formado em engenharia aeroespacial pela Iowa State University e um M.S. graduado em engenharia elétrica e da computação pelo Georgia Institute of Technology. Jim é um engenheiro elétrico profissional registrado na Califórnia, um Certified Information System Security Professional (CISSP), um Certified Ethical Hacker (CEH) e um Certified Penetration Tester (CPT).

Jim Ledin é o CEO da Ledin Engineering, Inc. Jim é um especialista em software embarcado e design, desenvolvimento e teste de hardware. Ele também tem experiência em avaliação de segurança cibernética de sistemas embarcados e testes de penetração. Ele tem um B.S. formado em engenharia aeroespacial pela Iowa State University e um M.S. graduado em engenharia elétrica e da computação pelo Georgia Institute of Technology. Jim é um engenheiro elétrico profissional registrado na Califórnia, um Certified Information System Security Professional (CISSP), um Certified Ethical Hacker (CEH) e um Certified Penetration Tester (CPT). Conteúdos Relacionados:

- Ferramentas de código aberto ajudam a simplificar a programação FPGA

- Implementação de algoritmos de ponto flutuante em FPGAs ou ASICs

- Aproveitando FPGAs para aprendizagem profunda

- Ferramentas de software migram código GPU para FPGAs para aplicativos de IA

- FPGAs substituem ASICs em ADAS baseado em visão Subaru Eyesight

- Como os FPGAs baseados em flash simplificam os requisitos de segurança funcional

- Aproveitando os benefícios dos FPGAs instantâneos

- Configuração FPGA usando flash NOR de alta velocidade

- Como a tecnologia FPGA está evoluindo para atender aos novos requisitos de sistema de médio porte

Para obter mais informações sobre o Embedded, assine o boletim informativo semanal da Embedded por e-mail.

Integrado

- Como evitar surpresas dispendiosas no design de hardware conectado

- O que é design de sistema incorporado:etapas no processo de design

- Simplificando o desenvolvimento de IoT com Eclipse IoT

- Desenvolvimento de máquinas de estado com desenvolvimento orientado a testes

- Transformando big data em dados inteligentes com IA incorporado

- Cypress:ModusToolbox Suite facilita a complexidade do design de IoT

- Lattice:MachX03D FPGA aumenta a segurança com recursos de raiz de confiança de hardware

- O kit de design mede a pressão arterial com sensor óptico

- Java 9 - Melhoria do Try With Resources

- All in com aditivo