The D Latch

Uma vez que a entrada de habilitação em uma trava SR fornece uma maneira de travar as saídas Q e não-Q sem levar em conta o status de S ou R, podemos eliminar uma dessas entradas para criar um circuito de trava multivibrador sem entrada "ilegal" estados.

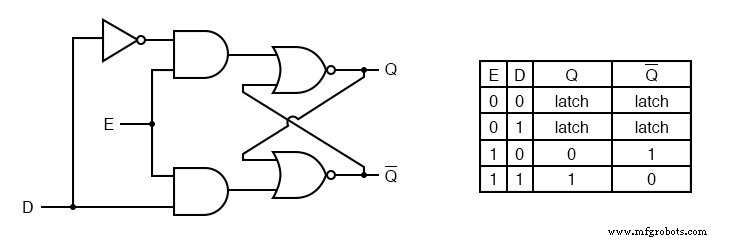

Esse circuito é chamado de trava D, e sua lógica interna se parece com esta:

Observe que a entrada R foi substituída pelo complemento (inversão) da antiga entrada S, e a entrada S foi renomeada para D. Como com a trava SR fechada, a trava D não responderá a uma entrada de sinal se habilitar a entrada é 0 - ela simplesmente permanece travada em seu último estado. Quando a entrada de habilitação é 1, entretanto, a saída Q segue a entrada D.

Como a entrada R do circuito S-R foi eliminada, essa trava não tem estado "inválido" ou "ilegal". Q e não-Q são sempre opostos um do outro.

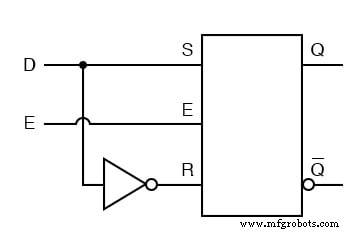

Se o diagrama acima for confuso, o próximo diagrama deve tornar o conceito mais simples:

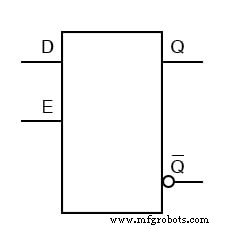

Como as travas S-R e S-R, o circuito de trava D pode ser encontrado como seu próprio circuito pré-embalado, completo com um símbolo padrão:

O latch D nada mais é do que um latch S-R com um inversor adicionado para tornar R o complemento (inverso) de S.

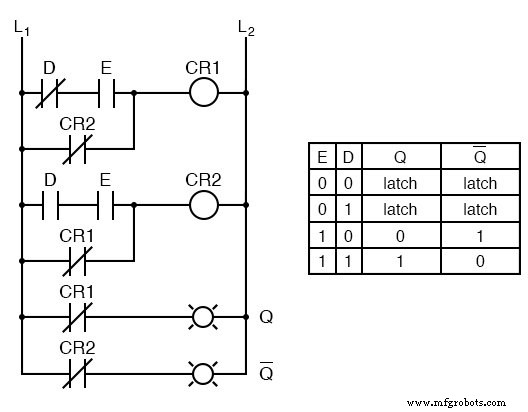

Vamos explorar a lógica ladder equivalente a uma trava D, modificada a partir do diagrama ladder básico de uma trava S-R:

Uma aplicação para a trava D é um circuito de memória de 1 bit. Você pode “gravar” (armazenar) um bit 0 ou 1 neste circuito de trava tornando a entrada de habilitação alta (1) e configurando D para o que você quiser que o bit armazenado seja. Quando a entrada de habilitação é baixa (0), a trava ignora o status da entrada D e alegremente mantém o valor do bit armazenado, emitindo no valor armazenado em Q e seu inverso na saída não-Q.

REVER:

- Uma trava D é como uma trava S-R com apenas uma entrada:a entrada “D”. A ativação da entrada D configura o circuito e a desativação da entrada D reinicializa o circuito. Obviamente, isso ocorre apenas se a entrada de habilitação (E) também estiver ativada. Caso contrário, a (s) saída (s) será (ão) travada (s), sem resposta ao estado da entrada D.

- As travas D podem ser usadas como circuitos de memória de 1 bit, armazenando um estado “alto” ou “baixo” quando desabilitadas e “lendo” novos dados da entrada D quando habilitadas.

PLANILHAS RELACIONADAS:

- Circuitos de trava - Planilha de trava D

Tecnologia industrial