Em suma, VHDL é uma linguagem de computador usada para projetar circuitos digitais. Eu uso o termo “linguagem de computador” para distinguir o VHDL de outras linguagens de programação mais comuns, como Java ou C++. Mas o VHDL é uma linguagem de programação? É sim. É uma linguagem de programação

Embora as ferramentas VHDL e FPGA sejam geralmente muito caras, é fácil acessar gratuitamente softwares de última geração se você for um estudante. Existem vários simuladores, editores e IDEs para trabalhar com VHDL. Este artigo mostra como instalar dois dos programas mais populares usados pelos e

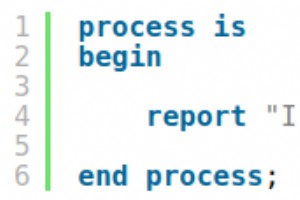

Ao aprender uma nova linguagem de programação, sempre gosto de começar aprendendo a imprimir. Quando você domina a saída de “Hello World!”, você sabe que o ambiente está funcionando. Ele também mostra o esqueleto básico da linguagem, o código mínimo necessário para produzir qualquer saída. Você po

No tutorial anterior, aprendemos que um processo pode ser pensado como um encadeamento de programa. Também aprendemos que um wait; instrução faz com que o programa seja pausado indefinidamente. Mas existe uma maneira de fazer um programa esperar por qualquer outro valor de tempo que não seja para se

No tutorial anterior, aprendemos como atrasar o tempo usando o wait for declaração. Também aprendemos sobre o loop de processo. Agora sabemos que, se permitirmos, o “thread” do processo entrará em loop dentro do processo para sempre. Mas e se quisermos fazer algo apenas uma vez no início do proces

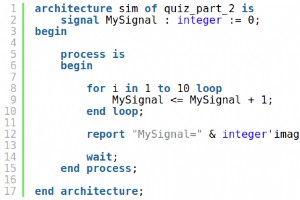

No tutorial anterior aprendemos a criar um loop infinito usando o loop declaração. Também aprendemos como sair de um loop usando o exit declaração. Mas e se quisermos que o loop seja repetido um certo número de vezes? O For-Loop é a maneira mais fácil de fazer isso. O For-Loop permite iterar em um

No tutorial anterior, aprendemos como usar um For-Loop para iterar em um intervalo de inteiros. Mas e se quisermos um controle mais detalhado do loop do que apenas um intervalo de inteiros fixo? Podemos usar um While-Loop para isso. O While-Loop continuará a iterar sobre o código incluído, desde q

Então você concluiu a primeira parte da série Basic VHDL Tutorial. Parabéns! Você está a apenas horas e horas e horas de se tornar um verdadeiro gênio do VHDL. Mas você completou o primeiro passo, e essa é a parte mais importante agora! Antes de prosseguirmos, você deve testar suas habilidades com

No tutorial anterior aprendemos como declarar uma variável em um processo. As variáveis são boas para criar algoritmos dentro de um processo, mas não são acessíveis ao mundo exterior. Se um escopo de uma variável está apenas dentro de um único processo, como ele pode interagir com qualquer outra l

No tutorial anterior aprendemos as principais diferenças entre sinais e variáveis. Aprendemos que os sinais têm um escopo mais amplo do que as variáveis, que só são acessíveis dentro de um processo. Então, como podemos usar sinais para comunicação entre vários processos? Já aprendemos a usar wait;

No tutorial anterior, usamos uma expressão condicional com a instrução Wait Until. A expressão garantiu que o processo só fosse acionado quando os dois sinais do contador fossem iguais. Mas e se quiséssemos que o programa em um processo tomasse ações diferentes com base em entradas diferentes? As

Você deve sempre usar uma lista de sensibilidade para acionar processos em módulos de produção. As listas de sensibilidade são parâmetros para um processo que lista todos os sinais aos quais o processo é sensível. Se algum dos sinais mudar, o processo será ativado e o código dentro dele será executa

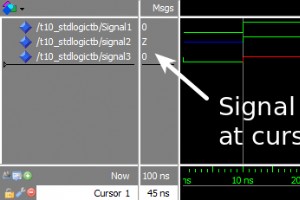

O tipo mais comum usado em VHDL é o std_logic . Pense nesse tipo como um único bit, a informação digital transportada por um único fio físico. O std_logic nos dá um controle mais refinado sobre os recursos em nosso design do que o integer type, que temos usado nos tutoriais anteriores. Normalmente

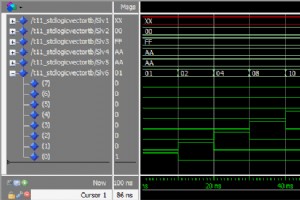

O std_logic_vector tipo pode ser usado para criar barramentos de sinal em VHDL. O std_logic é o tipo mais comumente usado em VHDL, e o std_logic_vector é a versão de matriz dele. Enquanto o std_logic é ótimo para modelar o valor que pode ser carregado por um único fio, não é muito prático para imp

Teste suas habilidades de codificação com este quiz VHDL depois de concluir os tutoriais 6-11 da série Basic VHDL Tutorial! Se você leu as postagens do blog, assistiu aos vídeos e fez os exercícios, deve estar qualificado para responder à maioria das perguntas do questionário. O quiz é intencional

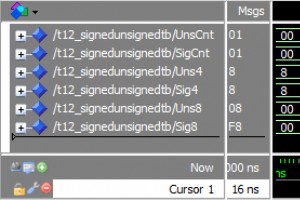

Os tipos assinados e não assinados em VHDL são vetores de bits, assim como o tipo std_logic_vector. A diferença é que, embora o std_logic_vector seja ótimo para implementar barramentos de dados, é inútil para realizar operações aritméticas. Se você tentar adicionar qualquer número a um tipo std_lo

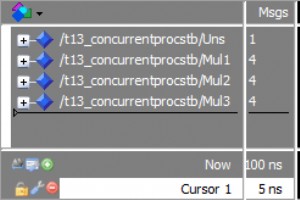

Uma instrução concorrente em VHDL é uma atribuição de sinal dentro da arquitetura, mas fora de uma construção de processo normal. A instrução concorrente também é chamada de atribuição concorrente ou processo concorrente. Quando você cria uma declaração concorrente, na verdade você está criando um

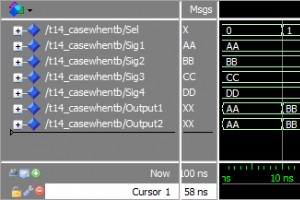

A instrução Case-When fará com que o programa pegue um dentre vários caminhos diferentes, dependendo do valor de um sinal, variável ou expressão. É uma alternativa mais elegante para uma instrução If-Then-Elsif-Else com vários Elsifs. Outras linguagens de programação têm construções semelhantes, u

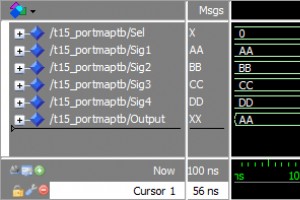

Um módulo é uma unidade independente de código VHDL. Os módulos se comunicam com o mundo exterior por meio da entidade . Mapa do porto é a parte da instanciação do módulo onde você declara a quais sinais locais as entradas e saídas do módulo devem ser conectadas. Nos tutoriais anteriores desta sér

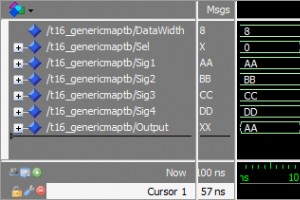

Criar módulos é uma ótima maneira de reutilizar código, mas geralmente você precisa do mesmo módulo com variações menores em todo o design. É para isso que servem os genéricos e o mapa genérico. Ele permite que você torne certas partes do módulo configuráveis em tempo de compilação. Constantes s

VHDL