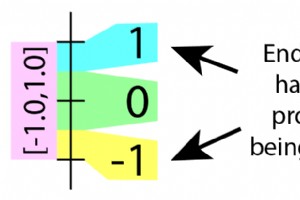

O VHDL tem um gerador pseudo-aleatório embutido, mas ele só pode gerar números de ponto flutuante entre 0 e 1. Felizmente, você pode derivar disso qualquer outro tipo de formato de dados aleatório que precise. Continue lendo este artigo para descobrir como produzir real ou integer valores de qualque

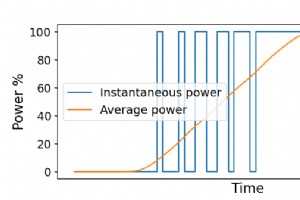

A modulação por largura de pulso (PWM) é uma maneira eficiente de controlar a eletrônica analógica a partir de pinos FPGA puramente digitais. Em vez de tentar regular a tensão analógica, o PWM liga e desliga rapidamente a corrente de alimentação com potência total para o dispositivo analógico. Este

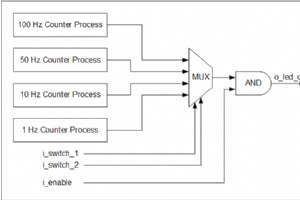

Percebi que muitos dos gadgets que comprei nos últimos dois anos mudaram de LED piscando para respiração conduzida. A maioria dos aparelhos eletrônicos contém um LED de status cujo comportamento dá indicações do que está acontecendo dentro do dispositivo. Minha escova de dentes elétrica pisca um L

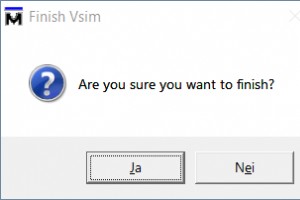

Como você interrompe o simulador VHDL quando a simulação é concluída? Existem várias maneiras de fazer isso. Neste artigo, examinaremos as maneiras mais comuns de encerrar uma execução bem-sucedida do testbench. O código VHDL apresentado aqui é universal e deve funcionar em qualquer simulador VHDL

A maioria dos simuladores VHDL usa o Tool Command Language (Tcl) como sua linguagem de script. Ao digitar um comando no console do simulador, você está usando Tcl. Além disso, você pode criar scripts com Tcl que rodam no simulador e interagem com seu código VHDL. Neste artigo, criaremos um testben

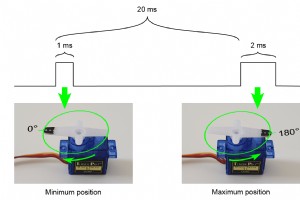

Servos de modelo controlados por rádio (RC) são atuadores minúsculos normalmente usados em modelos de aviões, carros e barcos amadores. Eles permitem que o operador controle o veículo remotamente por meio de um link de rádio. Como os modelos RC existem há muito tempo, a interface padrão de fato é

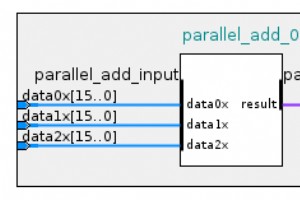

A instrução generate em VHDL pode duplicar automaticamente um bloco de código para encerramentos com sinais, processos e instâncias idênticos. É um loop for para a região de arquitetura que pode criar processos encadeados ou instâncias de módulo. Ao contrário de um loop for regular, que só pode

As cadeias de texto em VHDL geralmente são limitadas a matrizes de caracteres de comprimento fixo. Isso faz sentido porque o VHDL descreve o hardware e as strings de comprimento genérico requerem memória dinâmica. Para definir um array de strings, você precisa alocar espaço em tempo de compilação

Este tutorial aborda o uso do Analisador de lógica integrado (ILA) e Entrada/Saída Virtual (VIO) núcleos para depurar e monitorar seu design VHDL no Xilinx Vivado IDE. Em muitos casos, os designers precisam realizar a verificação no chip. Ou seja, obter acesso ao comportamento de um sinal interno

Ao projetar VHDL para aplicativos FPGA de segurança crítica, não é suficiente escrever testbenches com o melhor esforço. Você deve apresentar prova de que o módulo funciona como pretendido e sem efeitos colaterais indesejáveis. As técnicas de verificação formal podem ajudá-lo a mapear um requisito

VUnit é uma das estruturas de verificação VHDL de código aberto mais populares disponíveis atualmente. Ele combina um executor de suíte de testes Python com uma biblioteca VHDL dedicada para automatizar seus testbenches. Para lhe dar este tutorial VUnit gratuito, VHDLwhiz recruta Ahmadmunthar Za

Você já quis executar uma simulação VHDL que inclui um núcleo Quartus IP por meio da estrutura de verificação VUnit? Isso é o que o engenheiro da FPGA Konstantinos Paraskevopoulos tinha em mente, mas ele não conseguiu encontrar um tutorial adequado para isso. Felizmente, ele usou seu talento para

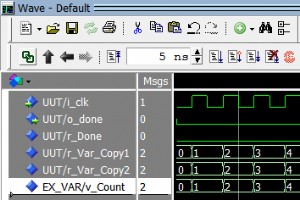

As variáveis em VHDL agem de forma semelhante às variáveis em C. Seu valor é válido no local exato do código onde a variável é modificada. Portanto, se um sinal usa o valor da variável antes a atribuição, ela terá o valor da variável antiga. Se um sinal usa o valor da variável depois a atribuiçã

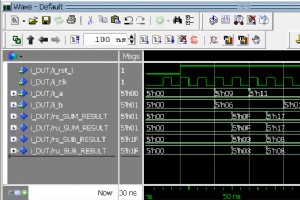

Todos os designers digitais devem entender como a matemática funciona dentro de um FPGA ou ASIC. O primeiro passo para isso é entender como os tipos de sinais assinados e não assinados funcionam. Existem tipos assinados e não assinados no numeric_std pacote, que faz parte da biblioteca ieee. Deve-se

A construção Record em VHDL pode ser usada para simplificar seu código. Os registros são semelhantes a estruturas em C . Os registros são usados com mais frequência para definir um novo tipo de VHDL. Este novo tipo contém qualquer grupo de sinais que o usuário desejar. Na maioria das vezes, isso é

Os procedimentos fazem parte de um grupo de estruturas chamadas subprogramas. Os procedimentos são pequenas seções de código que executam uma operação que é reutilizada em todo o código. Isso serve para limpar o código, bem como permitir a reutilização. Os procedimentos podem receber entradas e ge

Usando arquivos de pacote Numeric_Std e Std_Logic_Arith Abaixo estão as conversões mais comuns usadas em VHDL. A página é dividida em duas seções. A primeira metade da página mostra as conversões usando o arquivo de pacote Numeric_Std. A segunda metade da página mostra as conversões usando o arquiv

Parte 1:Design de VHDL ou Verilog Este tutorial mostra a construção do código VHDL e Verilog que pisca um LED em uma frequência especificada. Ambos VHDL e Verilog são mostrados, e você pode escolher qual deseja aprender primeiro. Sempre que o código de projeto é escrito, o projetista do FPGA precis

Usando o processo VHDL ou o Verilog sempre bloqueia Este tutorial mostra como escrever blocos de VHDL ou Verilog que estão contidos em um Processo ou um Sempre bloquear respectivamente. Processos (em VHDL) e Always Blocks (em Verilog) são fundamentais e precisam ser bem compreendidos. Eles se compo

VHDL é uma sigla horrível. Significa V HSIC H hardware D inscrição L língua. Uma sigla dentro de uma sigla, incrível! VHSIC significa V ery H alto S fiz xixi eu C integrado ircuito. Portanto, o VHDL expandido é V Circuito Integrado de Alta Velocidade H hardware D inscrição L língua. Ufa, isso é um b

VHDL