Chips de IA neuromórficos para spiking redes neurais estreiam

Innatera, a startup holandesa que fabrica aceleradores neuromórficos de IA para aumentar as redes neurais, produziu seus primeiros chips, avaliou seu desempenho e revelou detalhes de sua arquitetura.

A empresa também anunciou que o cofundador da Cadence e da Synopsys, Alberto Sangiovanni-Vincentelli, ingressou na empresa como presidente do conselho de administração. O veterano da indústria é atualmente professor da Universidade da Califórnia em Berkeley.

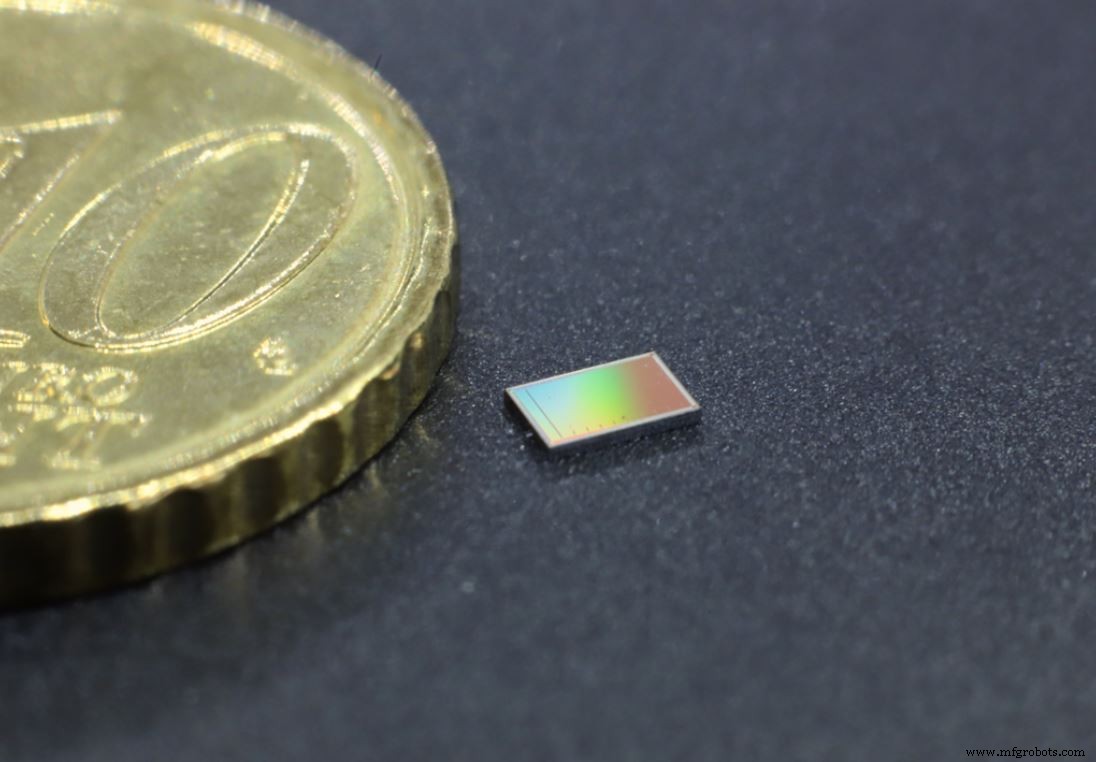

O chip de Innatera é projetado para acelerar diferentes SNNs para aplicações de áudio, saúde e radar (Imagem:Innatera)

O chip Innatera é projetado para acelerar spiking Neural Networks (SNNs), um tipo de algoritmo neuromórfico de IA baseado na biologia do cérebro que usa o tempo de picos em um sinal elétrico para realizar tarefas de reconhecimento de padrões. Os SNNs são completamente diferentes em estrutura dos algoritmos de IA convencionais e, portanto, requerem hardware dedicado para aceleração, mas normalmente oferecem consumo de energia significativo e vantagens de latência para aplicações de ponta de sensor.

A maioria das outras empresas que trabalham no aumento de algoritmos e hardware de rede neural (por exemplo, a Prophesee) tem como alvo imagens e fluxos de vídeo. A Innatera decidiu se concentrar em áudio (reconhecimento de som e fala), saúde (monitoramento de sinais vitais) e radar (para casos de uso de consumidor / IoT, como sensores de queda de idosos que mantêm a privacidade).

Marco Jacobs (Imagem:Innatera)

“Esses sensores têm dados de séries temporais, em vez de imagens que são muito paralelas”, disse Marco Jacobs, vice-presidente de marketing e desenvolvimento de negócios da Innatera, em entrevista ao EE Times . “Nosso array é especialmente bom no processamento de dados de séries temporais ... é um bom ajuste de tecnologia. Além disso, de uma perspectiva de mercado, vemos muitas aplicações interessantes nesta área e não tantas soluções que atendam a isso. ”

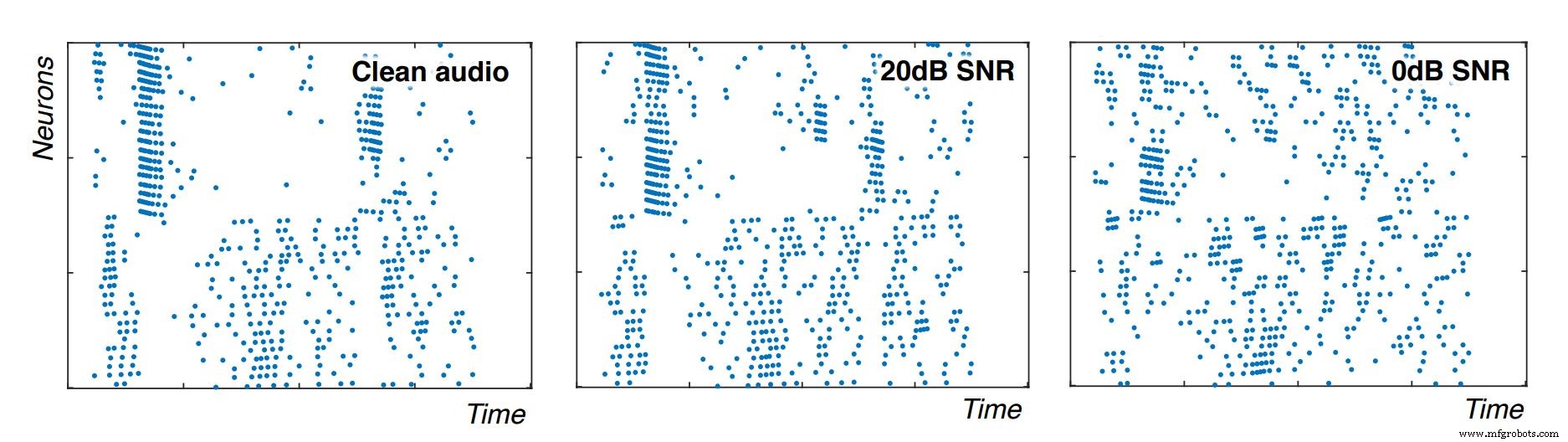

Outra coisa que esses três aplicativos têm em comum é que, como o processamento é necessário no nó do sensor, o envelope de energia é muito restrito. Nos testes de Innatera, cada evento de pico (cada neurônio disparando em resposta aos dados de entrada) exigiu menos do que um picoJoule de energia - na verdade, menos de 200 femtoJoules em TSMC 28nm, confirmou Innatera. Isso está se aproximando da quantidade de energia usada por neurônios biológicos e sinapses. Um aplicativo típico de detecção de palavras-chave de áudio exigia menos de 500 eventos de pico por inferência, resultando em "dissipação de energia sub-miliWatt profunda", de acordo com o CEO da Innatera, Sumeet Kumar. Nesse caso, grupos de neurônios disparando juntos representam diferentes fonemas na fala.

Grupos de neurônios disparando (grupos de pontos aqui) representam a detecção de fonemas na fala. Como os dados de entrada incorporam mais ruído, os mesmos clusters estão principalmente presentes, embora sejam mais difíceis de detectar (Imagem:Innatera)

Arquitetura de processamento

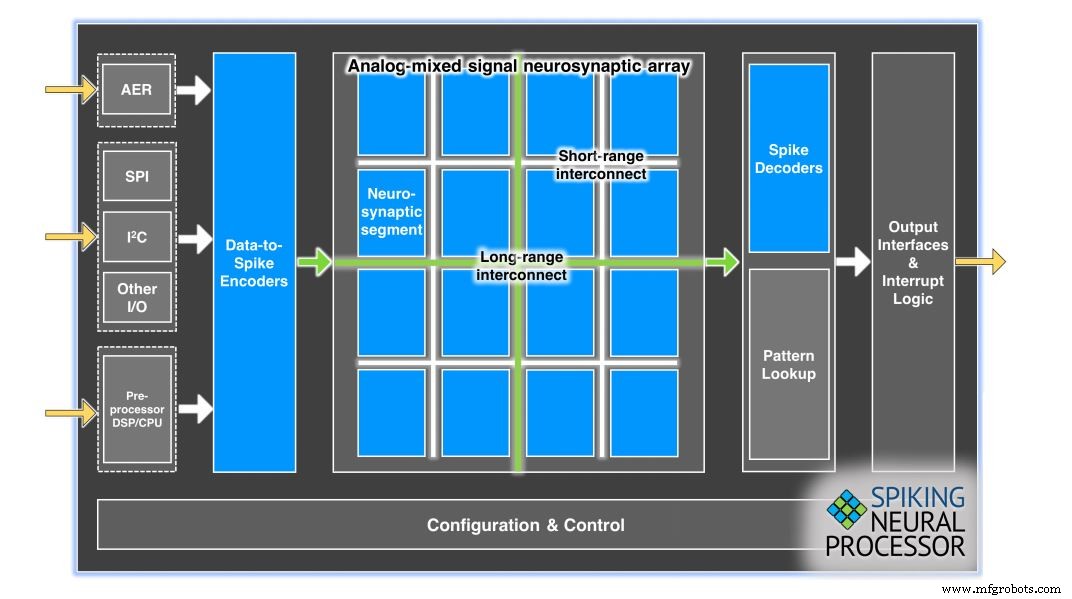

O processador neural de spiking de Innatera usa uma matriz paralela de neurônios de spiking e sinapses para acelerar SNNs de tempo contínuo com dinâmica temporal refinada. O dispositivo é um acelerador de sinal analógico / misto projetado para alavancar a capacidade do SNN de incorporar a noção de tempo em como os dados são processados.

O processador neural de pico de Innatera inclui uma matriz neuro-sináptica massivamente paralela e codificadores e decodificadores de pico (Imagem:Innatera)

Um dos principais aspectos das malhas de computação da Innatera é sua programabilidade, que é importante por duas razões.

Primeiro, programar SNNs diferentes no chip. Os neurônios precisam ser conectados de maneira flexível - o cérebro usa topologias de rede neural muito complexas para fazer as coisas com eficiência, o que requer conexões complexas entre os neurônios, que precisam ser recriadas em silício.

Sumeet Kumar (Imagem:Innatera)

Em segundo lugar, para otimizar o desempenho. Em vez de representar informações como bits em palavras, em um SNN as informações são representadas como picos precisamente cronometrados. O tempo dos picos precisa ser manipulado em um nível muito refinado para extrair insights sobre os dados. Os neurônios e as conexões entre eles (as sinapses), portanto, precisam exibir comportamentos de temporização complexos. Esses comportamentos podem ser ajustados por meio do SDK do Innatera para otimizar o desempenho.

Innatera descreve seu chip como um sinal analógico misto ou "analógico assistido digitalmente". Neurônios e sinapses são implementados em silício analógico para manter o consumo de energia ultrabaixo. A eletrônica analógica também permite redes de tempo contínuo (a eletrônica digital exigiria discretização). Isso é importante para SNNs porque sua natureza significa que eles têm inerentemente uma noção de tempo e precisam ser capazes de manter determinados estados por um período de tempo.

“Fazer isso é muito mais fácil no domínio analógico - você não precisa mudar a complexidade de manter o estado na topologia da rede”, disse Kumar. “Nossos elementos de computação retêm naturalmente essa informação de estado. Esta é a razão pela qual fazemos coisas no domínio analógico. ”

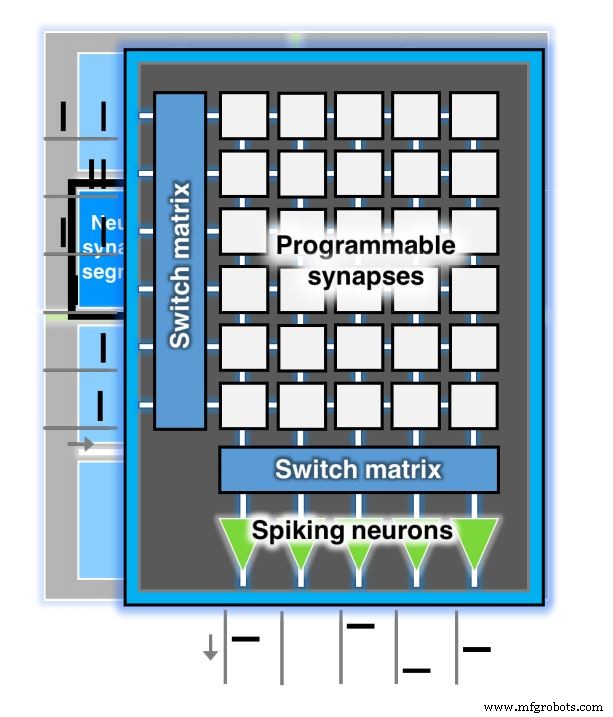

Um segmento de computação na matriz de Innatera, onde os neurônios são projetados para serem cuidadosamente combinados. As sinapses programáveis são organizadas em uma estrutura de barra transversal de vários níveis. (Linhas pretas / travessões aqui representam picos de entrada e saída) (Imagem:Innatera)

Pequenas inconsistências na fabricação entre elementos de computação no chip e entre diferentes chips podem ser um problema para a implementação de redes neurais com precisão no domínio analógico. A solução de Innatera é agrupar neurônios no que chama de segmentos, que são cuidadosamente projetados para combinar comprimentos de caminho e número de neurônios.

O design do segmento “essencialmente nos permite usar o melhor dos circuitos analógicos, ao mesmo tempo em que minimiza essas não-idealidades que você normalmente teria em um circuito analógico”, disse Kumar. “Tudo isso foi feito essencialmente para garantir que os neurônios dentro de um segmento exibam comportamento determinístico e funcionem de forma semelhante a seus vizinhos imediatos.”

Inconsistências entre chips diferentes podem causar problemas quando a mesma rede treinada é implementada para dispositivos em campo. Innatera contorna isso com software.

“A incompatibilidade e a variabilidade são tratadas profundamente no SDK”, disse Kumar. “Se você é um usuário avançado, podemos expor um pouco disso a você, mas um programador típico não precisa se preocupar com isso.”

Específico do aplicativo

Innatera, um spin-out da Delft University of Technology, já estava trabalhando com clientes de receita em seus algoritmos SNN antes de passar para o hardware e levantar uma rodada inicial de € 5 milhões (cerca de US $ 6 milhões) no final de 2020.

“Temos trabalhado com vários clientes desde o momento em que realmente começamos a empresa, e esses compromissos ainda estão em andamento - eles amadureceram de forma significativa”, disse Kumar. “Esperamos poder mostrar mais demonstrações junto com alguns desses clientes no final deste ano.”

Kumar disse que a empresa mantém seu foco como uma empresa de soluções de computação, ou seja, fornecerá soluções turnkey que incluem hardware e algoritmos SNN específicos para aplicativos.

O primeiro chip do Innatera é adequado para aplicações de áudio, saúde e radar. O roteiro da empresa pode incluir mais chips otimizados para cada uma das aplicações.

“Nós arquitetamos o dispositivo de forma que pudéssemos acelerar uma ampla variedade de redes neurais de spiking”, disse Kumar. “[Nosso chip] pode implementar essas redes em domínios de aplicativos. Mas, à medida que avançamos nos domínios, pode ser necessário otimizar o design do hardware, e isso é algo que examinaremos no futuro. No momento, o hardware não é excessivamente especializado para qualquer classe específica de aplicativos ou qualquer estilo de spiking redes neurais, o objetivo é oferecer suporte a uma variedade deles geralmente dentro da arquitetura. ”

Amostras do chip inicial devem estar disponíveis antes do final de 2021.

>> Este artigo foi publicado originalmente em nosso site irmão, EE Vezes.

Conteúdos Relacionados:

- O chip AI visa dispositivos periféricos de baixo consumo

- Corrente de ferramentas e placa de sensor aprimoram o ecossistema de chips de IA

- Novos módulos de aceleração de IA melhoram o desempenho de ponta

- IA no limite:o que procurar em 2021

- Como implementar IA das coisas (AIoT) em MCUs

Para obter mais informações sobre o Embedded, assine o boletim informativo semanal por e-mail da Embedded.

Integrado

- Co-simulação para designs baseados em Zynq

- Renesas:chips automotivos adotados pela Nissan para seu novo Skyline ProPILOT 2.0

- CEVA:processador AI de segunda geração para cargas de trabalho de rede neural profunda

- Argumentando sobre chips neuromórficos para computação IA

- Chip de radar de baixa potência usa redes neurais com pico

- Lanner:gateway de borda pronto para LTE certificado para IoT e SD-WAN em redes celulares

- IBM na SPIE:Sete avanços para além dos chips 7nm

- NPE é estreia nos EUA para o Campetella Robotic Center

- 3G morreu:o que vem a seguir para designers de produto?

- LoRaWAN substituirá temporariamente as redes 5G para IoT