Melhoria do desempenho do dispositivo a-IGZO TFT usando um processo de interface limpa por meio de nanocamadas Etch-Stopper

Resumo

Para superar os obstáculos tecnológicos e econômicos do óxido de índio-gálio-zinco amorfo (a-IGZO) para a produção industrial, um processo de rolha de corrosão limpo (CL-ES) é desenvolvido para fabricar finas à base de a-IGZO transistor de filme (TFT) com melhor uniformidade e reprodutibilidade em substratos de vidro de 8,5 geração (2200 mm × 2500 mm). Comparado com a TFT baseada em a-IGZO com estrutura gravada em canal traseiro (BCE), uma nano-camada ES recém-formada (~ 100 nm) e uma gravação simultânea de nano-camada a-IGZO (30 nm) e fonte-dreno camada de eletrodo é primeiramente introduzida em um dispositivo TFT baseado em IGZO com estrutura CL-ES para melhorar a uniformidade e estabilidade do dispositivo para exibição em grandes áreas. A mobilidade de elétrons de saturação de 8,05 cm 2 / V s e o V th uniformidade de 0,72 V são realizadas no dispositivo TFT baseado em a-IGZO com estrutura CL-ES. No teste de estresse de iluminação de temperatura de polarização negativa e teste de confiabilidade de estresse térmico de polarização positiva sob uma polarização de ± 30 V para 3600 s, o V medido th a mudança do dispositivo estruturado CL-ES diminuiu significativamente para - 0,51 e + 1,94 V, que são muito mais baixos do que o dispositivo estruturado BCE (- 3,88 V, + 5,58 V). O desempenho elétrico do dispositivo TFT baseado em a-IGZO com estrutura CL-ES implica que a transferência econômica de um processo TFT baseado em silício para o processo baseado em semicondutor de óxido metálico para fabricação de LCD é altamente viável.

Histórico

O painel traseiro do transistor de filme fino (TFT) com resolução mais alta e tamanho de painel maior é altamente desejado na indústria de monitores planos. O material semicondutor com alta mobilidade de elétrons é crucial para melhorar o desempenho do backplane TFT. Em particular, um backplane TFT baseado em semicondutor de óxido metálico é considerado um candidato promissor para superar a limitação do backplane TFT baseado em silício em termos de flexibilidade mecânica e mobilidade de elétrons [1,2,3,4]. Embora um backplane TFT baseado em semicondutor de óxido metálico apresente propriedades promissoras, o método de processo com um processo de baixo custo tanto para deposição em larga escala para aplicação industrial ainda é necessário [5].

Óxido de índio-gálio-zinco amorfo (a-IGZO) é um excelente semicondutor de óxido de metal com uma alta mobilidade de elétrons de saturação (~ 5–10 cm 2 / V s) e uma baixa corrente de desligamento (<10 pA) [6,7,8,9,10]. O método de produção industrial comum para o painel traseiro TFT baseado em a-Si:H é o processo de cinco máscaras-back-channel-etched (BCE). No entanto, o nano-filme a-IGZO tem uma resistência química muito baixa aos decapantes típicos atualmente usados no processo BCE. Especialmente, nano-filmes de a-IGZO seriam completamente atacados em poucos segundos quando eles são expostos ao ácido fosfórico, ácido nítrico e ácido acético [11,12,13]. Esta gravação incontrolavelmente rápida impede a adoção do processo BCE para um painel traseiro TFT baseado em a-IGZO. Para utilizar a-IGZO no painel traseiro estruturado de BCE, a tecnologia de fiação Cu foi desenvolvida, como o agente de corrosão usado no processo de fiação Cu, que é baseado em H 2 O 2 , é muito mais suave para um nano-filme a-IGZO do que os usados na fiação de Al [11, 13]. Infelizmente, o nano-filme a-IGZO ainda é danificado durante o processo de fiação de Cu, mesmo quando um ácido acondicionador mais suave é usado. Mesmo gravações mais suaves causam danos na superfície de um nano-filme IGZO que forma o canal traseiro dos dispositivos TFT. Esses danos causam colapso na proporção da composição molecular estequiométrica próximo à superfície de um nano-filme de a-IGZO, levando ao agravamento da uniformidade na exibição de grandes áreas e confiabilidade do dispositivo TFT. Até o momento, o processo convencional de seis máscaras de gravação (CV-ES) é desenvolvido para fabricar um backplane TFT baseado em IGZO com estrutura de capa de gravação (ESL) [14, 15]. No entanto, este processo ES de seis máscaras pode levar a uma viabilidade econômica negativa. Além disso, este número aumentado de camadas de filme fino aumentaria a área de sobreposição entre camadas e resultaria no aumento da capacitância parasitária e diminuição da razão de abertura [16,17,18]. Embora o processo ES de cinco máscaras que produz o backplane TFT usando meio-tom e tecnologia de decolagem tenha sido relatado recentemente, este processo não é acessível para a produção de um backplane TFT baseado em IGZO, já que sua superfície de camada ativa ainda está exposta a produtos químicos de processo, como stripper e fotoresiste na última etapa, que podem causar contaminação considerável ao a-IGZO, reduzindo assim a qualidade do dispositivo e o rendimento da produção [19,20,21]. Portanto, o método de produção industrial para um backplane TFT baseado em IGZO com alta uniformidade e estabilidade permanece um desafio.

Neste artigo, propomos um processo ES limpo de cinco máscaras (CL-ES) por meio da introdução de ESL para a fabricação de um backplane TFT baseado em IGZO. Este processo CL-ES recém-desenvolvido é altamente compatível com o processo existente para o dispositivo BCE. Este processo CL-ES é projetado para ter as máscaras iguais às do processo BCE, o que garante uma perda insignificante de produtividade do painel traseiro AM-LCD TFT FAB existente. Um backplane baseado em a-IGZO produzido usando isolador de porta de depósitos de processo CL-ES, nano-camada IGZO e nano-camada ES sequencialmente, então forma uma nova máscara ESL através do método dry-etch. Isso pode evitar a contaminação de uma nanocamada de a-IGZO e sua interface de ácido, removedor e solvente. Esta nano-máscara recém-formada ajuda a melhorar a uniformidade e estabilidade do dispositivo TFT. Comparado ao dispositivo convencional com estrutura BCE, o dispositivo baseado em a-IGZO com estrutura CL-ES mostra desempenho elétrico aprimorado, ou seja, uma mobilidade de elétrons de saturação mais alta, uma alta taxa de abertura e um baixo consumo de energia.

Métodos / Experimental

Fabricação de um painel traseiro TFT baseado em IGZO

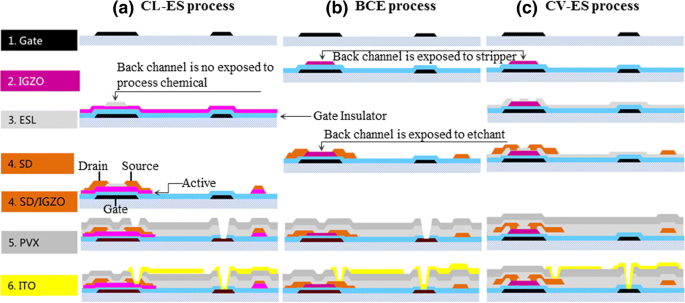

O backplane TFT baseado em a-IGZO com estrutura ES fabricado via processo CL-ES era o seguinte (Fig. 1).

(Cor online) Esquemas de a CL-ES, b BCE e c Processos CV-ES

Em primeiro lugar, a camada dupla (Mo / Cu:30 nm / 250 nm) foi usada para o eletrodo de porta, pois tem uma resistividade razoavelmente baixa. Em seguida, o isolador de porta, nitreto de silício (SiNx) / óxido de silício (SiOx) (300 nm / 100 nm), foi depositado pelo método de deposição química a vapor intensificada por plasma (PECVD). Este filme de SiNx é projetado para prevenir a oxidação da metalização do Cu e a difusão do íon Cu no isolador da porta. Posteriormente, um filme fino de SiOx foi depositado. As condições de deposição do filme PECVD SiOx foram 17-KW de potência de RF, pressão de 1000 mTorr, 1:55 SiH 4 / N 2 Razão de gás O e temperatura de 350 ° C. Em seguida, um nano-filme de a-IGZO foi depositado a 30 nm usando sputter magnetron rotativo dc. O alvo tinha o diâmetro de 171 mm, enquanto a composição estava em 2 O 3 :Ga 2 O 3 :ZnO =1:1:1% molar. Os parâmetros de pulverização catódica para o nano-filme a-IGZO foram a pressão de base do sistema de 5 ~ 9 × 10 −7 Torr, potência de pulverização catódica rf de 10 KW, pressão de pulverização catódica de 5-mTorr Ar / O 2 mistura de gás (85% Ar-15% O 2 ) A temperatura de deposição está em condição ambiente. O filme a-IGZO produzido é recozido a 330 ° C por 1 h em ambiente de ar limpo e seco.

Em segundo lugar, a nanocamada (SiOx) de rolha de corrosão (ES) foi depositada usando o método PECVD. A nano camada ES é depositada simultaneamente para evitar a contaminação em uma camada de IGZO. Como no processo BCE, não há camada protetora para um nano-filme a-IGZO antes do processo de padronização do eletrodo S / D, contaminação da superfície e danos no nano-filme a-IGZO por S / D etchant quando formar o canal TFT é inevitável. A nano camada ES no processo CL-ES pode proteger eficazmente o canal TFT de contaminação externa e danos. A nano-camada ES foi depositada com uma espessura de 100 nm. As condições de deposição do filme fino de SiOx foram 17-KW de potência de RF, pressão de 1000 mTorr, 1:66 SiH 4 / N 2 Razão de gás O e temperatura de 240 ° C. A nano-máscara ES produzida foi gravada por corrosão seca e padronização. Durante o processo de gravação, CF 4 e O 2 o gás foi fornecido a uma taxa de 2.000 sccm / 800 sccm.

Em terceiro lugar, Mo / Cu / Mo também foi usado para o eletrodo S / D. Para selecionar o eletrodo S / D de a-IGZO TFT, a diferença de função de trabalho entre o metal e a-IGZO foi considerada para formar um contato ôhmico e os materiais de baixa resistividade. Conforme descrito no processo de rolha de corrosão, durante a padronização da nano-máscara ES, os nano-filmes a-IGZO, que não são protegidos pela camada de rolha de corrosão, já são conduzidos sendo bombardeados com CF 4 plasma. Portanto, o contato ôhmico é formado naturalmente com Mo / Cu / Mo [22]. As camadas S / D foram depositadas na espessura de 30 nm / 300 nm / 30 nm com as mesmas condições de sputtering do eletrodo de porta. Além disso, camadas de filme multi-fino de Mo / Cu / Mo e a-IGZO foram gravadas em lote usando “H 2 O 2 ácido acondicionador à base de Cu contendo um aditivo de flúor ”para completar o eletrodo S / D. Os 30 nm de Mo adicionado no topo do Cu foram formados para prevenir a oxidação da superfície do Cu por filme de passivação (SiOx) no próximo processo e para prevenir o dano do plasma da superfície do Cu, durante o ataque a seco para a formação do orifício de passivação.

Em quarto lugar, o filme de passivação, dividido em dois tipos de filme fino, foi depositado pelo método PECVD. A primeira passivação foi feita de película fina de SiOx. O filme fino tinha 250 nm de espessura. A segunda passivação foi constituída por uma película fina de SiNx. A espessura da película fina era de 200 nm.

Em quinto lugar, como o eletrodo de pixel, foi utilizado o filme de óxido de estanho e índio (ITO), que é mais comumente usado na indústria de telas. O filme ITO tinha 40 nm de espessura e pulverização catódica CC foi usada para a deposição. Em seguida, o recozimento final foi realizado em um ambiente de ar limpo e seco a 230 ° C por 1 h usando um forno de ar quente. As características elétricas dos TFTs a-IGZO fabricados foram medidas usando o sistema de teste paramétrico Keysight 4082A. Este processo obterá o mesmo número de máscaras (padrão de produto TN:cinco máscaras) que o processo BCE, que é amplamente utilizado na fabricação em massa.

Para efeito de comparação, o backplane TFT baseado em a-IGZO com estrutura BCE foi fabricado via processo BCE.

Caracterização

A medição I-V do TFT foi conduzida em temperatura ambiente usando um analisador de característica de semicondutor. A condição de análise para avaliar a estabilidade do TFT sob estresse de iluminação de temperatura de polarização de porta negativa (NBTIS) foi a seguinte. V gs e V ds foram fixados respectivamente em - 30 e 15 V, e a temperatura do substrato foi mantida a 60 ° C. A luminância para NBITS foi fixada em 5000 cd / m 2 . A duração do estresse para avaliação continuou por 3600 s [23]. O estresse térmico de polarização positiva (PBTS) foi testado em um V gs de 30 V e um V ds de 15 V, e a temperatura do substrato foi fixada em 60 ° C. A duração do estresse para avaliação continuou por 3600 s [24].

Resultados e discussão

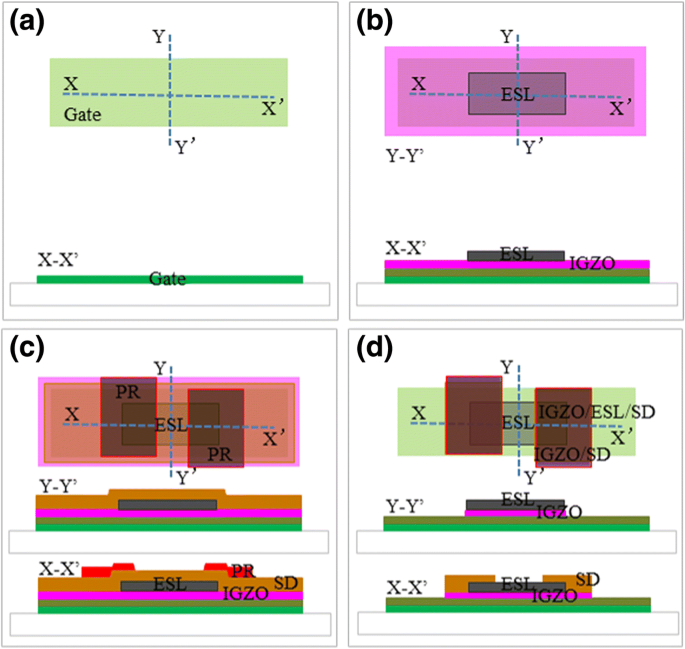

TFT baseado em a-IGZO fabricado via processo CL-ES mostra o mesmo número de máscara daquele do processo BCE (Fig. 1). Comparado com o TFT baseado em a-IGZO com estrutura BCE, o TFT baseado em a-IGZO com estrutura CL-ES mostra duas vantagens:(1) backplane baseado em a-IGZO produzido usando isolador de porta de depósitos de processo CL-ES, a-IGZO nano -camada, e nano-camada ES sequencialmente, então forma uma nano-máscara ESL através do método de gravação a seco. Esta nano-máscara ESL recém-formada com 100 nm pode evitar a exposição de um nano-filme a-IGZO a ácido, removedor ou fotorresistente. Portanto, a contaminação nas interfaces inter-camadas é efetivamente evitada [25]. (2) Ao mesmo tempo, o nano-filme a-IGZO não é protegido pela camada ES, mas bombardeado por CF 4 plasma durante a formação da nano-máscara ESL, portanto, torna-se um condutor. Isso naturalmente forma o contato ôhmico entre o eletrodo S / D do processo seguinte e o semicondutor a-IGZO. Por outro lado, uma gravação simultânea de S / D e a-IGZO nano-camada pode ser uma permissão de sobreposição de camada ESL- (metalização a-IGZO + S / D), o que poderia diminuir os dois erros de processo de sobreposição de a- Camada de metalização IGZO-ESL e ES-S / D no processo ESL convencional (Fig. 2). O número de sobreposição da camada a-IGZO, ES e S / D é reduzido, o que resultou na diminuição do tamanho do dispositivo TFT que reduziu a capacitância parasita. A estrutura planar do resultado é semelhante à estrutura BCE (Fig. 3a, b).

(Cor online) Esquemas do método de formação simultânea para canal TFT e eletrodo S / D no processo CL-ES. a A primeira etapa que forma o eletrodo de porta. b A segunda etapa que forma a camada de rolha de corrosão. c A terceira etapa que forma o padrão de foto S / D. d A quarta etapa que forma o eletrodo S / D e o padrão ativo

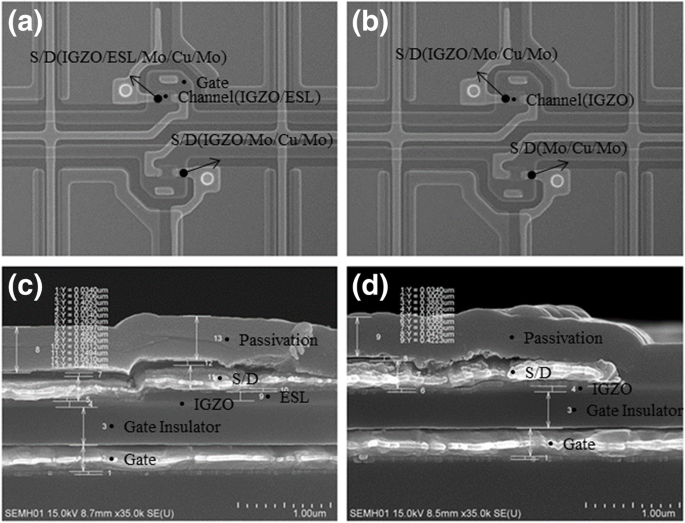

(Colorir online) Imagens SEM de a-IGZO TFT ( a , b vista do topo; c , d vista lateral) com estrutura CL-ES ( a , c ) e estrutura BCE ( b , d )

A Figura 3 mostra as imagens SEM de TFTs baseados em a-IGZO com estrutura CL-ES (Fig. 3a, c) e estrutura BCE (Fig. 3b, d). Visto de cima, é difícil identificar as diferenças entre a estrutura CL-ES e a estrutura BCE (Fig. 3a, b). Da vista lateral, uma nano camada ES pode ser encontrada entre a nano camada a-IGZO e a camada de eletrodo S / D na estrutura CL-ES (Fig. 3c). Enquanto isso, uma camada de passivação pode ser encontrada no topo da nano-camada a-IGZO na estrutura BCE (Fig. 3d). No processo CL-ES apresentado, uma nano-camada de a-IGZO com uma espessura de 30 nm é depositada. Além disso, os danos durante a corrosão úmida são insignificantes. Para o processo BCE, uma nano camada a-IGZO de 70 nm é depositada, pois a camada a-IGZO precisa de compensação para perda de corrosão. A diferença entre as espessuras das nano-camadas de a-IGZO em estruturas CL-ES e BCE pode ser observada nas imagens SEM (Fig. 3c, d).

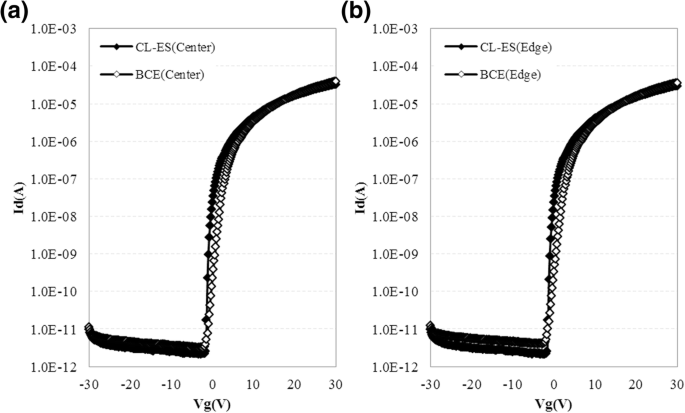

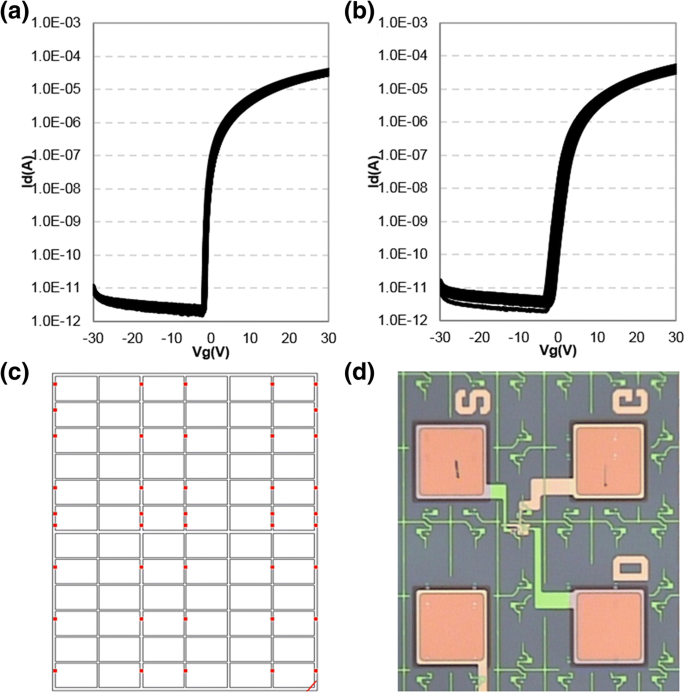

As características I-V de um TFT baseado em a-IGZO com estrutura CL-ES e estrutura BCE são comparadas (Fig. 4). A mobilidade do elétron de saturação, a tensão de limiar, o valor de oscilação de tensão de sublimiar (SS) e mais valores característicos estão resumidos na Tabela 1. Observe que os valores resumidos na Tabela 1 são o número médio derivado do centro e da borda de um substrato de vidro de 8,5 geração . O TFT baseado em a-IGZO com estrutura CL-ES realiza V th de - 0,8 V, valor SS de 0,18 V / dec e mobilidade de elétrons de saturação de 8,05 cm 2 / V s. No TFT baseado em a-IGZO com estrutura BCE, os resultados correspondentes são V th de + 0,5 V, valor SS de 0,77 V / dec e mobilidade de elétrons de saturação de 6,03 cm 2 / V s. Em comparação com a estrutura BCE, a estrutura CL-ES mostra um desempenho de dispositivo aprimorado. No entanto, a característica na corrente do dispositivo TFT baseado em a-IGZO com estrutura CL-ES é menor do que com dispositivo estruturado BCE. Isso se deve ao fato de que as estruturas do canal TFT são diferentes nas estruturas CL-ES e BCE. Geralmente, o comprimento do canal TFT estruturado em BCE é a distância entre os eletrodos de metal S / D, e o comprimento do canal medido neste estudo é 5 um [21]. Na estrutura CL-ES, os eletrodos estão em contato com o nano-filme a-IGZO que é esticado na lateral da nano-máscara ESL. Portanto, o comprimento do canal é decidido pela distância entre os a-IGZOs definidos nos lados da rolha de corrosão, mas não determinado pela distância entre os eletrodos. O comprimento do canal do dispositivo de estrutura CL-ES atual é medido em 10 um.

(Cor online) Comparação das características I-V de a-IGZO TFTs com CL-ES e estrutura BCE no centro ( a ) e borda ( b ) de substrato de vidro de 8,5 geração

Conforme mostrado na Tabela 1, os valores medidos de I em / eu desligado proporção (~ 10 6 , consulte a Tabela 1) são aproximadamente 10 vezes menores do que o valor típico (> 10 7 ) de TFTs baseados em a-IGZO. Isso ocorre porque o equipamento de medição usado aqui é para a produção em massa de 8,5 gerações. Cabos longos são necessários para essas medições, pois o tamanho do equipamento industrial é grande. Os cabos longos resultaram em um aumento do ruído de medição. No teste de confiabilidade a seguir, é utilizado equipamento de medição em escala menor e os dispositivos TFT individuais são usados como espécime para medição. Desta forma, o medido eu em / eu desligado as proporções são todas 10 7 superiores (ver abaixo).

O processo CL-ES é cuidadosamente projetado para evitar que uma camada de canal de IGZO seja exposta a corrosão, fotorresiste ou stripper. Durante o processo que produz o processo CL-ES, isolador de porta, nano-camada a-IGZO e nano-camada ES, cada interface entre camadas está em contato apenas com água DI para fins de limpeza. Conseqüentemente, a contaminação química é desprezível na camada isolante e nano-camada a-IGZO [25, 26]. No entanto, o processo BCE não apenas expõe a camada do canal aos produtos químicos, mas também envolve a contaminação por difusão do íon Cu, uma vez que o canal a-IGZO está diretamente exposto ao metal Cu. Isso também é evitado em dispositivos com estrutura CL-ES. A região do canal do nano-filme a-IGZO é bem protegida pela nano-máscara ESL. A baixa contaminação química no processo CL-ES pode levar a uma baixa densidade de armadilha de portadores na interface entre a nanocamada a-IGZO e a camada isolante, resultando em um excelente valor de SS. Esta baixa contaminação química de um dispositivo TFT baseado em a-IGZO via processo CL-ES também ajuda a melhorar a uniformidade e reprodutibilidade de a-IGZO TFT, que são altamente importantes na produção industrial [27, 28].

A Figura 5 mostra a característica I-V medida de TFTs com estrutura CL-ES e estrutura BCE derivada de 42 pontos de medição em um substrato de geração 8,5. TFT baseado em a-IGZO com estrutura CL-ES tem um V th faixa de 0,72 V, enquanto a do dispositivo com estrutura BCE é de 2,14 V (Tabela 1). Em outras palavras, a uniformidade de desempenho do dispositivo é significativamente melhorada pela estrutura CL-ES.

(Cor online) a Estrutura CL-ES. b Característica de transferência I-V dos TFTs da estrutura BCE. c 42 pontos de medição. d a foto do TFT. Todos medidos em um substrato de 8,5 geração

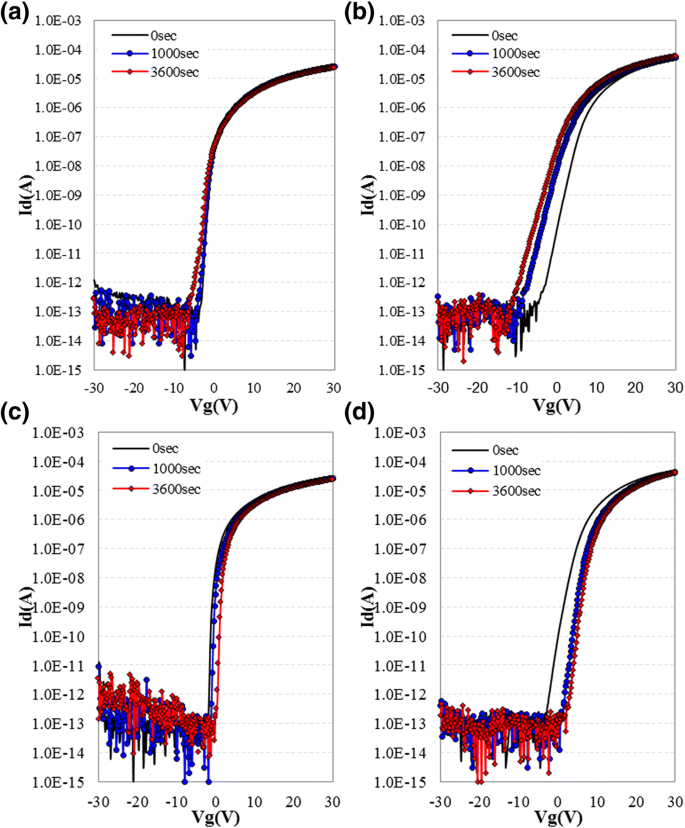

A Figura 6a, b mostra a mudança característica I-V do dispositivo estruturado CL-ES e dispositivo estruturado BCE obtido no teste NBTIS, respectivamente. Os resultados do teste NBTIS estão resumidos na Tabela 2. Sob a condição de estresse descrita na Tabela 2, o V th o deslocamento do dispositivo estruturado CL-ES e do dispositivo estruturado BCE é - 0,51 e - 3,88 V, respectivamente. Além disso, o deslocamento na corrente, o deslocamento fora da corrente e a variância do valor SS do dispositivo estruturado CL-ES são todos inferiores aos do dispositivo estruturado BCE (Tabela 2); isso ocorre porque um dispositivo baseado em a-IGZO com estrutura CL-ES pode prevenir efetivamente a contaminação de a-IGZO e diminuir a densidade de armadilha de portadora de um canal TFT de a-IGZO. Especialmente, ao olhar para o resultado dos primeiros 1000 s de estresse, nenhuma mudança de valor de SS é observada no dispositivo estruturado CL-ES. Este fenômeno é comparável ao aumento de 0,16 V / dec no valor SS do dispositivo estruturado BCE, pois mostra que os locais de defeito, que podem formar armadilhas de portadores na superfície de um nano-filme a-IGZO, constituindo o canal traseiro CL-ES TFT, não são criados adicionalmente por estresse elétrico e de iluminação. Esses resultados provam totalmente que o dispositivo estruturado CL-ES é muito mais estável do que o dispositivo estruturado BCE. A Figura 6c, d mostra o deslocamento da curva I-V de TFTs estruturados CL-ES e BCE obtidos a partir de testes PBTS. Os resultados detalhados dos testes de PBTS estão resumidos na Tabela 3. Tanto o TFT estruturado em CL-ES quanto o TFT estruturado em BCE diminuíram na corrente de íons durante a avaliação de PBTS. Isso é causado pela mudança em V th para a direção positiva. Durante a avaliação de PBTS, a razão de corrente de íon residual [(último íon / íon inicial) × 100] do TFT estruturado em CL-ES com V relativamente menor th deslocamento positivo (+ 1,94 V) está no nível de 88,2%. Quando comparado com a razão de corrente de íon residual do TFT estruturado BCE de 41,3%, o TFT estruturado CL-ES é significativamente superior. Isso mostra a importante diferença de capacidade durante o projeto do circuito de gate drive on array (GOA). Diferente de NBTIS, o valor SS do TFT estruturado CL-ES não tem variação significativa ((∆SS 0,06 V / dec), ou melhor, diminui (∆SS - 0,86) como o TFT estruturado BCE. Isso talvez se deva ao portadores, se acumulam no espaço interno e na interface entre o isolador de porta e nano-filme a-IGZO por polarização de porta positiva, preenchendo o local da armadilha de portadores no estágio inicial, causando diminuição no fenômeno de armadilha de portadores. Além disso, o fenômeno de mudança de voltagem de limiar ocorre por carga da portadora presa perto da interface entre o isolador da porta e a nano-filme a-IGZO. A pequena mudança de tensão de limiar do TFT estruturado em CL-ES representa que a interface e o espaço interno de a-IGZO são notavelmente limpos. Em conclusão, o teste de PBTS também sugere que a estrutura e o processo do CL-ES levam a uma melhor confiabilidade do dispositivo.

(Cor online) Desvio característico de transferência I-V de CL-ES ( a , c ) e BCE ( b , d ) TFT obtido de NBITS ( a , b ) e teste PBTS ( c , d )

Conclusões

Em conclusão, um processo CL-ES recém-desenvolvido foi desenvolvido com sucesso para fabricar um painel traseiro TFT baseado em IGZO com cinco máscaras para exibição avançada. O processo CL-ES tem as vantagens de uma estrutura de camada de rolha de corrosão, mantendo o mesmo número de máscaras e áreas de dispositivo semelhantes a um processo BCE, que supera o problema de aumento do número de máscara e área ocupada em dispositivos TFT convencionais de rolha de corrosão . Uma nano-máscara ESL recém-formada e um ataque simultâneo de nano-camada a-IGZO e nano-camada de eletrodo S / D permitem uma alta uniformidade e estabilidade do dispositivo para exibição em grandes áreas. Em relação ao desempenho elétrico, a reprodutibilidade e a confiabilidade do desempenho do dispositivo de um TFT baseado em a-IGZO com estrutura CL-ES são muito melhores do que a do dispositivo estruturado BCE. O dispositivo TFT baseado em a-IGZO tem um V th distribuição em 42 pontos de medição TFTs no substrato de vidro de 8,5 geração de 0,72 V, mobilidade de elétrons de saturação de 8,05 cm 2 / V s e valor SS de 0,18 V / dec. De acordo com os resultados da avaliação de confiabilidade obtidos do NBTIS e PBTS, V th as variações antes e depois do estresse de TFTs baseados em CL-ES a-IGZO são - 0,51 e 1,94 V após 3600 s de estresse, respectivamente. As variações do valor SS são 0,33 e 0,06 V / dec. Portanto, ao superar os obstáculos tecnológicos e econômicos, a técnica CL-ES apresentada abrirá o caminho para a próxima geração de produtos de alta resolução e grandes painéis.

Abreviações

- a-IGZO:

-

Óxido de índio-gálio-zinco amorfo

- AM-LCD:

-

Tela de cristal líquido de matriz ativa

- BCE:

-

Gravura do canal traseiro

- ESL:

-

Camada anti-corrosiva

- GOA:

-

Gate drive na matriz

- NBTIS:

-

Tensão de iluminação de temperatura de polarização negativa

- PBTS:

-

Estresse de temperatura de polarização positiva

- SiNx:

-

Nitreto de silício

- SiOx:

-

Óxido de silício

- SS:

-

Balanço de sublimiar

- TFT:

-

Transistor de filme fino

- TN LCD:

-

Visor de cristal líquido nemático torcido

Nanomateriais

- Usando tecnologias sem água no processo de tingimento

- Chave de seleção de inicialização de hardware usando Pico

- Usando a eficácia geral do equipamento

- Estratégias para gerenciar o desempenho de ativos

- Usando o gerenciamento de desempenho de ativos para maximizar o valor do ativo

- Engenharia de processo de revestimento por imersão e otimização de desempenho para dispositivos eletrocrômicos de três estados

- Composto Híbrido de Sílica Nanoestruturada / Ouro-Celulose Ligado Amino-POSS via Processo Sol-Gel e Suas Propriedades

- Fabricação de estruturas periódicas 3D baseadas em nanoconcha por processo de modelagem usando ZnO derivado de solução

- Usando uma impressora 3D para melhorar seu processo de fabricação - Vídeo

- Vantagens de usar VIA em eletrodos