Dispositivo LVTSCR robusto e imune a travamento com um PMOSFET incorporado para proteção ESD em um processo CMOS de 28 nm

Resumo

Espera-se que o retificador controlado por silício acionado por baixa tensão (LVTSCR) forneça uma proteção contra descarga eletrostática (ESD) para um circuito integrado de baixa tensão. No entanto, é normalmente vulnerável ao efeito de travamento devido à sua tensão de retenção extremamente baixa. Neste artigo, um novo LVTSCR incorporado com um MOSFET tipo p extra denominado EP-LVTSCR foi proposto e verificado em uma tecnologia CMOS de 28 nm. O dispositivo proposto possui uma tensão de disparo mais baixa de ~ 6,2 V e uma tensão de retenção significativamente mais alta de ~ 5,5 V com apenas 23% de degradação da corrente de falha no teste de pulso da linha de transmissão. Também é mostrado que o EP-LVTSCR opera com uma resistência de ativação inferior de ~ 1,8 Ω, bem como uma corrente de fuga confiável de ~ 1,8 nA medida a 3,63 V, tornando-o adequado para proteções ESD em 2,5 V / 3,3 V CMOS processos. Além disso, o mecanismo de disparo e as características de condução do dispositivo proposto foram explorados e demonstrados com simulação TCAD.

Histórico

Com a miniaturização contínua do tamanho do recurso dos dispositivos semicondutores, o dano induzido por descarga eletrostática (ESD) nos circuitos integrados (IC) se tornou um problema mais sério. Além disso, o custo de fabricação do dispositivo de proteção ESD aumentou drasticamente devido à tecnologia de processo avançada [1]. Portanto, os projetos de dispositivos de proteção ESD de alta eficiência e robustez são de grande valor.

Um dispositivo retificador controlado de silício (SCR) foi verificado para sustentar uma alta corrente ESD com uma pequena dimensão de dispositivo devido ao efeito de feedback fortemente positivo em seus transistores de junção bipolar parasita [2]. Mas o SCR normalmente tem uma alta tensão de disparo ( V t1 ) que excede a tensão de ruptura do óxido de porta do estágio de entrada na tecnologia CMOS em nanoescala. Para reduzir o V t1 de SCR, o SCR lateral modificado (MLSCR) foi relatado para proteção ESD de entrada inserindo n + fortemente dopado ou p + regiões através do limite de n-well e p-well [3, 4]. Mas a tensão de disparo do MLSCR ainda é maior do que as tensões de ruptura dos transistores de saída no buffer de saída do CMOS. Portanto, ele não pode fornecer uma proteção ESD de saída eficiente sozinho.

Para proteger com eficiência o buffer de saída do CMOS, um SCR disparado por baixa voltagem (LVTSCR) foi proposto pela inserção de um dispositivo NMOS de canal curto (PMOS) no SCR tradicional para realizar uma voltagem de disparo muito mais baixa [5,6,7] , que é equivalente à tensão de disparo de snapback do dispositivo NMOS (PMOS) inserido. No entanto, como os dispositivos SCR e MLSCR tradicionais, o LVTSCR também sofre os riscos de travamento devido à sua tensão de retenção extremamente baixa (V h ) de cerca de 2 V [8]. Tal efeito de travamento resultará em um mau funcionamento durante a operação normal e uma alta corrente incessante para destruir o IC [9].

Existem vários métodos possíveis para melhorar o V h do LVTSCR [10,11,12,13,14,15]. A solução mais comum é expandir a região de base dos transistores de junção bipolar parasita do SCR (BJT) para diminuir a eficiência de injeção de suas junções de base de emissor [10]. Adotando essa solução, não apenas a área de layout do dispositivo aumentará, mas também a resistência à ativação ( R em ) deveria, também, o que levará ainda mais à degradação drástica de sua corrente de falha ( I t2 ) Em seguida, um método otimizado foi proposto pela inserção de uma região flutuante-n-bem em LVTSCR com menos sacrifício em I t2 [11], mas também opera com um grande R em levando uma tensão de condução exorbitante que excede a tensão de ruptura do óxido de porta contra uma pequena corrente, reduzindo assim sua corrente de proteção ESD efetiva. O método adicionando as camadas N-LDD / P-HALO extras em LVTSCR também pode elevar o V h [12], enquanto tais dispositivos são compatíveis apenas para o processo específico e não podem ser amplamente utilizados em processos CMOS comuns. Além disso, um LVTSCR disparado por NMOS (GGSCR) foi relatado em [13], o que aumenta o V h conduzindo o dreno do NMOS embutido para o ânodo, mas pode fazer com que o NMOS embutido seja danificado antes da condução do SCR em uma corrente baixa. Recentemente, as estruturas LVTSCR compostas com baixo V t1 bem como alto V h foram demonstrados em [14, 15]. Essas estruturas compostas são projetadas com alta complexidade e requisitos de área, limitando assim sua aplicação em tecnologia CMOS avançada considerando os custos de projeto. Portanto, um dispositivo de proteção ESD robusto, com eficiência de área e imune a travamento é altamente desejável na proteção ESD de processo avançado.

Neste artigo, uma nova estrutura LVTSCR com um transistor PMOS embutido (EP-LVTSCR) é proposta para aplicações de tensão de alimentação de 2,5 V / 3,3 V. O dispositivo proposto foi fabricado em um processo CMOS de 28 nm, e sua característica elétrica é verificada através da medição do pulso da linha de transmissão (TLP). Os mecanismos físicos do dispositivo proposto são explorados por meio de simulações de tecnologia de design auxiliado por computador (TCAD). Como resultado, a estrutura proposta possui uma maior tensão de retenção, uma menor tensão de disparo com um menor R em , e apenas uma ligeira diminuição em I t2 sem nenhuma etapa extra do processo.

Métodos

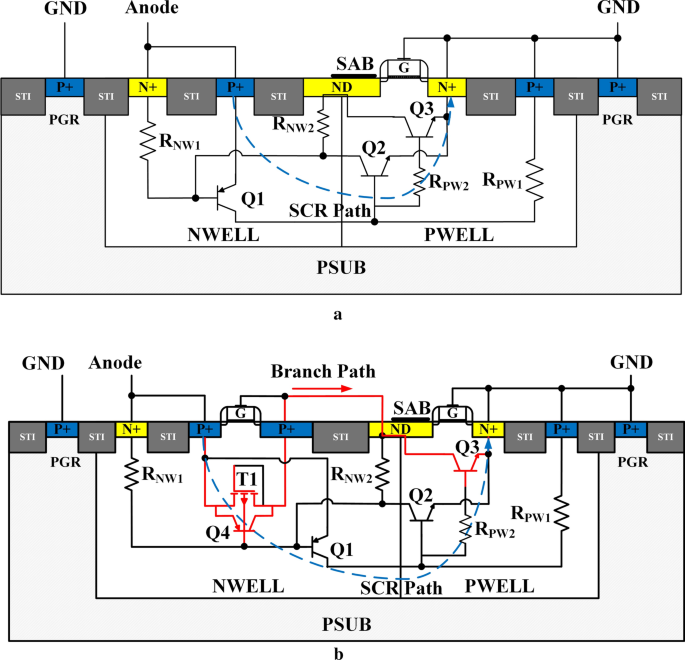

O LVTSCR convencional e o EP-LVTSCR proposto foram estudados neste artigo. As vistas esquemáticas em corte transversal do LVTSCR convencional e EP-LVTSCR são mostradas na Fig. 1a, b, respectivamente, enquanto seus circuitos equivalentes são representados dentro das estruturas com os transistores parasitas e resistores de poço. Em ambos os dispositivos, camadas de bloco de siliceto (SAB) são colocadas no topo da região ND parcial, o que induzirá resistências de lastro, evitando a formação de camadas de siliceto [16, 17]. No LVTSCR convencional, um transistor NMOS é inserido no PWELL com sua configuração de dreno (ND) entre NWELL e PWELL, enquanto sua fonte e porta são conectadas ao terra (GND) juntos, o que pode ser visto na Fig. 1a. Durante o estresse ESD, o BJT p-n-p lateral parasita (Q1) e os BJTs n-p-n laterais parasitas (Q2 e Q3) serão gradualmente ativados. Em tal condição, os transistores Q1 e Q2 são acoplados para constituir o caminho de condução de SCR que irá predominar na descarga de corrente, onde o caminho de condução de SCR é indicado pela linha tracejada.

Vista transversal de a o LVTSCR convencional e b o EP-LVTSCR proposto

Comparado com o LVTSCR convencional, o EP-LVTSCR tem um transistor PMOS extra (T1) embutido no NWELL, pois sua porta e dreno são conectados ao ND com um metal, que é mostrado na Fig. 1b. Quando um pulso ESD é aplicado ao ânodo do EP-LVTSCR, o diodo N + / NWELL / N + / PWELL / P + com polarização reversa conduzirá primeiro se a tensão de zapping for superior à tensão de ruptura N + / PWELL. Então, os buracos / elétrons gerados pelo efeito multiplicador de avalanche irão fluir em direção ao cátodo / ânodo, aumentando assim a densidade de corrente em NWELL / PWELL e elevando ainda mais o potencial de queda através do NWELL / PWELL. Assim que a tensão total cair em R NW1 e R NW2 , que é equivalente à queda de tensão entre a fonte e a porta (- V gs ) de T1, supera sua tensão limite ( V th ) de cerca de 0,9 V, o T1 será ligado. Subseqüentemente, os transistores n – p – n parasitas laterais Q2 e Q3 serão acionados com base na condução de suas junções emissor-base. Percebe-se que a condução de T1 irá diminuir o R em através do NWELL e, portanto, Q2 e Q3 podem ser acionados em tensões mais baixas. À medida que a corrente continua a aumentar, a queda de tensão em R NW1 sobe para cerca de 0,7 V e liga o Q1 e o transistor p – n – p lateral parasita do PMOS (Q4). Finalmente, o caminho do SCR liga-se à condução do caminho do ramal.

Vários relatórios demonstraram que a tensão de retenção do SCR é principalmente determinada pela diferença de potencial através da região de depleção NWELL / PWELL V dep [18,19,20], que é inversamente proporcional aos portadores minoritários (elétrons / lacunas) injetados na região de depleção. Enquanto o caminho de ramificação de EP-LVTSCR pode extrair buracos / elétrons injetados na região de depleção do caminho de SCR, elevando assim o V h de EP-LVTSCR.

A fim de demonstrar ainda mais o mecanismo físico de EP-LVTSCR, simulação TCAD foi realizada, onde os modelos físicos como mobilidade, recombinação, termodinâmica e densidade intrínseca efetiva foram integrados e os métodos matemáticos como extrapolar, RelErrcontrol e corrente contínua computação foram usados. A modelagem de corrente ESD por pulsos de 1,2 A com tempo de subida de 10 ns foi aplicada aos ânodos de EP-LVTSCR e LVTSCR convencional, respectivamente, onde o substrato dos dispositivos foi considerado como o único dissipador de calor e a temperatura ambiente foi definida como 300 K.

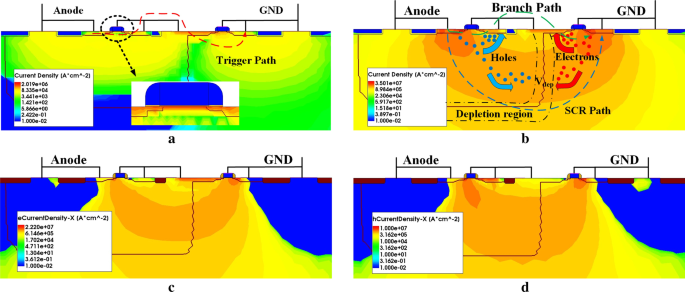

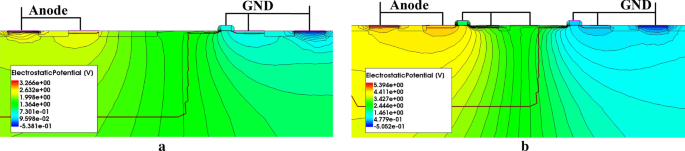

Os resultados simulados das distribuições de densidade de corrente total de EP-LVTSCR a 500 ps e 5 ns são mostrados na Fig. 2a, b, respectivamente. A 500 ps, a distribuição de densidade de corrente se concentra nos transistores T1 e Q2, o que indica que a série T1 / Q2 foi ativada como um caminho de disparo mostrado na Fig. 2a. Quando o tempo sobe para 5 ns, tanto o caminho SCR quanto o caminho do ramal foram conduzidos, como pode ser observado na Fig. 2b. Neste momento, parte dos buracos / elétrons gerados por P + / N + são extraídos de NWELL / PWELL para fluir através do caminho do ramal, que são ilustrados pelos buracos horizontais e densidade de corrente de elétrons da estrutura proposta mostrada na Fig. 2c, d . Além disso, as distribuições de potencial eletrostático do LVTSCR convencional e EP-LVTSCR a 5 ns são comparadas na Fig. 3a, b. Obviamente, o pico potencial dentro do EP-LVTSCR é maior. Estes resultados de simulação fornecem evidência direta para a suposição acima da tensão de retenção mais alta de EP-LVTSCR resultante do caminho de ramificação indicado na Fig. 1b.

Simulado por TCAD a distribuição da densidade de corrente total em t =500 ps, b distribuição de densidade de corrente total em 5 ns, c distribuição horizontal de densidade de corrente de elétrons em 5 ns e d distribuição de densidade de corrente de furos horizontais em 5 ns do EP-LVTSCR proposto sob uma tensão de 1,2A-TLP

Distribuições de potencial eletrostático simulado por TCAD de a o EP-LVTSCR proposto e b o LVTSCR convencional em t =5 ns sob uma tensão de 1,2A-TLP

Resultados e discussão

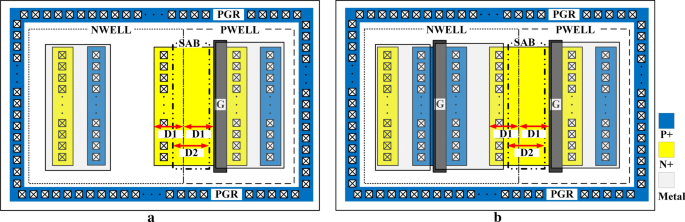

O LVTSCR convencional e o EP-LVTSCR são implementados em um processo CMOS lógico de 2,5 V / 3,3 V de 28 nm com a mesma largura de 40 um, e suas topologias de layout são mostradas na Fig. 4a, b, respectivamente. Para evitar os efeitos parasitários associados ao substrato, anéis de guarda do tipo P (PGR) são empregados em ambas as estruturas, e cada PGR é conectado ao GND [21]. O eixo central de ND está alinhado com a junção NWELL / PWELL, e o parâmetro D1 é usado para descrever metade do comprimento de ND, enquanto D2 é o comprimento da região SAB.

Topologias de layout de a o LVTSCR convencional e b o EP-LVTSCR proposto

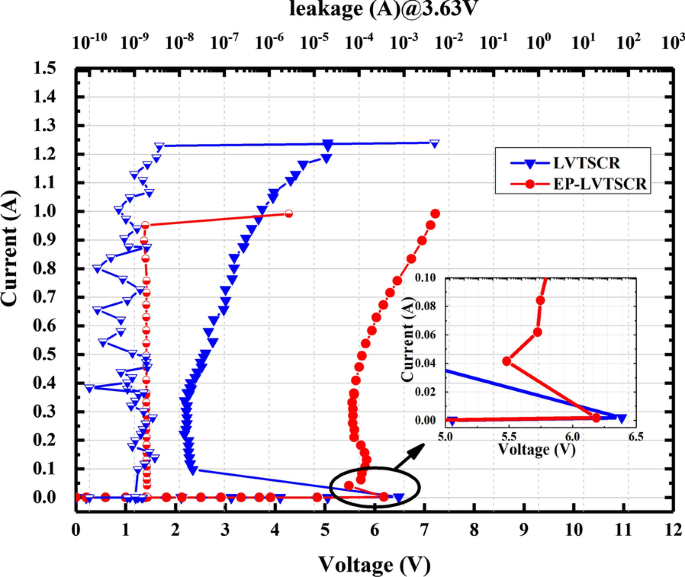

As características ESD do LVTSCR convencional e EP-LVTSCR foram medidas usando o testador Hanwa TED-T5000 TLP com tempo de subida de 10 ns e largura de pulso de 100 ns, e as correntes de fuga foram medidas sob polarização de tensão de 3,63 V (1,1 * VDD) após cada Estresse TLP. O TLP I – V medido e as características de vazamento do EP-LVTSCR e LVTSCR são mostrados na Fig. 5. Aparentemente, o EP-LVTSCR possui um V superior h de 5,49 V em comparação com o LVTSCR convencional de 2,18 V. Embora o EP-LVTSCR tenha uma melhora significativa na tensão de retenção, seu I t2 apenas diminuiu cerca de 0,29 A, que se beneficia do assistente do caminho da corrente do ramal. Além disso, EP-LVTSCR também executa um V t1 diminuindo de 6,49 para 6,18 V. Para pinos IO de 2,5 V ou 3,3 V em processos CMOS de 28 nm, a janela de design ESD variou de 3,63 a 9,4 V com consideração de margem de segurança de 10%. Portanto, o EP-LVTSCR proposto pode ser usado como uma solução de proteção ESD válida para portas IO 2,5 V / 3,3 V, superando o problema de travamento em uma estrutura tradicional do tipo LVTSCR.

TLP I – V medido e correntes de fuga de EP-LVTSCR e LVTSCR convencional com a mesma área de matriz

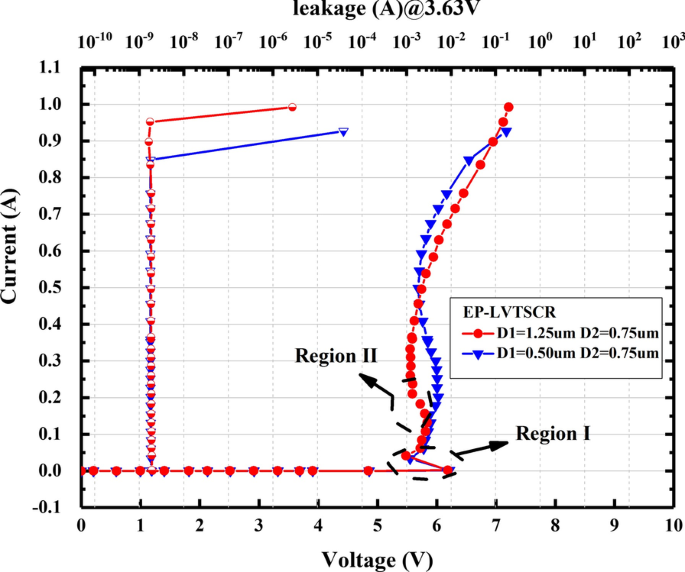

Neste artigo, as características elétricas da proteção ESD proposta foram otimizadas através da modificação das variáveis de projeto D1 e D2. A Figura 6 ilustra os resultados da medição TLP de EP-LVTSCRs com dois D1 diferentes. Percebe-se que as curvas I – V de EP-LVTSCRs apresentam duas regiões de snapback devido aos efeitos de multi-trigger durante a ativação dos dispositivos. O primeiro snapback região I sugere a condução do caminho de gatilho que é indicado na Fig. 2a, enquanto o segundo snapback da região II é induzido pela ativação do caminho SCR. Quando D1 diminui de 1,25 para 0,5 um, o I t2 diminui em cerca de 0,1 A e a corrente de retenção no segundo snapback é aumentada em cerca de 0,17 A. Isso ocorre porque as resistências do poço R NW2 e R PW2 (Fig. 1) são diminuídas com a diminuição D1, exigindo, portanto, mais corrente para disparar e manter a condução do SCR.

TLP I – V medido e correntes de fuga de EP-LVTSCR com dois D1 diferentes

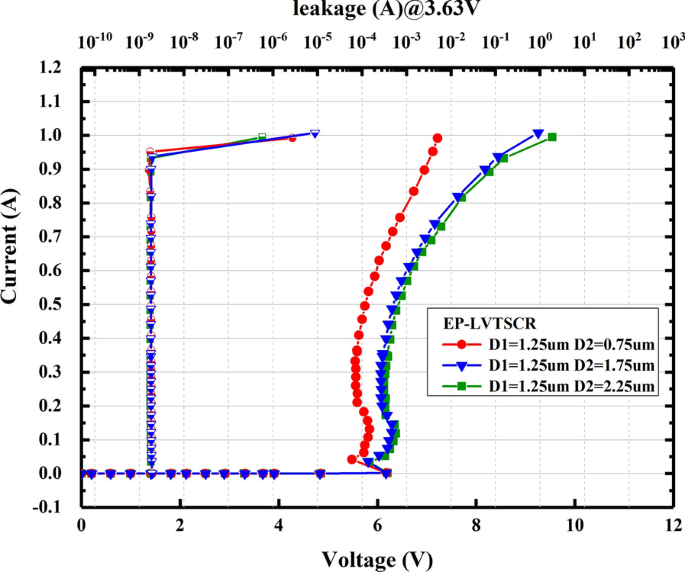

A Figura 7 mostra os resultados de TLP I – V de EP-LVTSCR com três D2 diferentes. Quando D2 aumenta de 0,75 para 2,25 µm, a resistência do lastro de ND aumenta gradualmente, resultando em um aumento na resistência do caminho do ramal e aumento adicional em R em , que pode ser observado pelas variações de inclinação das curvas características IV na Fig. 7. Como resultado, o V h eleva de 5,5 para 5,8 V com o aumento D2 e sem mudanças significativas em I t2 .

TLP I – V medido e correntes de fuga de EP-LVTSCR com três D2 diferentes

Conclusões

Um dispositivo ESD aprimorado chamado EP-LVTSCR foi projetado e fabricado em uma tecnologia CMOS de 28 nm. Os mecanismos dos dispositivos propostos também foram demonstrados com simulações TCAD. Comparado com o LVTSCR convencional, o EP-LVTSCR proposto possui uma tensão de disparo mais baixa de 6,2 V e uma tensão de retenção significativamente mais alta de 5,5 V devido ao seu mecanismo de disparo aprimorado e efeito de condução de ramal. Com um aumento tão maior em V h , a corrente de falha do EP-LVTSCR diminuiu apenas em cerca de 20%. Além disso, a estrutura proposta opera com uma resistência de ativação mais baixa, bem como uma corrente de fuga confiável de cerca de 2 nA na tensão de 3,63 V, por isso é altamente aplicável para proteção de pinos de E / S de 2,5 V / 3,3 V. Além disso, espera-se que os EP-LVTSCRs forneçam proteção ESD em circuitos de energia de 5 V com o benefício de suas características de tensão de retenção ajustáveis.

Disponibilidade de dados e materiais

Todos os dados gerados ou analisados durante este estudo estão incluídos neste artigo publicado.

Abreviações

- ESD:

-

Descarga eletrostática

- SCR:

-

Retificador controlado por silicone

- MLSCR:

-

SCR lateral modificado

- LVTSCR:

-

SCR disparado por baixa tensão

- CMOS:

-

Semicondutor de óxido de metal complementar

- IC:

-

Circuitos integrados

- V t1 :

-

Tensão de disparo

- V h :

-

Retenção de tensão

- BJT:

-

Transistores de junção bipolar

- R em :

-

Resistência ao ligar

- I t2 :

-

Corrente de falha

- TLP:

-

Pulso da linha de transmissão

- TCAD:

-

Tecnologia de design auxiliado por computador

- SAB:

-

Bloco de silicídio

- V th :

-

Tensão de limiar

- DC:

-

Corrente direta

Nanomateriais

- Um resumo sobre tecnologia IC para microcontroladores e sistemas incorporados

- Maxim:transceptor IO-Link duplo com regulador DC-DC e proteção contra surtos

- Design integrado com FPGAs:Processo de desenvolvimento

- TRS-STAR:sistemas incorporados robustos e sem ventoinha de avalue

- Engenharia de processo de revestimento por imersão e otimização de desempenho para dispositivos eletrocrômicos de três estados

- Uma SRAM 4T integrada RRAM com carga de comutação resistiva autoinibida por processo lógico CMOS puro

- Uma nova microestrutura de cluster de nanocônios com propriedades anti-reflexo e superhidrofóbicas para dispositivos fotovoltaicos

- Dispositivo multifuncional com funções selecionáveis de absorção e conversão de polarização na faixa Terahertz

- Automação e segurança cibernética:proteção completa para clientes

- Materiais e design de PCB para alta tensão