Uma SRAM 4T integrada RRAM com carga de comutação resistiva autoinibida por processo lógico CMOS puro

Resumo

Este artigo relata uma nova memória de acesso aleatório não volátil 4T2R totalmente lógica compatível (nv-SRAM) com seu mecanismo de armazenamento de dados autoinibido para aplicações SRAM de baixa potência / alta velocidade. Com área de célula compacta e compatibilidade lógica total, esta nova nv-SRAM incorpora duas STI-ReRAMs embutidas na SRAM 4T. Os dados podem ser lidos / gravados por meio de uma estrutura volátil de par cruzado para manter a velocidade de acesso rápido. Os dados podem ser armazenados de forma não volátil em uma nova célula SRAM por meio de uma operação de auto-inibição exclusiva na carga da memória de acesso aleatório resistiva (RRAM), alcançando energia estática zero durante a retenção de dados.

Histórico

Nos últimos anos, várias memórias de acesso aleatório estático de baixa potência foram desenvolvidas para atender a necessidade de sistemas de computação em dispositivos portáteis e aplicações IOT [1,2,3,4,5,6]. À medida que a tecnologia CMOS se reduz ao regime de nanômetro, a corrente de fuga no estado desligado aumenta drasticamente, o que leva a piorar o consumo de energia estática para módulos de memória volátil [7, 8]. O consumo de energia estática aumentado pela corrente de fuga em transistores com escala nano se tornou um dos principais desafios para o avanço das SRAMs de baixa potência. [9,10,11]. Ao longo dos anos, diferentes estruturas celulares ou técnicas de operação [12,13,14,15,16] foram propostas para minimizar o consumo de energia em SRAMs. Algumas das células recentemente propostas incorporam elementos de armazenamento não voláteis, como memória de acesso aleatório resistiva (RRAM) e memória de acesso aleatório magnetorresistiva (MRAM) [17,18,19,20], para atingir o poder de retenção zero, mantendo baixa operação poder e velocidade de acesso rápido no processamento de dados voláteis. No entanto, adicionar elementos de armazenamento não voláteis em matrizes SRAM baseadas em lógica geralmente requer camadas e / ou processos adicionais para as plataformas lógicas padrão [21,22,23]. Isso inevitavelmente aumentará a complexidade do processo para seu desenvolvimento. Além disso, esses RRAMs e MRAMs baseados em back-end requerem uma grande estrutura de conexão, composta de múltiplas pilhas de vias e metais para as células SRAM. Essas estruturas de ponte aumentam a capacitância parasita para o nó de armazenamento de dados SRAM, afetando a velocidade de acesso dessas células SRAM não voláteis [24, 25]. Em nosso trabalho anterior [26], uma nova SRAM 4T nv de potência estática zero com RRAMs de parede lateral STI localizados próximos aos nós de armazenamento flutuantes da SRAM 4T foi proposta em primeiro lugar. Nesta carta, este 4T2R nv-SRAM com armazenamento de dados não voláteis, potência zero-holding e velocidade de acesso rápido será analisado e otimizado para aplicativos NVM incorporados.

Métodos

Estrutura da célula STI-ReRAM

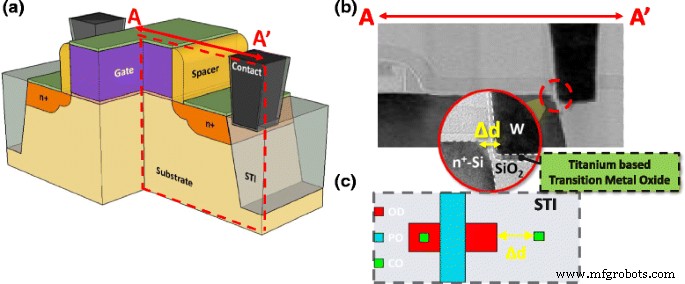

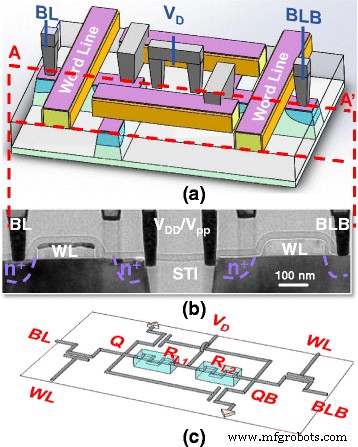

Na estrutura 3D STI-RRAM na Fig. 1a, o nó de armazenamento resistivo é composto por um óxido de metal de transição (TMO) entre dois eletrodos, a região N + e um tampão de tungstênio no lado esquerdo e direito, respectivamente. Conforme mostrado na imagem TEM na Fig. 1b e layout na Fig. 1c, colocando o contato na região STI com a distância adequada para a região N +, o SiO 2 restante e a camada de barreira sob o plugue de tungstênio torna-se filme TMO e apresenta a qualidade de comutação resistiva.

a Ilustração 3D de uma célula 1T1R com STI-ReRAM ao lado da junção n +. b A imagem TEM correspondente do nó de armazenamento resistivo composto de óxidos de metal de transição, formados entre um contato especialmente colocado e a região n + do transistor selecionado. c Layout

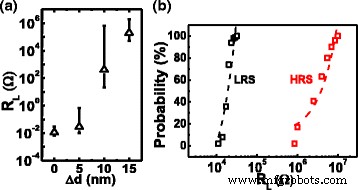

A espessura de TMO pode ser controlada escolhendo um espaçamento adequado Δd entre um contato e a região de difusão N +. Com base na medição da Fig. 2a, existe uma correlação positiva entre o nível de resistência inicial e a distância traçada, Δd, determinada pelas máscaras que definem o STI e as regiões de contato, respectivamente. Para o estudo a seguir, RRAM com Δd igual a 10 nm é escolhido por sua tensão de formação mais baixa e R L preferencial distribuição no estado de baixa resistência (LRS) e no estado de alta resistência (HRS), conforme resumido na Fig. 2b. Com o controle de tensão de linha de palavra (WL) adequado durante as operações de definição / formação, a corrente definida pode ser fixada localmente pelo transistor selecionado, permitindo melhores desempenhos de resistência.

a A resistência inicial medida de amostras STI-RRAM com diferentes △ d. b Probabilidade cumulativa da resistência de carregamento após reinicialização / definição do STI-RRAM em ambos os estados de resistência alta e baixa

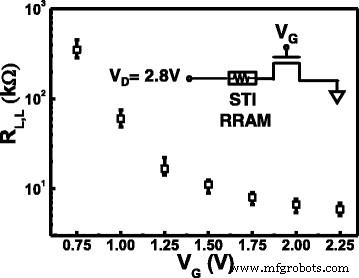

Os dados na Fig. 3 revelam ainda que o nível de corrente lido no LRS pode ser bem controlado pela tensão da porta, V G . Durante a formação em V D =2,8 V, o transistor selecionado limita a corrente máxima que passa pelo STI-RRAM depois que o dispositivo é definido como LRS. O nível de resistência do estado LRS subseqüente é inversamente proporcional à corrente localmente fixada, que foi encontrada em vários dispositivos RRAM baseados em TaO [27, 28].

Correlação entre os níveis de resistência ao carregamento, R L, L , e a tensão de porta aplicada durante o ajuste. Os dados sugerem que diferentes R L, L pode ser obtido definindo um nível diferente de tensão de porta selecionada

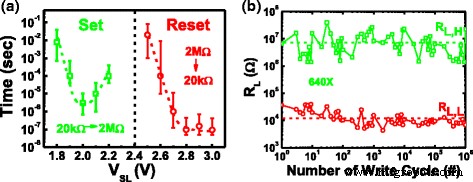

Para garantir as características de chaveamento resistivo do STI-RRAM, o tempo de configuração e o tempo de reinicialização são testados, conforme mostrado na Fig. 4a. As operações de ajuste e redefinição podem ser otimizadas quando V SL =2 e 2,8 V, respectivamente. O teste de resistência RRAM está resumido na Fig. 4b. Usando um algoritmo de programação de pulso de passo incremental, sua janela de leitura pode permanecer estável após 1 milhão de ciclos.

a Tempo de configuração resumido e tempo de reinicialização vs. V PP . b Resultado do teste de resistência de um milhão de ciclos do STI-RRAM usando o algoritmo de Programação Incremental Step Pulse

Conceito SRAM não volátil

A ilustração 3D na Fig. 5 mostra a estrutura da célula 4T2R nv-SRAM proposta recentemente e sua imagem TEM em seção transversal correspondente ao longo da linha de corte AA '. Dois STI-RRAMs servem como nós de armazenamento não voláteis e resistores de carregamento, que são ensanduichados entre as regiões de difusão Q e QB N + e um contato bem próximo nas bordas STI com design de espaçamento adequado. A imagem TEM mostra um STI-RRAM bem formado em ambos os lados esquerdo e direito da região de isolamento e resulta em uma célula bastante compacta com esses nós de armazenamento não voláteis próximos colocados no mesmo nível dos transistores.

a Ilustração 3D da estrutura da célula 4T2R nv-SRAM proposta e o b imagem TEM em seção transversal correspondente. c O esquema do circuito de uma célula SRAM é mostrado com dois resistores RRAM como os dispositivos de carregamento

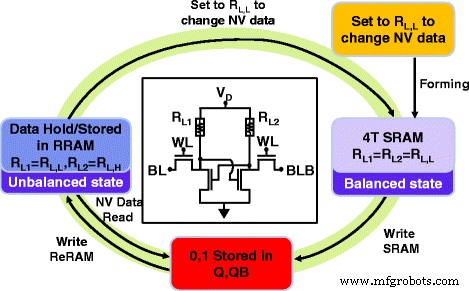

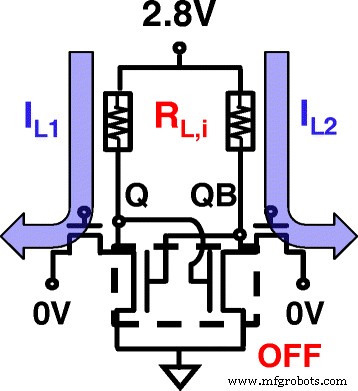

A 4T nv-SRAM proposta pode ser operada em modos voláteis e não voláteis. Seus quatro estados diferentes e seu esquema de operação são ilustrados na Fig. 6.

Esquema do circuito da célula nv-SRAM e seu fluxograma correspondente para alternar entre as operações SRAM voláteis e não voláteis

Em seus estados iniciais, STI-RRAM normalmente carrega um nível de resistência de 10 8 Ω, enquanto o filme TMO está intacto. Por meio de uma operação de formação de cobertor, as células nv-SRAM podem ser inicializadas simultaneamente bloco a bloco em V D =2,8 V. Ambos R L1 e R L2 (resistência de carregamento à esquerda e direita, respectivamente) são inicializados para R L, L . O R L, L final nível de 20 ~ 370 kΩ pode ser controlado fornecendo-se uma tensão WL diferente durante a operação de conformação. A célula então atinge um estado de equilíbrio, o que significa que os dois resistores de carregamento estão no mesmo estado. Neste estado, esta célula pode agora funcionar como a SRAM 4T2R típica, processando dados voláteis de uma forma convencional, armazenando dados na trava de acoplamento cruzado.

Para armazenar os dados de forma não volátil, os dados bloqueados complementares podem ser armazenados nos RRAMs por um mecanismo de auto-inibição herdado nesta célula. Quando os dados são armazenados com sucesso no par RRAM, pode-se desligar a alimentação para manter os dados permanentemente. Para acessar o estado armazenado, basta reaplicar V DD para a matriz. Os dados não voláteis serão restaurados para os nós Q e QB automaticamente e podem ser acessados por meio do modo de leitura SRAM convencional. Finalmente, para atualizar os dados não voláteis, uma operação de conjunto geral é aplicada às matrizes SRAM para que a matriz retorne aos seus estados de equilíbrio.

Resultados e discussão

Análise elétrica

As condições de operação para as transições entre os diferentes estágios estão resumidas na Tabela 1.

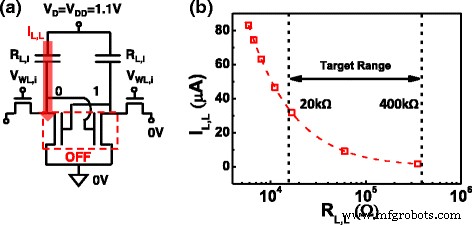

Diferentes R L, L O nível pode ser obtido ajustando-se a voltagem WL diferente durante a inicialização de um bloco ou matriz. Considerando a estabilidade e tensão de operação, o R L, L nível variando entre 20 e 400 kΩ é o primeiro alvo para investigação neste estudo. Tensão WL correspondente de 0,75 a 1,25 V, a resistência de carregamento resultante reduz bastante linearmente, como mostrado na Fig. 3. Como esperado, menor R L, L nível levará a uma corrente de espera mais alta, consulte a Fig. 7. No entanto, R L, L deve permanecer baixo o suficiente para garantir uma grande janela de dados de ampliação entre os dois estados de resistência. Ambas as janelas de dados estáticos, dinâmicos e não voláteis precisam ser considerados para uma maior otimização do alvo R L, L , que é definido pela condição de inicialização.

a Célula 4T2R SRAM na condição de espera. b Como esperado, nível de resistência ao carregamento, I L, L durante a espera pode ser reduzido de forma eficaz, escolhendo um R L, L mais alto

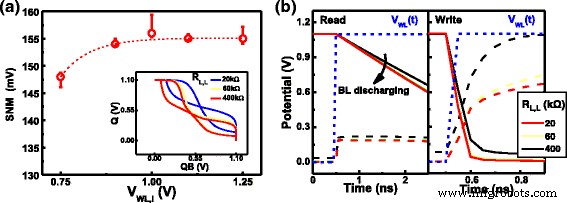

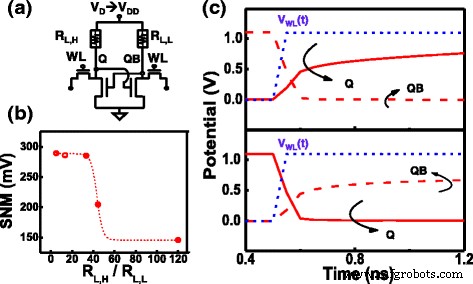

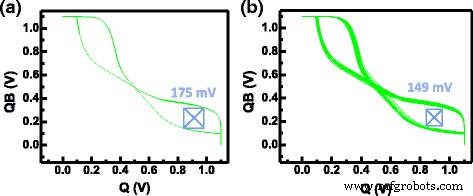

A caracterização estática e dinâmica da nv-SRAM no estado de equilíbrio é primeiramente investigada, considerando células inicializadas por diferentes condições. Na Fig. 8, a margem de ruído estático (SNM) obtida pelas múltiplas curvas borboleta de células inicializadas por diferentes tensões WL. Dados revelam que R L, L nível tem efeito mínimo na margem de leitura de células balanceadas, quando os resistores de carregamento estão dentro da faixa alvo. A distribuição SNM de várias células nos estados de equilíbrio sob diferentes condições de inicialização está resumida na Fig. 8a. SNMs gerais permanecem bastante estáveis de célula para célula, enquanto uma margem de leitura razoável pode ser estabelecida com tensão WL inferior a V DD , o que pode ser benéfico para aplicativos de baixo consumo de energia. Para investigar as características dinâmicas de leitura e gravação desta célula no estado equilibrado, a resposta transitória de gravação “1” e “0” está resumida na Fig. 8b. Verificou-se que R L, L mais alto reduz a velocidade de pull-up para os nós Q, QB, o que pode aumentar ligeiramente o tempo transiente durante as operações de leitura e gravação. No entanto, a velocidade de resposta ainda está dentro da faixa esperada. Os dados acima sugerem que, no estado de equilíbrio, este 4T2R nv-SRAM pode processar dados voláteis como SRAMs convencionais.

a A margem de ruído estático de leitura (SNM) das células SRAM propostas com diferentes tensões WL durante a inicialização. SNM razoável pode ser mantido dentro de uma faixa bastante grande de R L, L de 20 ~ 400 kΩ. b As características dinâmicas de leitura e gravação de uma célula sob condição de carga balanceada revelam um bom tempo de resposta em nanossegundos. Superior R L, L reduz ligeiramente a velocidade de pull-up durante a operação de gravação

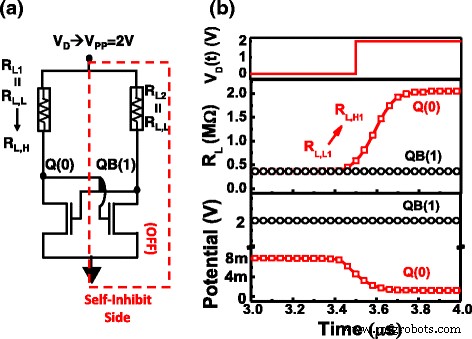

Para armazenar dados no par STI-RRAM, esta célula permite uma reinicialização auto-seletiva de apenas um dos RRAM no par de resistores de carregamento, o que permite que os dados sejam gravados de forma não volátil aplicando um V pp tensão para o nó de alimentação para o bloco de células uniformemente. Uma vez que os dados de trava são armazenados no nó Q e QB, a gravação não volátil é alcançada pelo mecanismo de auto-inibição na estrutura de par cruzado com RRAM, como mostrado na Fig. 9a. Apenas um lado do RRAM com baixa tensão no nó Q será redefinido para R L, H . A corrente no outro ramo é quase zero, pois o transistor pull-down é desligado pelo baixo V Q .

a Ilustração do mecanismo de auto-inibição durante a gravação de dados não voláteis redefinindo um lado de dois RRAMs. b Mudança dinâmica de R L e Q, QB verifica o potencial de auto-inibição de gravação de dados de trava para RRAMs

Os dados são armazenados no par RRAM como V PP pulso é aplicado ao nó de alimentação. Ao gravar dados não voláteis, a comutação dinâmica de R L e a resposta transitória do potencial Q, QB está resumida na Fig. 9b. Os dados de medição sugeriram que para redefinir com sucesso o STI-RRAM seletivamente em um lado, um pulso de 300 ns em V pp =2 V é suficiente. Para garantir que a operação volátil ainda possa ser afetada quando as células estão no estado desequilibrado, conforme a Fig. 10a, a distribuição SNM das células com diferentes R L, H / R L, L razão estão resumidos na Fig. 10b. Verifica-se que a relação de baixa resistência entre os estados não degrada o SNM de retenção. Para garantir que uma célula com uma carga desequilibrada, a gravação dinâmica de dados para tal célula é caracterizada. Os dados revelam que ambos os estados podem ser gravados com sucesso, superando a relação de resistência de desequilíbrio inicial de 2 M / 400 k, conforme mostrado na Fig. 10c.

a Estrutura cruzada durante carga de desequilíbrio. b Margem de ruído estático com diferentes tensões WL durante a inicialização. c Gravação dinâmica para dois estados de dados diferentes. Desequilíbrio R L, L =400 kΩ também pode ser escrito

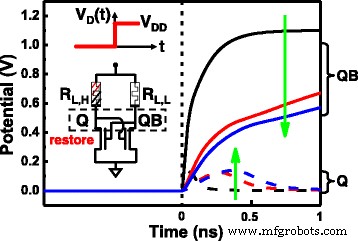

Para carregar os dados voláteis de volta armazenados anteriormente no RRAM, pode-se simplesmente aplicar V DD para o nó de fonte de alimentação, o carregamento de desequilíbrio nos RRAMs será auto-restaurado para os nós de travamento de Q e QB, conforme ilustrado na Fig. 11.

Restauração dos dados não voláteis armazenados em Q e QB a partir de um estado de carga RRAM de desequilíbrio. O potencial de nós Q e QB pode ser restaurado após o retorno da energia em nanossegundos

Efeito parasitário e comparação

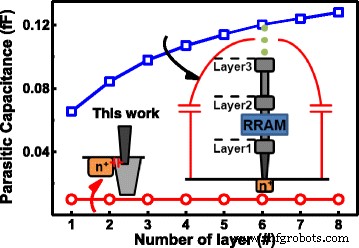

Ao incorporar o STI-RRAM totalmente compatível com a lógica nesta nova célula SRAM, esta célula pode ser facilmente implementada pela maioria dos processos lógicos padrão sem adicionar camadas de máscara, bem como etapas do processo. Este recurso pode aprimorar muito suas aplicações e flexibilidade em vários módulos IP de memória não volátil necessários em muitos sistemas IC. Além disso, o 4T2R nv-SRAM proposto apresenta capacitância parasita muito menor em comparação com outros nv-SRAMs relatados anteriormente [29,30,31] que requerem componentes não voláteis de back-end-of-line (BEOL). Para conectar o nó Q e QB da superfície de Si a esses BEOL RRAM ou MRAMs, várias pilhas de metal e via camadas são necessárias. Essas grandes estruturas de ponte levam a um efeito RC parasitário significativo. A grande capacitância parasitária introduzida nos nós internos dentro das células SRAM pode afetar criticamente o tempo de resposta dos dispositivos.

Para comparar o efeito parasitário sobre estes, nv-SRAMs são investigados com base na estimativa de simulação pós-layout. Assumindo que todas as células são implementadas pela mesma tecnologia CMOS padrão, a capacitância parasita nos nós de trava aumenta à medida que o número de camadas de metal aumenta para células que precisam de grandes estruturas de ponte. Para a nova nv-SRAM usando STI-RRAM, há muito pouco aumento na capacitância geral nos nós travados. Além disso, é independente do número de camadas de metal adaptadas em um determinado circuito. Para investigar melhor o efeito da capacitância parasitária da velocidade SRAM, a resposta dinâmica simulada das células SRAM proposta em [29,30,31] e este trabalho são comparadas na Fig. 12.

Capacitância parasita nos nós de trava de células nv-SRAM da ref [30] e que a partir deste trabalho baseado na tecnologia CMOS de 40 nm, aumento significativo na capacitância parasita é encontrado conforme o número de camadas de metal aumenta

Uma capacitância parasita muito menor desta nv-SRAM incorporada pode levar a um tempo de resposta mais rápido durante a operação de leitura dinâmica na célula SRAM. Isso evita que a grande capacitância interna do impacto da ponte de conexão no tempo de resposta do array SRAM baseado em lógica.

A Tabela 2 compara os principais recursos de SRAMs não voláteis relatados anteriormente incorporados com RRAMs de back-end ou MRAMs e este trabalho. Apesar da tensão de comutação de estado mais alta, a nv-SRAM baseada em STI-RRAM é apresentada com uma capacitância parasita muito menor nos nós internos travados dentro das células SRAM e compatibilidade lógica total.

Degradação da margem de ruído estática induzida por variação

Para garantir o SNM estável com células sujeitas a variações do processo, flutuações nos níveis de resistência RRAM e na tensão de limiar do transistor, V T , são considerados nas seguintes investigações:incompatibilidades em V T é conhecido por causar deslocamento SNM em SRAM por tecnologias escalonadas [32, 33]. Além disso, também pode causar diferentes conjuntos de corrente de conformidade, o que pode, por sua vez, resultar em maior variação no nível de resistência dos dois R L, L . Conforme ilustrado na Fig. 13, diferentes V T levar a uma corrente de conformidade de inicialização diferente na célula STI-RRAM, levando a uma incompatibilidade adicional em R L, L . Para analisar o impacto de V T variação no SNM, assumimos V T ser uma variável aleatória gaussiana com média e variação baseada em relatórios anteriores [34]. Por simulação de Monte-Carlo, a distribuição das curvas borboleta sujeitas a variações em R L, L estão resumidos na Fig. 14a. Quando ambas as variações em R L, L e VT são considerados, um estreitamento significativo da janela SNM é observado, como mostrado na Fig. 14b. O aumento da variabilidade no nv-SRAM precisa ser abordado em estudos futuros.

V T variação leva a conformidade de inicialização diferente I L, 1 e eu L, 2

Curvas borboleta por simulações de Monte-Carlo comparando degradações SNM causadas por a variação em R L, L após a inicialização e b variações em ambos R L, L e V T

Conclusões

Uma nova lógica SRAM não volátil baseada em 4T2R STI-RRAM, totalmente compatível com o processo de lógica CMOS, foi demonstrada com sucesso no processo de lógica CMOS puro em um nó de tecnologia de 40 nm sem máscaras ou etapas extras. Esta célula nv-SRAM apresenta mecanismo de auto-inibição e auto-restauração para dados não voláteis, pequena capacitância parasita em nós de travamento e energia estática zero durante a retenção de dados. Essas características superiores tornam a nv-SRAM baseada em STI-RRAM uma solução promissora para aplicações de memória não volátil lógica de baixa potência / alta velocidade no futuro.

Nanomateriais

- Introdução aos circuitos integrados digitais

- Circuitos integrados

- Lógica digital com feedback

- Circuitos de troca de diodo

- Energia em circuitos resistivos e reativos CA

- Correção prática do fator de potência

- Modelo de retenção de TaO / HfO x e TaO / AlO x RRAM com características de chave auto-retificadora

- Características de chaveamento resistivo bipolar de dispositivos RRAM de estrutura tricamada de HfO2 / TiO2 / HfO2 em substratos revestidos com Pt e TiN fabricados por deposição de camada atômica

- Memória resistiva ZrO2 / ZrO2 - x / ZrO2 sem conformidade com comportamento de comutação multiestado interfacial controlável

- Mecanismo de condução e resistência aprimorada em RRAM baseado em HfO2 com tratamento de nitridação