Projeto e implementação de placas de comutação de interconexão FDR de alta densidade

Atualmente, a taxa de transmissão da rede de interconexão de computadores de alto desempenho com a aplicação de transmissão serial de alta velocidade se desenvolveu em FDR (Fourteen Data Rate, 14Gb/s), a 4ª geração do SDR primário (Single Data Rate, 2,5Gb/s). s), DDR (Double Data Rate, 5Gb/s) e QDR (Quad Data Rate, 10Gb/s). O projeto de PCB (Placa de Circuito Impresso) com interconexão e placa de comutação e placas de interface que são essenciais para a formação da Internet entrou no campo FDR de alta velocidade e alta frequência. Desde que o tempo de subida do sinal FDR reduziu drasticamente para a magnitude de 10ps, uma série de problemas relacionados à integridade do sinal tornaram-se os principais recursos para determinar a possibilidade de implementação de funcionalidade e operação confiável, como atenuação, diafonia, reflexão, interferência eletromagnética etc. Com base nos recursos dos chips de interconexão FDR, incluindo várias portas, vários canais, várias categorias de energia e alto consumo de energia, vários chips de interconexão sempre precisam ser integrados em uma única placa de interconexão para aumentar a taxa de transferência. Em uma placa com espaço limitado, por um lado, alguns requisitos devem ser atendidos, incluindo layout de componentes e dissipação de calor, roteamento com alta densidade, transmissão de longa distância na parte traseira da placa e integridade de todos os tipos de sinais. Por outro lado, alguns elementos devem ser levados em consideração, incluindo o período de projeto do PCB, limitações da técnica de fabricação do PCB e controle de custos. Portanto, é extremamente difícil para a implementação do projeto e verificação da simulação. Com base no exemplo de projeto de PCB de interconexão FDR e placa de comutação, este artigo traz alguns métodos de otimização em termos de seleção de material de substrato, design de empilhamento, regras de roteamento e design anti-interferência para resolver o problema de integridade de todos os tipos de sinais em o processo de design de PCB de alta velocidade FDR.

Atributo de atenuação e seleção de material de substrato

Para sinais FDR de alta frequência, a perda da linha de transmissão é o problema relacionado à integridade do sinal. Quando os sinais FDR são transmitidos do terminal de transmissão para o terminal de recepção ao longo dos canais de interconexão, porque a atenuação de alta frequência é muito maior do que a atenuação de baixa frequência, ocorre uma séria deformação na forma de onda do sinal que chega ao terminal de recepção. A deformação é classificada principalmente em dois aspectos:a oscilação de tensão dos sinais diminuiu bastante, enquanto a degradação ruim ocorreu na borda de subida do sinal. O primeiro limita a distância de transmissão dos sinais, enquanto o segundo leva à interferência entre os códigos. A perda da linha de transmissão A pode ser considerada como a soma da perda do condutor Acond e perda dielétrica Adiel conforme mostrado na Fórmula (1):A =Adiel + Acondição .

A perda do condutor refere-se à perda causada pelo resistor serial no condutor de cobre entre o caminho do sinal e o caminho de retorno. Na situação de alta frequência, o efeito pelicular faz com que a corrente flua na superfície dos condutores de cobre circundantes. Com o aumento da resistência serial equivalente dos condutores de cobre, a perda do condutor aumentará com o aumento da frequência que é positiva proporcional à raiz quadrada da frequência, que é ilustrada na Fórmula (2):

.

. A perda dielétrica refere-se à perda gerada pelo meio do material do substrato, determinada principalmente pelo atributo do material e não relacionada à construção geométrica, incluindo a largura do condutor, positiva proporcional à frequência, que é mostrada na Fórmula (3):

.

. Com base na Fórmula (2), o aumento da largura da linha é capaz de reduzir a perda do condutor. No entanto, no projeto prático de PCB, a largura dos condutores nunca pode ser indefinidamente ampla como resultado da limitação do espaçamento entre pinos, placa, número de camadas de sinal e impedância. A largura/espaçamento/largura do condutor comumente aplicado no design FDR é geralmente 7mil/7mil/7mil ou 8mil/10mil/8mil. Quando a largura do condutor é a mesma, a perda do condutor é positiva proporcional ao comprimento do condutor, sem qualquer relação com o material. Portanto, para reduzir a perda geral de transmissão, apenas a perda dielétrica deve ser levada em consideração. Com base na Fórmula (3), a perda dielétrica é proporcional ao fator de dissipação e a aplicação de pequenos fatores de dissipação pode ser útil para a redução da perda dielétrica, levando à perda da transmissão geral.

A Tabela 1 lista os parâmetros de atributo de três materiais comuns de placa de alta velocidade e valores de perda calculados de acordo com a Fórmula (1), (2) e (3) quando a taxa de transmissão é 14Gb/s, largura do condutor 8mil e impedância 50Ω.

| Parâmetros do material da placa | FR4 | Nelco4000-13SI | Megtron6 |

| [email protected] | 0,02 | 0,008 | 0,004 |

| [email protected] | 4.10 | 3.200 | 3.600 |

| Umacondição @7GHz/in | 0,24 | 0,240 | 0,240 |

| Umdiel @7GHz/in | 0,65 | 0,230 | 0,120 |

| [email protected]/in | 0,89 | 0,470 | 0,360 |

| [email protected]/30in | 27,00 | 14.000 | 11.000 |

| Custo Relativo | 1,00 | 3.500 | 8.000 |

Pode ser indicado que com a taxa de transmissão de 14 Gb/s e comprimento de transmissão de 30 polegadas, a perda total de transmissão do Nelco4000-13SI é de aproximadamente 14 dB, enquanto a atenuação de oscilação de tensão que o chip FDR típico pode suportar está na faixa de 20 dB a 25dB. Portanto, este tipo de material de placa pode ser aplicado em design de placa de interruptor de interconexão FDR com distância de transmissão inferior a 30 polegadas. No entanto, a atenuação geral da transmissão do FR4 é de aproximadamente 27dB e o FR4 não pode ser aplicado para o projeto FDR de projeto de longa distância, mas as placas de interface de interconexão FDR com curta distância de transmissão podem selecionar FR4 para reduzir o custo. Já o Megtron6, cuja atenuação geral de transmissão é a menor, apresenta o maior custo e sua aplicação em FDR leva ao aumento das taxas de arquitetura do sistema. Em conclusão, para PCB de alta frequência, o material da placa é a base e a seleção do material da placa determina o comprimento de transmissão dos sinais.

Layout e design de pilha

Para o projeto de PCB, a estrutura e a pilha da placa de circuito devem ser levadas em consideração primeiro. Normalmente, o padrão e a forma da placa de circuito foram determinados e a determinação do número da pilha está na frequência do sinal, densidade de pinos da placa de circuito, custo de fabricação de PCB, período de fabricação e requisitos de confiabilidade. As placas de interconexão FDR possuem alta frequência e densidade e a aplicação de placas multicamadas é o passo necessário para reduzir a interferência. Além disso, a determinação do número da pilha é crucial.

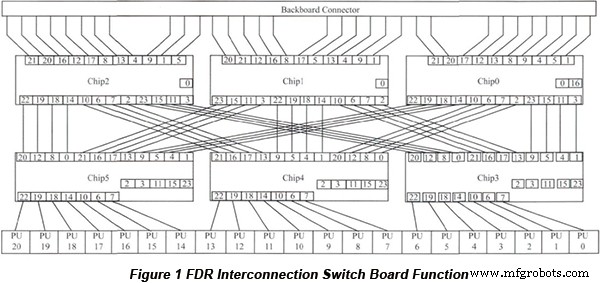

Existem 24 portas no chip de interconexão FDR e cada porta possui 8 canais Tx e 8 canais Rx no método de operação de interconexão. 6 chips de interconexão e 3 chips de downlink são aplicados pela placa de interconexão FDR e 32 portas são acessadas através do conector da placa traseira. 3 chips de uplink acessam 21 portas através de fibras ópticas QSFP (Quad Small Form-factor Pluggable). O chip de uplink e o chip de downlink estão conectados entre si por meio de 4 portas, mostradas na Figura 1.

O FDR apresenta o pacote de BGA (Ball Grid Array) com área de 50mmx50mm, 1157 pinos e espaçamento de 1,0mm e os pinos P/N nas portas de Tx e Rx são distribuídos de acordo com 3 círculos concêntricos. Teoricamente, 3 camadas de sinal podem ser aplicadas para conduzir todos os pinos em todas as portas para fora do BGA. Com os dois elementos a seguir considerados, duas camadas de sinal podem ser usadas para acessar um grupo de pinos de círculos concêntricos.

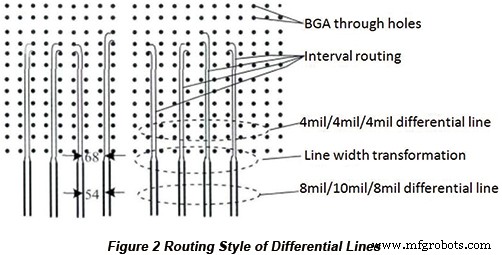

a. Devido à limitação do espaçamento, a largura da linha/espaçamento/largura das linhas diferenciais é de 4mil/4mil/4mil e será expandida para 8mil/10mil/8mil saindo do BGA e a distância entre os pares de linhas diferenciais não deve ser menor que 50mil. Portanto, um par de linhas diferenciais deve ocupar uma largura de 2 mm e 48 pares de sinais estão ao longo da borda com a maior densidade. Portanto, é difícil implementar esse método.

b. O espaçamento entre os pinos BGA é de 1 mm. Se uma camada de sinal for aplicada para acessar um grupo de sinais de círculo concêntrico, o espaçamento entre os pares de linhas diferenciais sob BGA é de apenas 14mil, longe dos 50mil necessários. Além disso, o comprimento máximo de roteamento paralelo é de apenas 20 mm, o que gerará alguma interferência.

Para evitar os fatores negativos mencionados acima, duas camadas de sinal são aplicadas para acessar um grupo de sinais circulares concêntricos e o sinal diferencial em cada camada de sinal deve ser conduzido para fora do BGA de acordo com o espaçamento de 50mil. Portanto, pelo menos 6 camadas são exigidas pelas placas de interconexão FDR para fazer com que todos os sinais diferenciais sejam conduzidos para fora do BGA. Com a conectividade e a quantidade de roteamento da placa e a superfície da placa suficiente para o capacitor de acoplamento de troca considerados, 8 sinais internos e uma pilha de 22 camadas são aplicados.

Análise cruzada e medidas de redução

Crosstalk é a primeira consideração em termos de projeto de circuito de alta velocidade e alta densidade. Quando a tensão e a corrente na linha ofensiva mudam, o acoplamento eletromagnético ocorrerá através de capacitância mútua e indutância mútua entre a linha ofensiva e a linha vítima. A diafonia que flui em direção ao terminal de transmissão ao longo da linha vítima é chamada de diafonia próxima ao terminal, enquanto a diafonia fluindo em direção ao terminal receptor ao longo da linha vítima é chamada de diafonia terminal distante. De um modo geral, a tensão geral do ruído na linha vítima deve ser controlada em menos de 5% da tensão do sinal. É melhor controlar o orçamento de crosstalk da linha ofensiva de borda única dentro de 1% com outra fonte de ruído e linha ofensiva em torno de dois lados da linha da vítima considerados.

Os pontos-chave a seguir em termos de redução de crosstalk incluem:

a. O espaçamento entre a linha ofensiva e a linha da vítima deve ser aumentado e o comprimento do roteamento paralelo deve ser diminuído.

b. O aterramento integrado é aplicado para ser o caminho de retorno dos sinais. De acordo com a lei empírica, para a linha de tira de 50Ω, quando o espaçamento é três vezes a largura da linha, a diafonia próxima é de aproximadamente 0,5%. Para linha de microfita de 50Ω, quando o espaçamento é três vezes a largura da linha, a diafonia próxima é de aproximadamente 1%. A diafonia de extremidade distante em linhas de tira ou linhas de microfita totalmente incorporadas é quase zero e a polaridade de diafonia de extremidade distante de linhas de transmissão de microfita é negativa com sua magnitude relativamente grande porque a influência do acoplamento indutivo é maior que o acoplamento capacitivo.

• Roteamento de intervalo

Neste projeto, a impedância diferencial da linha diferencial de alta velocidade é de 100Ω. Com base no solucionador de campo Si9000, a largura/espaçamento/largura da linha é calculada em 8mil/10mil/8mil. Quanto mais larga a linha, menor é a atenuação e o espaçamento de 10mil é para manter a impedância diferencial de 100Ω. Este tipo de linha diferencial é aplicado fora da área do chip BGA. Para diminuir a diafonia, o espaçamento entre dois pares de linhas diferenciais não é inferior a 80mil. O espaçamento entre os pinos do chip de interconexão neste artigo é de 1mm e a limitação do tamanho do furo passante do BGA faz com que a largura da linha/espaçamento/largura da linha do diferencial na área do chip BGA seja 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

Tecnologia industrial

- Como documentar cabos e chicotes

- O que é Power Hammers? - Tipos, Design e Operação

- Placas de circuito impresso personalizadas de alta tecnologia

- Diretrizes para Projeto de RF e Microondas

- Materiais e design de PCB para alta tensão

- Capacidades de dobra flexível e rígida-flexível no projeto de PCB

- Retrocessos e soluções no projeto de PCB de RF

- Tungstênio

- O processo de projeto e implementação de automação da planta

- A ascensão dos PCBs de interconexão de alta densidade