Processamento isométrico diferencial e verificação de simulação de projeto de PCB de alta velocidade

Influência do atraso relativo nos sinais

Os sinais transmitidos em linhas de sinal diferenciais contêm componente de modo diferencial e componente de modo comum de sinais.

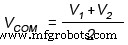

A quantidade de sinais diferenciais refere-se à diferença entre dois sinais seguindo a fórmula Vdif =V1 - V2 . A quantidade de sinais de modo comum refere-se a metade da soma de dois sinais seguindo a fórmula

. Portanto, a mudança de tensão de uma única linha definitivamente leva à influência simultânea nos sinais de modo diferencial e nos sinais de modo comum. Em seguida, o software gráfico é aplicado para desenhar o diagrama de funções matemáticas para estudar respectivamente a influência nos sinais de modo diferencial e nos sinais de modo comum. Por conveniência de pesquisa, os sinais podem ser analisados simulando-os em forma de onda trapezoidal com o mesmo tempo superior e tempo de inatividade.

. Portanto, a mudança de tensão de uma única linha definitivamente leva à influência simultânea nos sinais de modo diferencial e nos sinais de modo comum. Em seguida, o software gráfico é aplicado para desenhar o diagrama de funções matemáticas para estudar respectivamente a influência nos sinais de modo diferencial e nos sinais de modo comum. Por conveniência de pesquisa, os sinais podem ser analisados simulando-os em forma de onda trapezoidal com o mesmo tempo superior e tempo de inatividade. • Influência nos sinais diferenciais

O sinal do terminal de fase positiva, o sinal do terminal de fase negativa e o sinal diferencial dos pares de linhas diferenciais são exibidos na Figura 1 abaixo, na qual a linha completa significa onda de sinal diferencial.

Se uma colocação de fase ocorrer do terminal de fase positivo para o terminal de fase negativa, haverá uma mudança de diferença entre o sinal do terminal de fase positivo e o sinal do terminal de fase negativo na borda superior ou inferior e essa mudança mudará com a mudança de fase. Tr é usado para representar o menor tempo entre o tempo crescente e decrescente. Pode-se indicar que quando a colocação da fase for menor que o ponto dois de Tr , a distorção do sinal é relativamente pequena e o aumento da colocação de fase leva a uma forte distorção da forma de onda diferencial. Quando o posicionamento da fase excede Tr , a área não monotônica ocorrerá na forma de onda. Aqui a área não monotônica é uma linha reta. No entanto, para sinais práticos, por causa de reflexões, grandes subidas e descidas podem ocorrer em áreas não monotônicas com pulso de interferência formado levando a falsos disparos, o que deve ser evitado. Além disso, a borda superior da forma de onda diferencial torna-se lenta com o aumento do posicionamento da fase, o que pode levar a um tempo de estabelecimento insuficiente para o sinal de dados e pode levar a um tempo de retenção insuficiente para o sinal de clock.

• Influência no sinal de modo comum

A colocação de fase do sinal de terminal único não terá influência na forma de onda diferencial, mas alterará a forma de onda dos sinais de modo comum. Quando a colocação de fase ocorre no sinal terminal positivo, a mudança de onda ocorrerá para sinais de modo comum. Pode-se indicar que a faixa de flutuação está relacionada com a quantidade de colocação de fase. Quando a quantidade de colocação de fase é respectivamente 0,05Tr , 0,1Tr , 0,2Tr e 0,5Tr , a faixa de flutuação do modo comum é respectivamente 5%, 10%, 20% e 50% da faixa de flutuação original. Quando a fase aumenta para Tr ou mais, a flutuação aumentará para aproximadamente 100%, que é a faixa de flutuação mais alta. A mudança do sinal de modo comum pode levar a problemas de EMI e, como o sinal de código comum não é recebido no terminal sob muitas condições, a reflexão se formará no terminal receptor, levando ao toque do sinal. Portanto, a faixa de flutuação do sinal de modo comum deve ser diminuída o máximo possível.

Em conclusão, um atraso relativo muito grande entre pares diferenciais pode causar falsos disparos de sinais, reflexão de sinal, EMI e problemas de sequenciamento de tempo. No entanto, o grau de influência do sinal de atraso relativo depende do fator de escala compatível com o sinal Tr . Quando o fator de escala é 0,05, a distorção dos sinais diferenciais pode ser quase ignorada. No entanto, para sinais de modo comum, quando o fator de escala é 0,05, a flutuação de tensão dos sinais de modo comum pode ser controlada em aproximadamente 5%. Então, mesmo na situação de reflexão total, a tensão de reflexão empilhada nas linhas de sinal é apenas 10% da flutuação original, o que geralmente é um valor aceitável. Portanto, no processo de projeto de PCB de alta velocidade, o atraso relativo da linha de sinal diferencial nas regras de regulação de roteamento pode ser definido como 0,05 Tr que é capaz de atender ao requisito de integridade do sinal.

Determinação da Categoria de Atraso Relativo

Com base na análise acima, a chave de determinação da categoria isométrica diferencial, ou seja, a determinação do atraso relativo dos pares diferenciais, está na determinação de Tr referindo-se ao menor valor entre o tempo superior e inferior dos sinais diferenciais. A saída do tempo de subida e descida é na verdade a saída da combinação de impedância e capacitância. Portanto, o tempo de subida/descida sem carregamento é, na verdade, o tempo de subida/descida inerente.

Os três métodos a seguir podem ser aplicados para obter o valor de Tr :

• O tempo de subida/descida pode ser obtido diretamente nos manuais dos componentes. No entanto, na maioria das situações, esse parâmetro não é fornecido.

• Valor de Tr pode ser obtido a partir das palavras-chave Ramp do modelo IBIS (Input/Output Buffer Informational Specification) do componente. Os parâmetros de tempo de subida/descida nas palavras-chave Ramp são geralmente medidos na porta de saída conectada com um resistor de 50Ω, que geralmente é de 20% a 80% do tempo de tensão final. Como os parâmetros são obtidos sem considerar a influência do pacote, é estrito para nós usar o tempo de subida/descida como o valor de Tr .

• O valor de Tr pode ser estimado de acordo com a frequência de clock mínima ou frequência de clock máxima dos sinais de saída. Como a borda de subida distributiva é aproximadamente 10% da frequência de clock na maioria dos sistemas digitais de alta velocidade, o valor de Tr pode ser estimado com o período mínimo de clock Tclk fornecido com base na fórmula:Tr =Tclk x 10%.

O valor estimado obtido através do período de clock é geralmente rigoroso porque os parâmetros parasitas do pacote ou o carregamento de componentes tornarão o tempo de subida/descida inerente nos transistores muito mais lento.

No trabalho prático, na maioria das situações, os projetistas de circuitos não fornecem informações de Tr para engenheiros de layout de PCB que recebem apenas algumas demandas ambíguas em termos de controle isométrico diferencial. O terceiro método, sem dúvida, fornece um esquema simples para engenheiros de layout de PCB, desde que a frequência de clock mais alta na linha de sinal seja obtida. A frequência de clock mais alta é considerada o parâmetro de projeto mais confiável para projetistas de circuitos e geralmente é fornecida aos engenheiros de layout de PCB no início do projeto de PCB.

O terceiro método geralmente leva a uma lista de valores de referência dentro da categoria de controle de atraso relativo entre pares diferenciais, conforme mostrado na tabela abaixo.

| Frequência do Relógio/ns | Frequência do Relógio/MHz | Categoria de atraso relativo/ps | Comprimento da Linha de Transmissão/mil |

| 3,75 | 266 | 18,8 | 105 |

| 3 | 333 | 15 | 84 |

| 2,5 | 400 | 12,5 | 70 |

| 1,87 | 533 | 9.4 | 52 |

| 1,5 | 667 | 7,5 | 42 |

| 1,25 | 800 | 6.3 | 35 |

Verificação de simulação

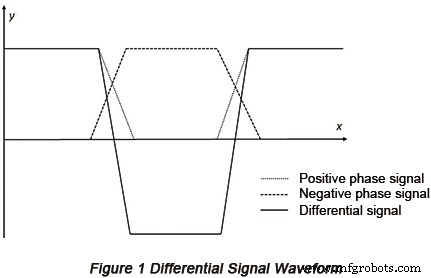

Tome o sinal diferencial DQS (Data Strobe) entre o TSM320 e o MT41J256M16 como exemplo, o software de simulação Cadence é aplicado para transmitir o sinal DOS para a memória DRR3 para simular o chip de controle de memória, analisar sua influência no tempo de espera do estabelecimento do sinal de dados e verificar a análise acima. O circuito de simulação é mostrado na Figura 2 abaixo.

Com base na Figura 2, a tensão de referência dos pinos de saída é 1,5V; chip de controle de memória é conectado diretamente com chip de memória através do modo ODT (On-Die Termination) com linha de transmissão de 800mil; impedância diferencial é de 100Ω e frequência de clock de simulação de 800MHz. Uma linha de transmissão de 50Ω é conectada em série com o terminal de fase positiva DQS para simular o fenômeno de discrepância de pares diferenciais. Na situação de diferenciais isométricos, o comprimento da linha de transmissão de terminal único de 50Ω é 0mil.

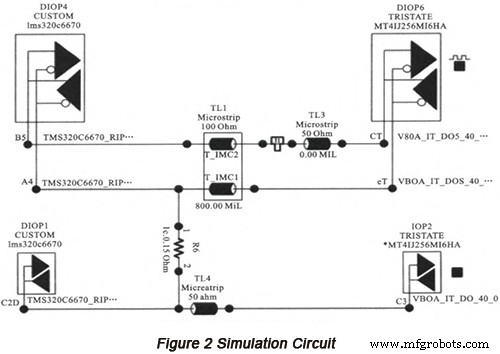

A simulação é realizada para o circuito isométrico diferencial. A Figura 3 ilustra o sinal de saída no terminal de fase positiva dos sinais diferenciais. Através da medição, o tempo de subida é de aproximadamente 216ps, enquanto o tempo de queda é de 219ps, portanto, o tempo mínimo de subida/descida Tr deve ser 216ps.

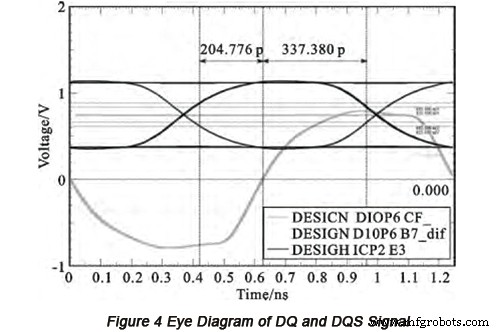

A Figura 4 é um diagrama de olho do sinal de dados DQ e do sinal de disparo DQS através de simulação com o tempo de estabelecimento de 205ps e o tempo de retenção de 337ps. De acordo com a taxa de rotatividade dos sinais DQS e DQ através de simulação e com base no manual de dados, o tempo mínimo de estabelecimento dos sinais de dados pelo terminal receptor é de 85ps e o tempo mínimo de espera é de 95ps. Portanto, a sobremedida do tempo mínimo de estabelecimento é de 120ps e o tempo de espera de 242ps.

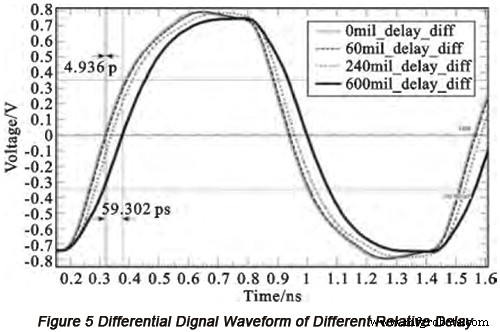

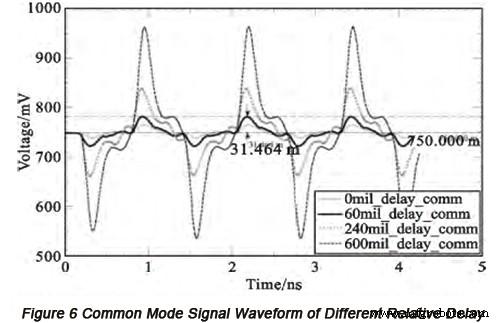

A situação da existência de 0,05Tr colocação de fase, 0,2Tr colocação de fase e 0,5Tr a colocação de fase no terminal de fase positiva deve ser considerada. O circuito pode ser simulado com comprimento de linha de transmissão de terminal único que é definido respectivamente para 60mil, 240mil e 600mil. A forma de onda do sinal diferencial e a forma de onda do sinal de modo comum através de simulação por 4 vezes são ilustradas nas Figuras 5 e 6.

Com base na Figura 5, a distorção é o mínimo quando os atrasos relativos de 0,05Tr e 0,2Tr tomar lugar. Especialmente quando o atraso relativo é 0,05Tr , apenas a colocação de cerca de 5ps do sinal diferencial para a forma de onda do sinal diferencial sem atraso relativo, de modo que a sobremedida de estabelecimento do sinal de dados seja aumentada em cerca de 5ps com o tempo de sobremedida de retenção diminuído em 5ps. Embora o tempo de sobremedição de retenção seja reduzido, essa quantidade de posicionamento é tão pequena para o tempo de retenção de 242ps. O sequenciamento de tempo pode ser evitado. Para a situação em que o atraso relativo é 0,5Tr , o posicionamento da forma de onda do sinal DQS atingiu cerca de 60ps. Embora esta colocação ainda esteja dentro da categoria de sobremedida, deve-se prestar atenção suficiente.

Com base na Figura 6, o aumento da colocação de fase leva a flutuações periódicas óbvias nas ondas e ao aumento gradual do alcance. Quando o atraso relativo é respectivamente 0,05Tr , 0,2Tr e 0,5Tr , o valor de pico medido do sinal de modo comum é, respectivamente, 61mV, 176mV e 430mV, entre os quais o valor mais alto é sete vezes o mais baixo. A maior faixa de flutuação é, respectivamente, 4,3%, 12% e 29%.

Em conclusão, o resultado da simulação é compatível com o resultado obtido através da análise do diagrama de funções matemáticas. Quando o atraso relativo entre os pares diferenciais for menor que 0,05Tr , a influência nos sinais é bastante pequena.

O período mínimo de clock do sinal de saída no terminal de saída é aplicado para estimar a categoria de controle de atraso relativo. Com base no manual do componente, o período mínimo de clock dos componentes é de 1,25ns com frequência de clock de 800MHz. De acordo com a Tabela 1, o atraso relativo deve ser controlado dentro de 6,3ps com comprimento de linha de transmissão de 35mil. Aparentemente, esse valor é muito menor que a categoria de controle do atraso relativo de 0,05Tr através de simulação. Portanto, a categoria de controle de atraso relativo estimado é relativamente conservadora, o que é mais específico do que o resultado simulado.

Recursos úteis

• Pesquisa sobre design de PCB de alta velocidade em sistemas de aplicativos incorporados

• Como projetar planos de imagem para PCBs de alta velocidade

• Desafios de design de PCB de alta velocidade na integridade do sinal e suas soluções

• Simulação de PCB usando OrCAD PSpice

• Serviço completo de fabricação de PCB da PCBCart - Várias opções de valor agregado

• Serviço avançado de montagem de PCB da PCBCart - Comece a partir de 1 peça

Tecnologia industrial

- Diretrizes para Projeto de RF e Microondas

- Materiais e design de PCB para alta tensão

- Capacidades de dobra flexível e rígida-flexível no projeto de PCB

- Etapas e processo Aprenda a proteger seu projeto de PCB

- Retrocessos e soluções no projeto de PCB de RF

- 3 técnicas de roteamento no projeto de circuito de sinal de alta velocidade PCB

- Dicas de layout de alta velocidade

- Método de supressão de reflexão de sinal em layout de PCB de alta velocidade

- Discussão sobre potência e aterramento em compatibilidade eletromagnética de PCB

- Análise de integridade de sinal e projeto de PCB em circuito misto analógico-digital de alta velocidade