Como criar uma declaração simultânea em VHDL

Uma instrução concorrente em VHDL é uma atribuição de sinal dentro da arquitetura, mas fora de uma construção de processo normal. A instrução concorrente também é chamada de atribuição concorrente ou processo concorrente.

Quando você cria uma declaração concorrente, na verdade você está criando um processo com certas características claramente definidas. Declarações simultâneas são sempre equivalentes a um processo usando uma lista de sensibilidade, onde todos os sinais à direita do operador de atribuição de sinal estão na lista de sensibilidade.

Esses processos de notação abreviada são úteis quando você deseja criar uma lógica simples que resulta na atribuição de um único sinal. Em vez de digitar uma construção de processo completa com listas de sensibilidade e tudo isso, você pode simplesmente atribuir ao sinal de destino diretamente na arquitetura.

Esta postagem do blog faz parte da série de tutoriais básicos de VHDL.

Quando usado corretamente, a intenção do código ainda será bastante clara. Não há necessidade de criar um processo para cada bit que você deseja inverter.

Exercício

Neste vídeo aprendemos como criar uma declaração concorrente:

O código final que criamos neste tutorial:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

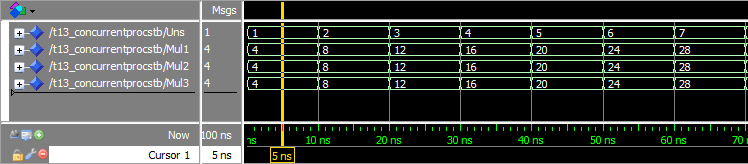

A janela de forma de onda no ModelSim depois que pressionamos executar e ampliamos a linha do tempo:

Análise

Podemos ver pela forma de onda que

Mul1 , Mul2 e Mul3 se comportam exatamente da mesma forma. Isso ocorre porque a instrução concorrente e os dois processos que criamos são equivalentes. Uma instrução concorrente funciona como um processo. Todos os sinais à direita do

<= são adicionados automaticamente à lista de sensibilidade. Isso significa que o sinal à esquerda do <= será atualizado sempre que um dos sinais avaliados for alterado. Há muitas maneiras de multiplicar números em VHDL. Neste exercício, multiplicamos o

Uns sinal por 4, usando deslocamento de bits. Todos os nossos sinais são de unsigned tipo, o que significa que eles são interpretados por números. Acrescentar um 0 à direita de um número binário é o mesmo que multiplicá-lo por 2. Esta é uma ilustração do que acontece no cursor na forma de onda:

Retirada

- Uma instrução concorrente é uma atribuição de sinal diretamente na região da arquitetura

- Declarações simultâneas são equivalentes a um processo com todos os sinais avaliados na lista de sensibilidade

Ir para o próximo tutorial »

VHDL

- Declaração de Procedimento - Exemplo de VHDL

- Como criar uma lista de strings em VHDL

- Como criar um testbench orientado por Tcl para um módulo de bloqueio de código VHDL

- Como parar a simulação em um testbench VHDL

- Como criar um controlador PWM em VHDL

- Como criar um buffer de anel FIFO em VHDL

- Como criar um testbench de autoverificação

- Como criar uma lista vinculada em VHDL

- Como usar um procedimento em um processo em VHDL

- Como usar uma função em VHDL