Como tornar os processadores confiáveis

Os circuitos integrados (ICs) modernos fornecem os recursos computacionais e de controle do sistema para processar enormes quantidades de dados, tomar decisões críticas de segurança em tempo real e proteger dados confidenciais. Projetar um circuito integrado específico de aplicativo (ASIC) ou sistema em chip (SoC) field-programmable gate array (FPGA) seria proibitivamente caro e demorado. Muitas funções críticas são implementadas usando propriedades intelectuais (IPs) de terceiros. Os núcleos do processador, por exemplo, são fornecidos por organizações especializadas e fornecem uma função flexível e programável por software por meio de sua arquitetura de conjunto de instruções (ISA), que define a interface entre o hardware e o software. As arquiteturas de processador de código aberto oferecem uma oportunidade para um escrutínio mais profundo e garantia de segurança rigorosa em sistemas que já estão enfrentando um ambiente de ameaça fluido. Este artigo descreve uma abordagem para fornecer garantia de segurança de IP e SoCs com base no ISA de código aberto RISC-V.

Inventado na Universidade da Califórnia e gerenciado pela RISC-V Foundation sem fins lucrativos, o RISC-V é o primeiro ISA de código aberto a se tornar uma escolha industrial genuinamente viável para uma ampla gama de aplicações.

RISC-V é um ISA de código aberto inventado na Universidade da Califórnia e gerenciado pela RISC-V Foundation, uma organização sem fins lucrativos com mais de 300 membros fundada em 2015. RISC-V é o primeiro ISA de código aberto a se tornar um escolha industrial genuinamente viável para uma ampla gama de aplicações. O ecossistema de ferramentas, software e experiência é robusto e está crescendo continuamente. Muitos indivíduos e organizações já doaram IPs de hardware de código aberto implementando o ISA RISC-V. O OpenHW Group, por exemplo, tem como objetivo tornar realidade a tão esperada perspectiva de hardware de código aberto - particularmente, núcleos de processador - para chips de alto volume.

A ascensão do RISC-V tem muitas razões por trás disso. Construído do zero com extensibilidade personalizada em mente, o RISC-V permite um novo nível de otimização de hardware para cargas de trabalho específicas. A lei de Moore está desacelerando e a customização é crucial para sustentar o nível de melhorias de desempenho que os avanços tecnológicos no processo de fabricação de semicondutores não podem mais fornecer. Além disso, a arquitetura RISC-V é isenta de custos de licenciamento e royalties, permitindo que mais empresas desenvolvam produtos inovadores e acessíveis. Muito está acontecendo na área de IoT e dispositivos vestíveis com recursos de inteligência artificial, por exemplo.

Os integradores de SoC costumam usar IPs de processador RISC-V de código aberto ou de terceiros. Esses designs e seus conjuntos de ferramentas associados podem ser aumentados com instruções personalizadas. Um ambiente de verificação de alta qualidade fornecido com o IP e testes adicionais no nível do sistema podem fornecer alguma confiança de que o IP não tem bugs críticos. Infelizmente, para muitas aplicações, isso não é suficiente e existem outros riscos graves a serem considerados.

Vulnerabilidades e Trojans

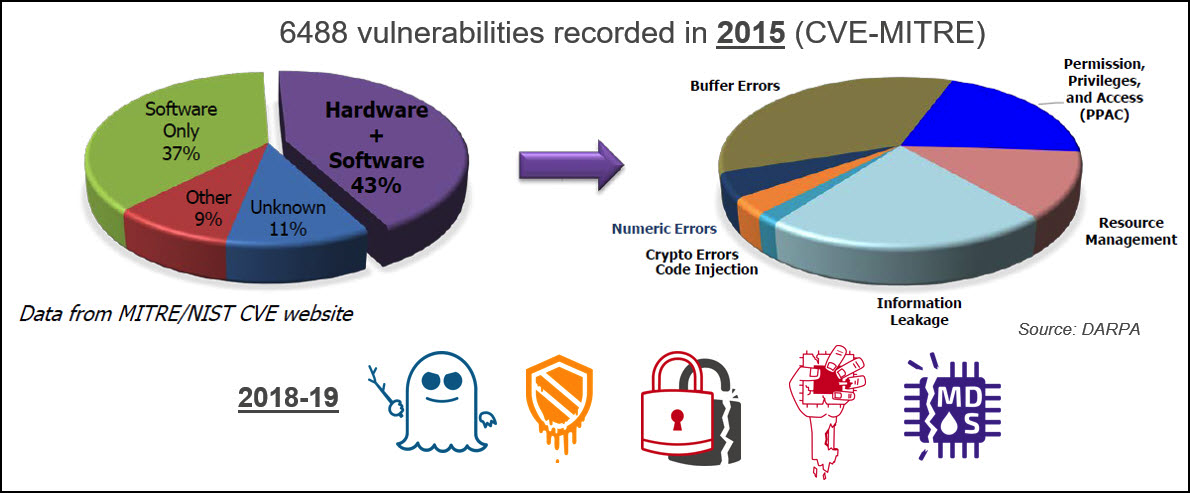

Tradicionalmente, as vulnerabilidades de segurança em sistemas eletrônicos têm sido associadas a problemas de nível de sistema e de software. Mais recentemente, os IPs de hardware, principalmente os processadores, também se tornaram uma preocupação central (consulte a Figura 1). As implementações de processador usam microarquiteturas baseadas em pipeline e geralmente incluem recursos de otimização de desempenho e energia. A complexidade aumenta o risco de perder não apenas bugs funcionais, mas também vulnerabilidades de segurança. Os pesquisadores de segurança que descobriram os ataques Meltdown e Spectre no início de 2018 demonstraram que os recursos de otimização de desempenho em processadores podem ser usados de maneiras não intencionais para fins nefastos. Desde então, muitas outras vulnerabilidades em processadores de ponta e de ponta foram descobertas. Canais laterais e ataques de execução transitória podem violar enclaves seguros e permitir que aplicativos maliciosos vazem dados confidenciais ou até mesmo assumam o controle do sistema. E, ao contrário do software, os problemas de hardware não podem ser facilmente reparados com atualizações remotas. Resolver um problema de hardware por meio do software geralmente causa uma grave degradação do desempenho.

A arquitetura RISC-V possui muitos recursos que suportam a implementação de sistemas embarcados seguros. A especificação de privilégio define quatro modos de privilégio (máquina, supervisor, hipervisor e usuário), por exemplo. Instruções personalizadas e extensões ISA em processo de ratificação, como a extensão criptográfica, fornecem recursos de segurança adicionais. Os designers podem implementar vários enclaves seguros para isolar aplicativos e evitar o vazamento de dados confidenciais. No entanto, os recursos da microarquitetura RTL ainda podem resultar em vulnerabilidades de segurança. Esses riscos não podem ser tratados inteiramente no nível ISA. Uma nova abordagem em exploração é o uso de um ISA aumentado (aISA) para definir aspectos da execução de instruções no nível da microarquitetura e, por exemplo, controlar o estado de buffers ou registros não visíveis no nível do ISA. Os bugs funcionais da RTL ainda podem comprometer todos esses recursos de segurança.

Um risco menos provável, mas com uma gravidade muito maior, é a presença de cavalos de Tróia lógicos ou de hardware mal-intencionados no núcleo RISC-V. Um Trojan de hardware é uma função lógica deliberadamente projetada para ser furtiva, que é ativada em circunstâncias muito raras, conhecidas apenas pelo invasor. Uma sequência específica de dados e eventos de controle que não aconteceriam enquanto o sistema estivesse operando em seus casos de uso de destino aciona a lógica do cavalo de Tróia, que por sua vez fornece uma carga útil prejudicial, vazando um segredo ou corrompendo criticamente o comportamento do sistema, por exemplo. As integrações de SoC usando núcleos RISC-V de código aberto ou de terceiros não podem mais ignorar esse risco.

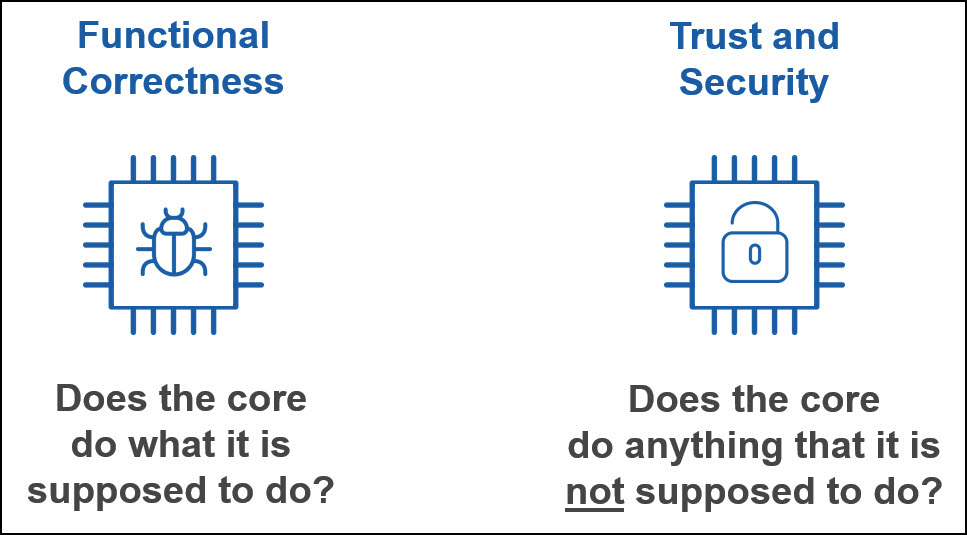

Garantir que um processador faça o que deve fazer é difícil, mas garantir que ele não faça nada que não deveria é uma tarefa ainda mais desafiadora que ainda não foi resolvida. Os sistemas críticos para a segurança e os sistemas em que a proteção da privacidade dos dados é fundamental, precisam de soluções eficientes e de alta qualidade que abordem o risco de vulnerabilidades de segurança e cavalos de Tróia.

Figura 1:O banco de dados CVE-MITER registrou 6488 vulnerabilidades em 2015, 43% das quais podem ser classificadas como vulnerabilidades de hardware assistidas por software. Em 2018 e 2019, os pesquisadores descobriram e relataram inúmeras vulnerabilidades em processadores, incluindo Meltdown e Spectre, Foreshadow, ZombieLoad e RIDL e Fallout. (Fonte:DARPA e OneSpin)

Garantia de hardware inteligente

Garantir a confiança e a segurança dos IPs RISC-V requer soluções técnicas inovadoras e eficientes que são complementares às abordagens de correção funcional, visando principalmente os casos de uso pretendidos de IP (ver Fig. 2). Os provedores de IP são responsáveis por aplicar processos de confiança e verificação de segurança de última geração, enquanto os integradores de IP devem ter acesso a soluções de garantia independentes que podem ser implantadas rapidamente e sem conhecimento profundo dos detalhes de implementação de IP.

Métodos formais podem analisar funções de hardware exaustivamente e fornecer prova de que o IP ou SoC corresponde precisamente a um comportamento esperado, muitas vezes capturado em asserções SystemVerilog. A verificação formal de hardware usando verificadores de modelos comerciais teve ampla adoção na última década. Normalmente, os provedores de IP e integradores de SoC têm especialistas em verificação formal em suas fileiras, tentando reduzir ao mínimo o risco de erros funcionais ausentes. Embora certas tarefas de verificação formais bem definidas possam ser automatizadas por meio de Aplicativos , em geral, é necessário um esforço significativo de engenharia para capturar o comportamento esperado do IP nas afirmações. Além disso, não há garantia de que afirmações suficientes foram escritas. Funções não documentadas ou lacunas não intencionais no conjunto de afirmações podem levar à funcionalidade de IP não verificada.

A natureza de código aberto do RISC-V permite o desenvolvimento de soluções de garantia independentes e pré-configuradas. A solução de verificação de integridade RISC-V da OneSpin, por exemplo, pode ser aplicada a uma ampla gama de microarquitetura. Inclui modelos do ISA RISC-V e ISA privilegiado que são extensíveis e podem acomodar instruções personalizadas. Um aspecto crucial desta solução é que ela se baseia no processo GapFreeVerification ™ da OneSpin, que fornece uma prova rigorosa de que o conjunto de afirmações que modelam o ISA RISC-V está completo e livre de lacunas. Este aspecto é de extrema importância quando a detecção de cavalos de Troia de hardware ou lógica não documentada é um objetivo crucial. A solução permite que integradores SoC com experiência limitada em RISC-V e a implementação RTL sob escrutínio ganhem confiança na qualidade e confiabilidade do IP. Os desenvolvedores de IP podem usá-lo para detectar fraquezas de segurança e bugs funcionais antes do lançamento.

Figura 2:A verificação de exatidão funcional fornece confiança de que a implementação de um processador se comporta conforme especificado e atende aos requisitos dos usuários finais. A verificação de confiança e segurança, por outro lado, fornece a confiança de que o processador não possui funções não documentadas, canais secundários imprevistos, cavalos de Troia de hardware ou outras vulnerabilidades que podem ser exploradas por agentes mal-intencionados. (Fonte:OneSpin)

Funciona?

O processo de garantia de integridade RISC-V descrito na seção anterior foi aplicado com sucesso a vários projetos RTL. A Edaptive Computing, empresa que integra soluções inovadoras para otimizar, garantir e automatizar rapidamente sistemas de sistemas e processos para uma variedade de clientes do Departamento de Defesa dos EUA e do setor comercial, aplicou o processo ao RocketCore, por exemplo. O RocketCore é um núcleo RISC-V de 64 bits comprovado em silício de código aberto com um sistema de memória virtual de 39 bits. Ele tem um pipeline de cinco estágios, de edição única e em ordem com conclusão fora de ordem para instruções de longa latência, como divisão. Inclui os recursos avançados de previsão de desvio e reprodução de instruções.

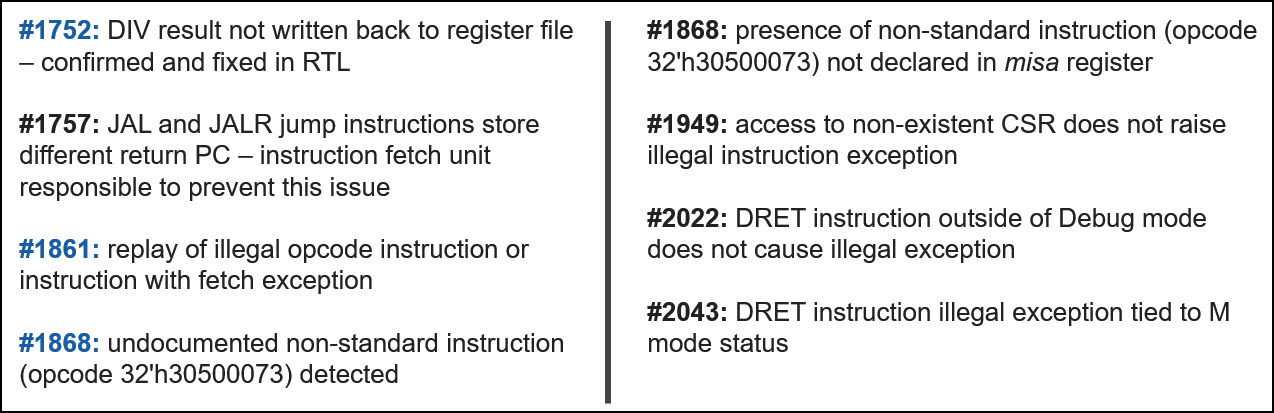

A solução de verificação de integridade RISC-V foi aplicada ao design com todas as instruções, níveis de privilégio, interrupções e mecanismo de exceção, e 8 problemas foram detectados (ver Fig. 3). Informações adicionais sobre 3 deles são relatadas abaixo.

Caixa esquina da divisão :um bug profundo associado à conclusão fora de ordem da instrução de divisão. Esse problema pode ter feito com que um programa de software usando a operação de divisão computasse resultados incorretos e levasse ao mau comportamento do sistema. O problema aparece apenas em uma combinação de circunstâncias raras e é por isso que os esforços de verificação anteriores não o perceberam.

Repetição de instrução ilegal :este não é um bug de esquina. A repetição de uma instrução ilegal pode desperdiçar ciclos de processamento, mas se isso acontecer apenas em situações raras, o impacto no desempenho é insignificante. No entanto, existem outros aspectos a serem considerados. A repetição da instrução pode causar solicitações de memória desnecessárias. Essas solicitações podem ter efeitos colaterais que podem ser aproveitados em ataques de canal lateral. Como resultado, esse comportamento precisa ser eliminado ou claramente compreendido e documentado.

Instrução não documentada :foi detectada uma instrução não documentada e fora do padrão chamada CEASE que interrompe o núcleo. Na verdade, o RISC-V RocketCore poderia fazer algo que não deveria fazer. Funções ocultas não documentadas não são aceitáveis quando a confiança e a segurança são uma preocupação, mesmo quando se relacionam a casos de uso considerados irrelevantes para o aplicativo final.

O estudo de caso RocketCore é apresentado em detalhes no documento GOMACTech 2019 intitulado Verificação formal completa de IPs de processador RISC-V para ICs confiáveis livres de cavalos de Tróia. Para obter uma cópia, visite onespin.com/resources/white-papers.

Figura 3:Lista de problemas detectados pelas soluções de verificação de integridade RISC-V da OneSpin e relatados no projeto GitHub RocketCore. (Fonte:OneSpin)

O que vem a seguir?

O processo de garantia RISC-V apresentado neste artigo detecta cenários que podem afetar a segurança e desvela sistematicamente funções não documentadas e cavalos de Troia de hardware que afetam o comportamento do processador, independentemente de quão raros e furtivos possam ser. No entanto, os canais laterais não são detectados sistematicamente. A detecção exaustiva de todos os canais laterais potenciais requer uma solução dedicada com tecnologia apropriada. Já existem protótipos que atendem a esse desafio. Para obter mais informações, visite onespin.com/resources/technical-articles e leia o artigo do EE Times Side-Channel Attacks on Embedded Processors.

Os núcleos do processador são IPs cruciais em sistemas incorporados. No entanto, um SoC típico integra muitos outros IPs que também podem conter Trojans de hardware. Ao contrário dos núcleos RISC-V, as soluções independentes de garantia de confiança podem não estar prontamente disponíveis. Nesse caso, seria valioso ter um processo de avaliação de confiança automatizado e de baixo esforço aplicável a qualquer IP. Um processo que não inclui um modelo confiável de IP não pode garantir a ausência de um Trojan. No entanto, é possível identificar padrões de código incomuns e suspeitos, assinaturas de cavalos de Tróia conhecidas e pontos fracos que podem ser explorados em estágios posteriores de desenvolvimento para fins nefastos. Um artigo sobre este tópico intitulado Uma avaliação automatizada de confiabilidade de IP pré-silício para garantia de hardware , de autoria da AEROSPACE Corporation e engenheiros da OneSpin, será apresentado na conferência GOMACTech 2020.

Integrado

- Como aproveitar ao máximo seus dados

- Um guia para acelerar aplicativos com instruções personalizadas RISC-V certas

- Como fazer uma plataforma de robô Arduino + Raspberry Pi

- Como fazer fibra de vidro

- Como tornar os dados da cadeia de suprimentos confiáveis

- Como fazer uma animação de corte no Solidworks

- Como fazer um protótipo

- Como substituir uma mangueira hidráulica

- Como fazer um programa de segurança abrangente funcionar

- Como fazer um mandril de metal