Avançando para 7nm

Esta é a quarta de uma série de quatro partes sobre os documentos apresentados pela IBM no IEDM 2016.

O Encontro Internacional de Dispositivos Eletrônicos anual é “o fórum mundial preeminente para relatar avanços tecnológicos nas áreas de tecnologia, design, fabricação, física e modelagem de semicondutores e dispositivos eletrônicos”. Então, os pesquisadores da IBM trouxeram seu termômetro de sonda de varredura, seu espaçador de ar para um chip de 10 nanômetros, seu chip de 7 nm, e para não ser superado pelo silício, eles trouxeram seus nanotubos de carbono também. Esses documentos e apresentações de IBMistas e muitos parceiros farão parte da conferência desta semana em San Francisco.

IEDM apresenta quatro artigos da IBM como alguns dos melhores exemplos da conferência desta reinvenção da computação - estendendo a Lei de Moore e construindo novas arquiteturas e usando novos materiais para ir além dela. Aqui está uma análise mais detalhada desses artigos e dos cientistas por trás do trabalho. A parte final da série destaca o artigo “A 7nm FinFET Technology com EUV Patterning e Dual-Strained High-Mobility Channels”, de Ruilong Xie, um membro sênior da equipe técnica da GlobalFoundries e membros da equipe da IBM no Albany Nanotech Center .

Em julho passado, a IBM e seus parceiros Alliance anunciaram que desenvolveram os primeiros chips de teste de nó de 7 nm do mundo. A descoberta veio com a aplicação da litografia com ultravioleta extrema (EUV) - uma técnica de usar luz para gravar padrões em outros materiais - e com o silício germânio (SiGe) como material de canal no transistor.

Do Silício ao Silício Germânio

O artigo IEDM da equipe mostra que “a tecnologia FinFET baseada em SiGe demonstrou melhoria de desempenho com regras básicas de tecnologia de 10 nm (padrões da indústria), fornecendo soluções elegantes para uma opção de tecnologia CMOS viável. Uma dessas soluções elegantes é permitir dispositivos de baixo consumo de energia e de alto desempenho no mesmo chip - sem perder desempenho ou variabilidade em um tipo de dispositivo em relação ao outro ”, conforme explicado em Inovação de material para 7 nm .

Além disso, o SiGe ultrapassa os limites do dimensionamento do chip, alterando a forma como a corrente passa pelo canal de um transistor. Acontece que ao adicionar átomos de germânio maiores a um cristal feito de átomos de silício menores, o cristal desenvolve uma incompatibilidade de rede, gerando tensão no canal do transistor. Essa deformação torna possível mover mais corrente através do canal em tensões mais baixas. Assim, usando SiGe como um material de canal em combinação com inovações em resistência parasita e redução de capacitância, a equipe poderia traçar um roteiro para um chip de 7 nm, mantendo um equilíbrio entre potência e desempenho - um desempenho em potência constante que, conforme apresentado no IEDM , 40% melhor do que um chip de 10 nm!

Comprimentos de onda de luz extremamente pequenos

A luz que está sendo usada, com apenas um comprimento de onda de 13,5 nm, é muito mais curta do que a luz de comprimento de onda padrão de 193 nm de hoje, tornando-a capaz de gravar 20 bilhões de transistores de 7 nm em um chip. Mas antes que a equipe possa colocar tantos switches em um chip, eles precisam fazer com que a tecnologia por trás do uso de um comprimento de onda tão curto seja um processo consistente, controlado e repetível.

Para fazer chips usando litografia, um wafer é exposto a um padrão de luz da mesma forma que todos os negativos de fotografia não digital são impressos em papel contato - é segurado acima do wafer e a luz é passada através de uma máscara (o 'negativo') . O tamanho das linhas e fios que podem ser impressos usando essa técnica reflete não apenas o tamanho das linhas na máscara, mas também o comprimento de onda da luz que está sendo usada. Hoje, usando luz de 193 nm, um wafer pode ser exposto várias vezes se o padrão necessário for menor do que o que 193 nm pode fornecer por si só.

Assim, assim como a impressão em xilogravura japonesa, padrão após padrão é colocado em camadas sobre o wafer para obter um chip mais complexo - e menor. Essa técnica de padrões múltiplos, entretanto, causa degradação; o que pode não ser um problema tão crítico para chips em dispositivos produzidos em massa, como smartphones, mas é um obstáculo significativo para supercomputadores e sistemas especializados que exigem confiabilidade muito alta. E, embora seja tecnicamente possível fazer chips de 7 nm dessa maneira, é um grande motivo pelo qual a IBM decidiu explorar como fazer chips de 7 nm usando a tecnologia EUV.

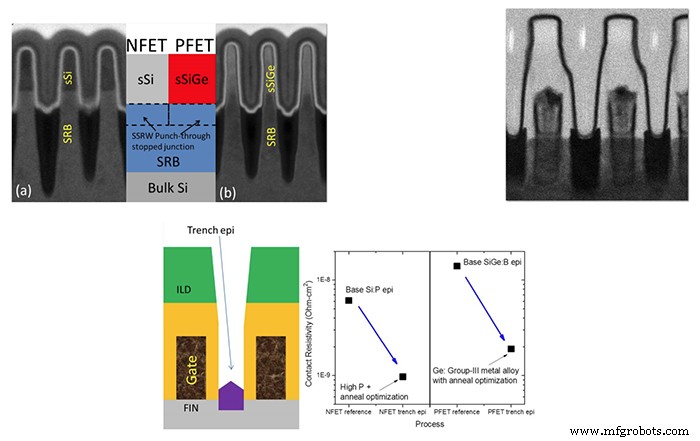

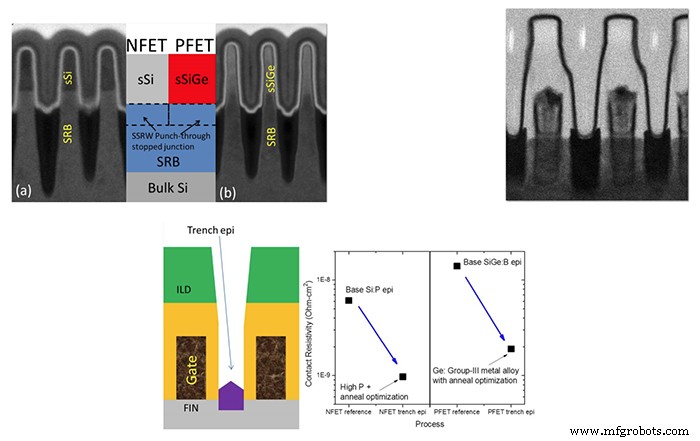

Superior esquerdo: Uma descrição esquemática de materiais de canal de tensão dupla no SRB com um poço retrógrado super íngreme (SSRW), juntamente com imagens TEM de (a) a aleta de silício tensionada por tração e (b) a aleta SiGe comprimida em um SRB comum. Canto superior direito: Uma imagem TEM de um dispositivo de pitch de polissilício em contato com 48nm com um contato auto-alinhado otimizado com uma abertura de contato de ~ 10nm e Lmetal de ~ 15nm. Meio inferior: a ilustração e o gráfico mostram que o processo epitaxial da trincheira atende simultaneamente às regras básicas e à redução da resistividade de contato após as otimizações de implante e recozimento.

Usando o EUV de 13,5 nm, apenas um padrão de alta fidelidade é necessário para imprimir um único padrão em um chip de 7 nm. O desafio do EUV é como amadurecer a tecnologia para estar pronta para a produção. Muito parecido com o modo como o IBM System 360, construído em 1964, levou às máquinas menores e mais rápidas de hoje por meio de refinamento, dimensionamento e esforço de engenharia, o EUV terá que amadurecer de maneira semelhante.

Considere o seguinte:para gerar luz de 13,5 nm, o dispositivo EUV libera uma gota de estanho derretido no vácuo (para obter uma forma esférica) que é então atingida por um laser de dióxido de carbono que o achatamento e o move para um ângulo específico. O estanho, ainda caindo, é então atingido - e vaporizado - com outro laser de dióxido de carbono mais poderoso para liberar luz de 13,5 nm, que é então capturada e focada em um wafer usando espelhos especializados.

Embora o processo para usar esta luz de 13,5 nm seja complicado, o trabalho das equipes está provando que fazer um chip de 7 nm usando EUV é possível e fornece resultados de alta qualidade. O que significa que chips especializados de alta confiabilidade para futuros sistemas de alto desempenho podem ser fabricados para atender às demandas de supercomputadores e sistemas de próxima geração.

Leia a primeira parte:Mapeando pontos críticos

Leia a parte dois:Outro tipo de chip com nanotubos de carbono

Leia a parte três:Espaçadores de ar para chips de 10 nm