A otimização da programação de DRAM 1T sem capacitor baseada no TFET de porta dupla

Resumo

O maior volume do capacitor e a maior corrente de fuga do transistor tornaram-se as desvantagens inerentes para a memória de acesso aleatório dinâmica (DRAM) tradicional de um transistor (1T) -um capacitor (1C). Recentemente, o tunelamento FET (TFET) é aplicado na célula DRAM devido à baixa corrente de estado desligado e alta taxa de chaveamento. A célula DRAM TFET de porta dupla (DG-TFET) com estrutura sem capacitor tem desempenho superior - maior tempo de retenção (RT) e fraca dependência de temperatura. Mas o desempenho da célula TFET DRAM é sensível às condições de programação. Neste artigo, a diretriz de otimização de programação é discutida em detalhes usando a ferramenta de simulação - Silvaco Atlas. Ambas as operações de escrita e leitura de DG-TFET DRAM dependem do tunelamento banda-a-banda (BTBT). Durante a operação de gravação, os furos vindos do BTBT governados pelo Gate2 são armazenados em potencial bem abaixo do Gate2. Uma pequena tensão negativa é aplicada no Gate2 para reter os orifícios por um longo tempo durante a retenção de “1”. O BTBT governado pelo Gate1 influencia principalmente a corrente de leitura. Usando a condição de programação otimizada, o DG-TFET DRAM obtém a maior proporção de corrente de leitura “1” para leitura “0” (10 7 ) e RT de mais de 2 s. O RT mais alto reduz a taxa de atualização e o consumo de energia dinâmica da DRAM.

Histórico

A memória dinâmica de acesso aleatório (DRAM) tornou-se uma célula de memória integral no sistema móvel e de computação [1,2,3]. Com a redução da geometria do dispositivo, o grande volume do capacitor é uma desvantagem inerente à célula DRAM tradicional de um transistor (1T) -um capacitor (1C), o que limita sua aplicação em larga escala. A célula DRAM 1T sem capacitor baseada no transistor de porta flutuante mostrou a vantagem potencial em comparação com a DRAM 1T-1C convencional para o empacotamento de alta densidade de memória [4]. No transistor de porta flutuante, as cargas na região do substrato são armazenadas na região da porta flutuante pelo tunelamento Fowler-Nordheim. E a operação de leitura depende da emissão termiônica [5, 6], que é a mesma do transistor de efeito de campo semicondutor de óxido metálico (MOSFET). Como resultado, a corrente de leitura da DRAM com o transistor de porta flutuante depende fortemente da temperatura. Além disso, a emissão termiônica faz com que a oscilação subliminar (SS) do transistor seja superior a 60 mV / dec, o que faz com que a alta corrente de fuga e o consumo de energia se tornem os maiores desafios [7,8,9].

Recentemente, o transistor de efeito de campo de tunelamento (TFET) tem sido considerado um candidato promissor para os futuros dispositivos elétricos de baixa potência [10,11,12]. O principal mecanismo de condução do TFET é o tunelamento banda-a-banda (BTBT) em vez da emissão termiônica, o que o faz obter várias vantagens, como o SS sub-60 mV / dec, baixa corrente de fuga no estado desligado e fraca dependência da temperatura [13, 14]. Até agora, grande quantidade de trabalho de pesquisa sobre TFET concentra-se principalmente no estudo do desempenho do dispositivo de TFET único e alguns circuitos simples consistem em TFETs. No entanto, o alto eu em / eu desligado do TFET permite que ele sirva para a célula DRAM [15]. Especialmente, a baixa corrente de fuga no estado desligado pode reduzir a leitura da corrente “0” e o consumo de energia da célula DRAM. Os pesquisadores projetaram uma DRAM TFET de porta dupla (DG-TFET) com a estrutura sem capacitor [16]. No DRAM DG-TFET, o armazenamento de carga durante a operação de gravação é baseado no BTBT entre o canal e o dreno, que é produzido principalmente pelo Gate2. Ao mesmo tempo, o tunelamento de elétrons promove o acúmulo de buracos na região do canal sob o Gate2. Gate1 é o principal responsável pela operação de leitura. A corrente de leitura do DGTFET DRAM depende principalmente do BTBT entre a região de origem e a região do canal. Existem alguns grupos de pesquisa que demonstraram que a corrente de leitura do DG-TFET DRAM tem uma dependência fraca da temperatura. E DG-TFET DRAM pode obter um tempo de retenção maior do que o alvo (64 ms) [17]. Mas a relação atual de leitura “1” para leitura “0” e RT não é o valor ideal devido à condição de programação não otimizada.

O desempenho do TFET DRAM, especialmente a relação de corrente de leitura “1” para leitura “0”, tem uma grande dependência da condição de programação. O Gate2 influencia principalmente o BTBT durante a operação de gravação, que domina a região de armazenamento de cargas e potencial bem abaixo do Gate2. Gate1 governa o BTBT durante a operação de leitura, que influencia principalmente a corrente de leitura “1”. As polarizações adequadas de Gate1 e Gate2 podem fazer o DGTFET DRAM obter a razão de corrente mais alta. Há pouca literatura estudando a influência das condições de programação na corrente de leitura. Neste artigo, uma diretriz detalhada de otimização de programação é proposta, incluindo operações de escrita, retenção e leitura. Ao aplicar a condição de programação otimizada, o DG-TFET DRAM obtém o desempenho ideal — a proporção da corrente de leitura de até 10 7 e o RT de mais de 2 s. E aplicando a tensão de programação otimizada, a leitura de corrente “0” é bem menor do que a relatada na referência [16, 18], o que é útil para a redução do consumo de energia.

Métodos

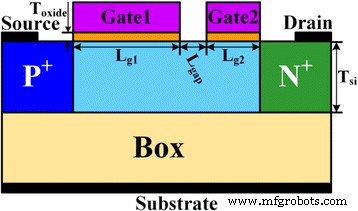

A estrutura do DG-TFET investigada neste artigo é ilustrada na Fig. 1. A concentração de dopagem de ambos os P + fonte e N + dreno é 1 × 10 20 / cm 3 . O canal intrínseco é dividido em dois segmentos:Gate1 e Gate 2, e há uma pequena lacuna entre Gate1 e Gate2. Gate1 e Gate2 são N + polissilício e P + polissilício, respectivamente. O P + polysilicon Gate2 pode criar e manter o poço físico para armazenamento de carga e para substituir o DRAM baseado em TFET convencional que utiliza um P + região do bolso como área de armazenamento. Enquanto para um N + polissilício Gate1, a concentração do orifício na região subjacente entre Gate1 e Gate2 é baixa, o que é útil para a operação de leitura. Assim, um P + Polysilicon Gate2 optou por ter uma região de armazenamento mais profunda que poderia facilitar uma retenção mais longa, enquanto um N + O polissilício Gate1 é selecionado para controlar o mecanismo de tunelamento durante a operação de leitura [18].

Esquema da célula DG-TFET DRAM. Esta figura mostra o esquema da célula DRAM TFET de porta dupla (DGTFET), incluindo Gate1, Gate2, fonte, dreno e canal. Neste design, a região de origem e a região de drenagem são P + dopagem e N + dopagem, respectivamente. Gate1 e Gate2 são N + polissilício e P + polissilício, respectivamente

Os parâmetros detalhados do dispositivo nas simulações são os seguintes:a espessura do silício bruto ( T si ) é 20 nm; os comprimentos do Gate1 (Lg 1 ) e Gate2 (Lg 2 ) são 400 nm e 200 nm, respectivamente; o comprimento da lacuna ( L lacuna ) entre o Gate1 e o Gate2 é de 50 nm; a espessura do óxido de porta (HfO 2 ) ( T óxido ) é 3 nm. As condições de programação otimizadas são mostradas na Tabela 1. As diretrizes de otimização das condições de programação serão discutidas em detalhes nas seções a seguir.

Toda a análise é realizada na ferramenta Silvaco-Atlas utilizando o modelo BTBT não local [19]. O BTBT não local leva em consideração a geração não local de elétrons e lacunas, para que possa modelar o processo de tunelamento com mais precisão. Os parâmetros do modelo de tunelamento são calibrados de acordo com os dados experimentais da referência [20]. Além disso, modelos físicos incluindo recombinação Shockley-Read-Hall, estatísticas Fermi, bem como dopagem e mobilidade dependente do campo elétrico também são usados. De acordo com as abordagens de [16, 18], os tempos de vida do elétron e do buraco são ajustados para 100 ns. A temperatura padrão é 300 K.

Resultados e discussão

O princípio de operação da célula DRAM DG-TFET é diferente daquele da DRAM tradicional. Tanto as operações de escrita como de leitura são baseadas no BTBT, mas cada uma delas tem uma função diferente. O BTBT durante a escrita “1” conduz os furos a serem armazenados no poço de potencial sob o Gate2, o que pode elevar a corrente de leitura “1”. Durante a operação de leitura, a corrente de dreno depende principalmente do BTBT próximo ao lado da fonte. Além disso, as duas portas também atuam como funções diferentes:Gate1 e Gate2 determinam principalmente a operação de leitura e a operação de gravação, respectivamente.

Operação de gravação

Durante a gravação de “1”, o Gate2 com polarização negativa aumentará a banda de energia do canal sob o Gate2, o que diminui a largura da barreira e produz o BTBT entre o canal e o dreno. E esta tendência negativa do Gate2 também induz um potencial profundo bem abaixo do Gate2. Devido ao tunelamento de elétrons do canal para o dreno, a região do canal sob o Gate2 está totalmente esgotada e muitos buracos são acumulados neste poço de potencial. Durante a escrita “0”, o Gate2 com viés positivo faz com que os furos se expulsem do poço de potencial que se recombina no lado do dreno [21].

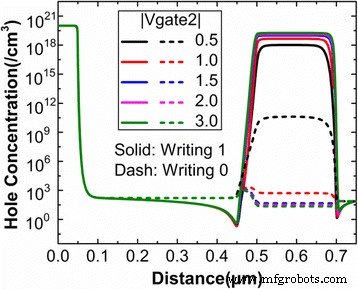

Geralmente, o valor absoluto da tensão do Gate2 permanece inalterado para a escrita “1” e a escrita “0”. A Figura 2 mostra a variação da concentração do orifício com a tensão do Gate2 após a operação de escrita. Quando a tensão do Gate2 é 0,5 V, a concentração do orifício após escrever “0” é maior devido à presença do poço de potencial, o que é prejudicial para o estado “0”. Quando o valor absoluto da tensão do Gate2 é superior a 1 V, a concentração do orifício depois de escrever “0” e escrever “1” não tem variação óbvia. Sugere que o BTBT está saturado por escrever “1” e que todos os buracos acumulados durante a escrita “1” se expulsam do potencial bem após escrever “0”. E a diferença de concentração de orifícios entre escrever “1” e escrever “0” é muito evidente, o que é benéfico para distinguir entre o estado “1” e o estado “0”.

Concentrações de furos na superfície do canal após a operação de gravação. Esta figura mostra as variações da concentração do orifício com as diferentes tensões do Gate2. A linha de corte é feita na superfície do dispositivo desde a região da fonte até a região do dreno. Nesta figura, a linha sólida e a linha tracejada representam a concentração do furo depois de escrever “1” e escrever “0”, respectivamente

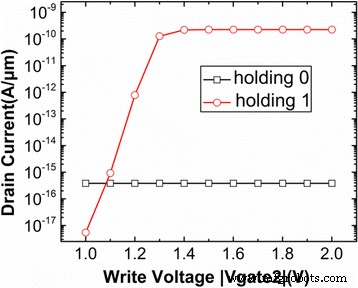

Mas o viés Gate2 durante a operação de gravação não pode ser determinado apenas pela concentração do orifício. A Figura 3 indica que a polarização do Gate2 durante a operação de gravação tem um efeito significativo na corrente de drenagem após a operação de retenção. O conjunto de tensão de programação durante a operação de retenção será discutido na próxima seção. A Figura 3 revela que a corrente de drenagem após a operação de retenção não tem variação óbvia quando o valor absoluto da tensão de escrita é superior a 1,3 V. Portanto, o -1,3 e 1,3 V são considerados como a tensão Gate2 ideal durante a escrita "1" e escrevendo “0”, respectivamente.

Drene a corrente do DG-TFET após segurar “0” e segurar “1”. Esta figura mostra a variação da corrente de drenagem após manter "0" e manter "1" em relação à tensão de escrita

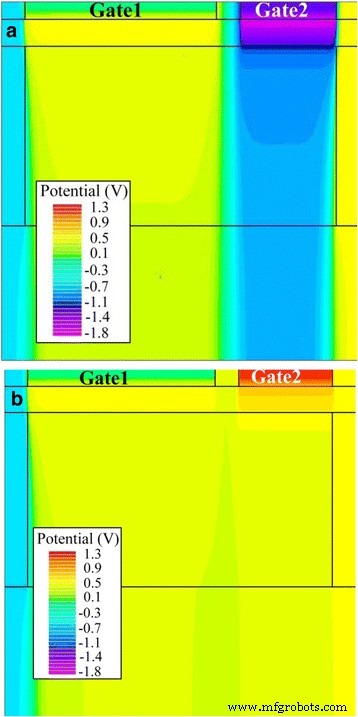

As Figuras 4a, b indicam respectivamente o contorno do potencial após a escrita "1" e a escrita "0" quando o valor absoluto da voltagem da escrita é 1,3 V. Obviamente, um poço de potencial muito profundo é criado na região do canal sob o Gate2 após a escrita " 1 ”, conforme mostrado na Fig. 4 a. Os furos acumulados são preservados neste poço de potencial durante a escrita “1”. Porém, os furos acumulados escapam deste poço de potencial durante a escrita “0”.

Contornos potenciais após a escrevendo “1” e b escrever “0” quando o valor absoluto da tensão do Gate2 for 1,3 V. a , b Os contornos potenciais depois de escrever “1” e escrever “0”, respectivamente. Os contornos de potencial nesta figura são extraídos quando o valor absoluto da tensão Gate2 é definido como 1,3 V

Operação de retenção

O processo de retenção é usado principalmente para modificar a retenção das cargas. Normalmente, o viés zero é usado durante a operação de holding para reduzir o consumo de energia [22]. Durante a operação de retenção, os furos acumulados no poço potencial são gradualmente recombinados devido à diminuição da profundidade do poço potencial. Portanto, o objetivo principal da otimização da operação de retenção é evitar a recombinação dos orifícios durante a retenção “1”. Neste projeto, uma pequena polarização negativa é aplicada no Gate2 para reter os furos no potencial bem depois de segurar “1”, enquanto o poço de potencial é esvaziado de furos após segurar “0”.

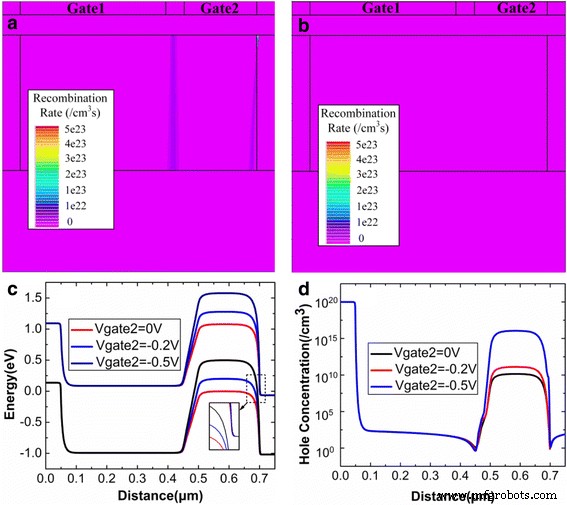

Com a tensão Gate2 mais negativa (−0,5 V) durante a operação de retenção, a recombinação dos orifícios é eliminada após segurar “1”, como mostrado na Fig. 5a, b. A eliminação da recombinação de orifícios é benéfica para a retenção de orifícios durante a retenção “1”. Uma pequena polarização negativa é aplicada no Gate2 para aumentar a profundidade potencial do poço e reter os orifícios por um longo tempo, o que é benéfico para o tempo de retenção do DRAM DGTFET. Durante a manutenção de “0”, uma polarização negativa do Gate2 pode puxar para cima a banda de energia da região do canal sob o Gate2, o que pode impedir que os elétrons vindos de BTBT entre a fonte e o canal fluam para o lado do dreno. Portanto, o Gate2 com um negativo pode reduzir a leitura da corrente “0”. No entanto, o Gate2 com tensão mais negativa (−0,5 V) diminui a distância de tunelamento próximo ao lado do dreno, conforme mostrado na Fig. 5c. Essa diminuição da distância de tunelamento faz com que o BTBT próximo ao lado do dreno durante a espera “0”, o que promove o acúmulo de furos no poço de potencial durante a espera “0”, conforme mostrado na Fig. 5d. Portanto, a tensão Gate2 mais negativa (−0,5 V) durante a manutenção de “0” degradará o estado “0”. Portanto, a fim de eliminar a recombinação de orifícios e BTBT durante a manutenção de “1” e manutenção de “0”, respectivamente, −0,2 V é considerada a polarização de Gate2 ideal durante a operação de retenção.

Taxa de recombinação na célula DRAM DG-TFET após segurar “1” quando a tensão do Gate2 é a 0 V e b −0,5 V; c diagrama de banda de energia e d concentração do orifício após segurar “0”. a , b A taxa de recombinação após segurar “1” quando a tensão Gate2 é definida como 0 V e −0,5 V, respectivamente. c A banda de energia do dispositivo da região de origem até a região de drenagem. d A concentração do orifício do dispositivo após o furo “0”. A banda de energia e a concentração do orifício são extraídas a 3 nm abaixo do óxido de porta

Operação de leitura

Posteriormente, a otimização da operação de leitura também é investigada. A operação de leitura depende fortemente do BTBT entre o P + fonte e canal. Durante a leitura “1”, o Gate1 promove principalmente o BTBT no lado da fonte, enquanto o Gate2 com a alta tensão diminui a barreira de energia que resiste ao fluxo de elétrons do canal para drenar. Mas durante a leitura “0”, é necessário que o Gate2 com a pequena tensão possa evitar que os elétrons fluam do canal para drenar. Portanto, a otimização das tensões Gate1 e Gate2 é muito importante para a operação de leitura.

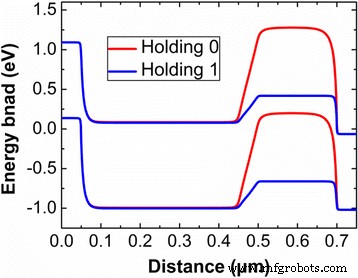

A Figura 6 mostra os diferentes diagramas de banda de energia após segurar “1” e segurar “0”. As mesmas tensões são aplicadas nos lados do Gate durante a leitura “1” e leitura “0”. Visto que as polarizações positivas do Gate serão usadas durante a operação de leitura, a banda de energia será reduzida sempre que for lido “1” ou “0”. A banda de energia do canal sob o Gate2 após segurar “0” é maior do que após segurar “1”, e esta banda de energia também é maior durante a leitura “0” em comparação com aquela durante a leitura “1”. A energia mais alta do canal sob o Gate2 criará uma barreira eficaz para resistir ao fluxo de elétrons em direção ao lado do dreno, o que diminuirá a leitura da corrente “0”.

Diagrama de banda de energia após a segurando “1” e b segurando “0”. a , b A faixa de energia do dispositivo após segurar “1” e segurar “0”, respectivamente. A banda de energia é extraída a 3 nm abaixo do óxido de porta

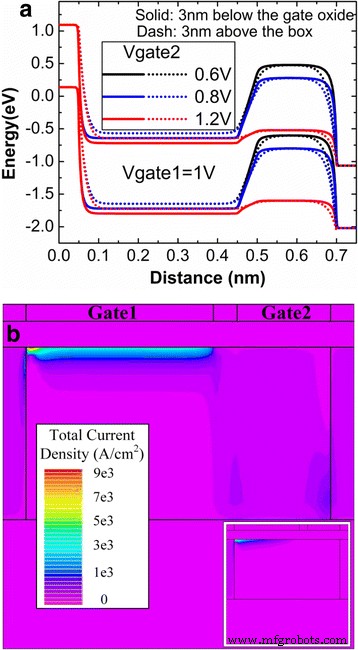

Durante a operação de leitura, o bias do dreno é ajustado para 1 V para que a corrente do dreno possa ser lida no DG-TFET. Em primeiro lugar, mantendo a tensão Gate1 de 1 V, mude a polarização de Gate2 para escolher a tensão Gate2 ideal. Como a tensão do Gate2 influencia principalmente a leitura da corrente “0”, a otimização da tensão do Gate2 é analisada pelo mecanismo de leitura “0”. A Figura 7a representa a variação da banda de energia com a tensão do Gate2 após a leitura “0”. Quando a tensão do Gate2 é mais baixa (0,6 ou 0,8 V), o canal sob o Gate2 fica totalmente esgotado. Mas quando a tensão do Gate2 sobe para 1,2 V, a banda de energia pull-down do canal sob o Gate2 não pode criar uma barreira eficaz para evitar que os elétrons fluam para o lado do dreno. A Figura 7b e sua inserção mostram, respectivamente, a densidade de corrente total depois de ler "0" quando a tensão do Gate2 é 1 V e 0,8 V. A densidade de corrente óbvia pode ser encontrada claramente na região do canal sob o Gate2 quando a tensão do Gate2 é 1 V, que será dar origem à leitura mais alta da corrente “0”. Portanto, 0,8 V é considerado a tensão ótima do Gate2 para o processo de leitura.

a Diagrama de banda de energia e b densidade de corrente total após ler “0”. a , b A banda de energia e a densidade de corrente total após a leitura “0”, respectivamente. A banda de energia é extraída a 3 nm abaixo do óxido de porta

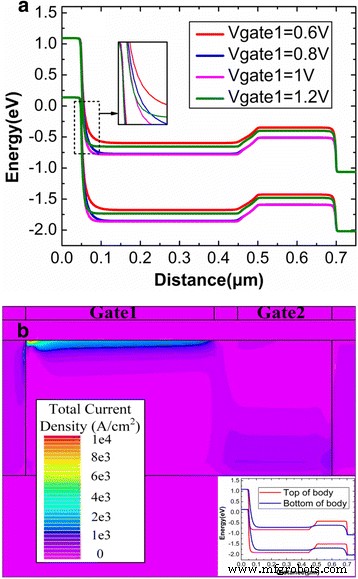

Finalmente, a otimização do viés Gate1 também é conduzida. A Figura 8a mostra a variação da banda de energia superior com a tensão Gate1. A largura da barreira BTBT no lado da fonte diminui gradualmente com o aumento da tensão do Gate1, mas essa tendência decrescente começa a saturar quando a tensão do Gate1 é maior do que 1 V. E a tensão do Gate1 de 1 V não pode trazer grande influência na leitura “0 ”Operação, que foi demonstrado pela Fig. 7b. Portanto, 1 V é considerado a polarização ótima do Gate1 durante a operação de leitura.

a Diagrama de banda de energia e b densidade de corrente total após ler “1”. a , b A banda de energia e a densidade de corrente total após a leitura “1”, respectivamente. A banda de energia é extraída a 3 nm abaixo do óxido de porta

Através da análise acima, o poço de potencial profundo é formado apenas no topo do canal sob o Gate2 após escrever “1”. Portanto, na região do canal sob o Gate2, a banda de energia na parte superior do canal é muito mais alta do que na parte inferior do canal. Isso demonstra que haverá uma barreira no topo do canal sob o Gate2 durante a leitura “1”. A inserção da Fig. 8b representa a banda de energia na parte superior e inferior do canal após a leitura “1”. Pode-se descobrir claramente que existe uma barreira de canal mais alta entre o Gate1 e o Gate2 na parte superior do canal, mas essa barreira não existe na parte inferior do canal. Portanto, o caminho de condução está no topo do canal sob o Gate1 e na parte inferior do canal sob o Gate2 durante a leitura "1", o que pode ser claramente demonstrado pela densidade de corrente na Fig. 8.

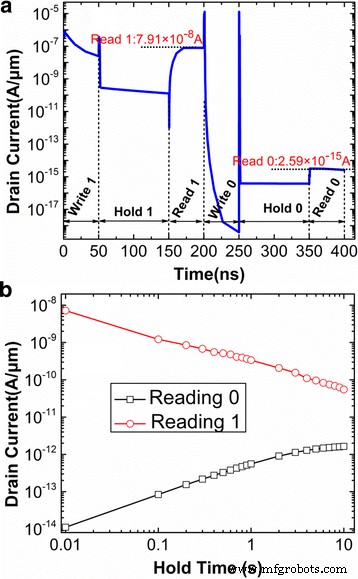

Aplicando a condição de programação otimizada acima, a resposta transitória da célula DG-TFET DRAM é mostrada na Fig. 9. Os tempos de escrita e leitura são ajustados para 50 ns, e o tempo de espera é ajustado para 100 ns. Na Fig. 9a, a proporção atual de leitura de “1” para leitura de “0” é tão alta quanto 10 7 , que é muito maior do que 10 2 ~ 10 3 na referência [16, 18, 23]. Além disso, quando o tempo de espera aumenta para 10 s, a proporção de corrente ainda excede 10. Na referência [16], quando o tempo de espera é aumentado para 2 s, a proporção de corrente é apenas cerca de 10. Portanto, o RT do DG-TFET DRAM com a condição de programação otimizada é superior a 2 s. Portanto, a condição de programação otimizada faz com que a célula DG-TFET DRAM obtenha não apenas a relação de corrente de leitura mais alta, mas também o RT maior. Além disso, a leitura de corrente “0” com tensão de programação otimizada é muito menor que a da referência [16, 18, 22, 23], o que permite atender à aplicação de menor potência.

a Correntes de drenagem transitórias na seqüência da operação; b variação da corrente de leitura com o tempo de espera. a A corrente transitória da célula DGTFET DRAM durante as operações de gravação, retenção e leitura. b As variações de leitura "1" e leitura "0" são correntes com os diferentes tempos de furação

Conclusões

A diretriz de otimização detalhada da condição de programação para DRAM DG-TFET é proposta neste artigo usando a ferramenta de simulação Silvaco-Atlas. Durante a escrita “1”, o Gate2 com tensão negativa (-1,3 V) cria um poço de potencial, e o BTBT entre o canal e o dreno faz com que os furos se acumulem neste poço de potencial. Durante a escrita “0”, o Gate2 com tensão positiva (1,3 V) faz escapar buracos do poço de potencial. Para a operação de retenção, a pequena tensão negativa (-0,2 V) é aplicada no Gate2 para reter os orifícios, o que pode melhorar a leitura da corrente “1”. Depois de segurar “0”, a barreira do canal sob o Gate2 pode resistir ao fluxo de elétrons em direção ao lado do dreno para reduzir a leitura da corrente “0”. Para a otimização da operação de leitura, a maior tensão Gate1 (1 V) é usada principalmente para aumentar BTBT no lado da fonte durante a leitura "1", enquanto uma tensão Gate2 apropriada (0,8 V) é usada para resistir ao fluxo de elétrons em direção ao dreno durante a leitura “0”. A condição de programação otimizada faz com que o DRAM DG-TFET obtenha a relação de corrente mais alta (10 7 ) da leitura “1” à leitura “0” e tempo de retenção de mais de 2 s. E a leitura extremamente baixa da corrente “0” é útil para a redução do consumo de energia.

Nanomateriais

- Os benefícios do monitoramento remoto, programação remota e manutenção preditiva

- Dominar os desafios da programação e depuração multicore

- Breadboarding e Programação do ATmega328P &ATtiny45 no Atmel Studio 7

- Aproveitando tecnologias baseadas em IoT no canteiro de obras

- Sistema de segurança biométrica baseado no batimento cardíaco humano

- Comentário:entendendo os métodos de programação de robôs

- O processo de projeto e implementação de automação da planta

- Preencha o espaço em branco Exercício de programação CNC Arcos múltiplos

- Preencha o campo em branco Exercício de fresamento de programação CNC

- Preencha o exercício de programação CNC em branco