Pesquisa sobre design de PCB de alta velocidade no sistema de aplicativo incorporado

O sistema eletrônico moderno está se desenvolvendo na tendência de pacote pequeno, grande escala e alta velocidade à medida que a densidade de chips está se tornando cada vez maior em SLSI (super-large-scale integration), o que traz alguns problemas inevitáveis como como analisar e lidar com as interconexões e problemas de empilhamento no projeto de circuitos de alta velocidade. Atualmente, a frequência de rádio de produtos eletrônicos atinge centenas ou milhares de MHz e tanto a borda ascendente quanto a borda descendente tornam-se tão íngremes que as regras de layout da placa de circuito impresso e a constante dielétrica do material do substrato são extremamente cruciais para o desempenho elétrico do sistema no projeto do processo. tais produtos.

Como um processo significativo e um passo na maioria das pesquisas de produtos eletrônicos atuais, o projeto de PCB de alta velocidade tem visto os principais problemas, incluindo problemas de tempo, interferência de ruído e EMI (interferência eletromagnética) cujas soluções estão relacionadas com a operação normal do projeto do sistema.

Agora, os métodos tradicionais de projeto levam à baixa confiabilidade e taxa de sucesso dos produtos, que fornecem alto valor prático e amplas expectativas de mercado para pesquisa em projeto de PCB de alta velocidade em sistema de aplicação embarcado.

Design do Esquema do Sistema

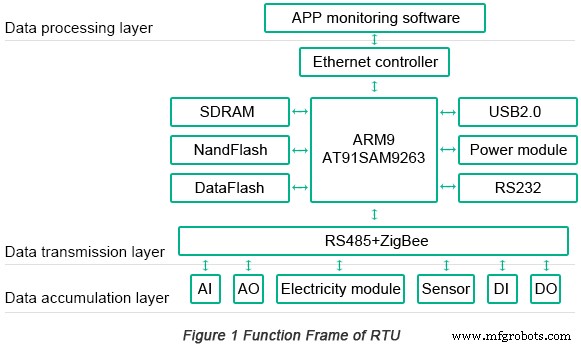

A Figura 1 mostra o quadro funcional da RTU (unidade terminal remota) embutida.

A partir da Figura 1, pode-se observar que este sistema é uma estrutura de comunicação vertical composta por camada de acumulação de dados contendo unidade de energia elétrica, unidade de sensor e unidade de medida de quantidade analógica, camada de transmissão de dados contendo gateway que ajusta os dados na camada de acumulação de dados através do comando do centro de engenharia de recebimento da Internet e camada de processamento de dados que é implementado pelo software de monitoramento APP, armazena e analisa dados em tempo real e faz curvas de dados voltadas para a interface do usuário para que a flexibilidade e a eficiência da administração do acúmulo de dados sejam aumentadas.

Quadro de hardware do sistema RTU

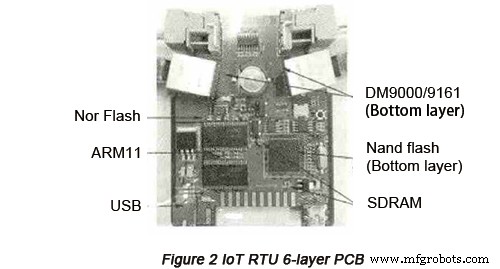

Este hardware de sistema IoT RTU incorporado consiste principalmente em USB2.0, processador AT91SAM9263, CAN, SDRAM, Nand Flash, Data Flash, controlador Ethernet, chip de relógio, interface RS232/485, administração de energia e peças de acumulação de dados.

Operado pelo sistema operacional Linux, este projeto apresenta maiores capacidades de memória e administração de dispositivos para que o agendamento multi-missão em tempo real seja implementado contendo algoritmo complexo e protocolo de comunicação para ser responsável pela conexão de rede, comunicação de dados e acúmulo de configuração. A Figura 2 é a placa de circuito RTU projetada neste artigo.

Suportando a pilha dupla de IPv6 e IPv4, este sistema é capaz de implementar a agilidade e capacidade em tempo real. Em termos de armazenamento de dados, o requisito de armazenamento local pode ser atendido na condição de bloco de comunicação. Em termos de interface de comunicação, possui diferentes interfaces de comunicação de dados de campo, incluindo RS485, RS232 e CAN, suportando o protocolo de comunicação Modbus RTU e atendendo aos requisitos de diferentes interfaces e diferentes taxas de comunicação.

Projeto de PCB do Sistema RTU

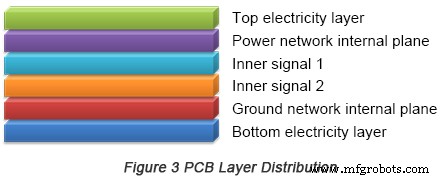

• Design de empilhamento de PCB do sistema

O número de camadas de PCBs geralmente está na faixa de 2 a 32 com base na dificuldade do projeto. O PCB de 6 camadas neste projeto é determinado de acordo com a densidade do pacote de componentes, espaço de roteamento de layout pequeno e alta frequência de sinal. Esta distribuição da camada PCB é ilustrada na Figura 3 abaixo.

A configuração das linhas de tira é escolhida para FLASH e SDRAM neste sistema e o roteamento é implementado no Sinal Interno 1 e Sinal Interno 2.

• Regras de restrição de PCB neste sistema

Durante o projeto de PCB de alta velocidade, a continuidade da impedância e a EMI são muito influenciadas pelo espaçamento, comprimento e largura dos fios e processamento adjacente de loops. A qualidade do layout e do roteamento dos componentes está relacionada com o sucesso do projeto final, de modo que as regras de restrição da PCB devem ser implementadas de forma razoável.

O Hyper Lynx apresenta uma funcionalidade de interferência na análise de gráficos e o modelo IBIS pode ser aplicado para simular com precisão a transmissão de perda, sinais diferenciais e modelo de passagem que muda com a frequência. A rede principal é simulada antes do roteamento por Linha para melhorar a estrutura de empilhamento de PCB e a impedância de roteamento e as regras de restrição de roteamento de rede de PCB de alta velocidade são projetadas antes do resultado da simulação para aumentar a eficiência do projeto.

• Simulação de PCB deste sistema

No processo de projeto de PCB de alta velocidade, um modelo de linha de transmissão ideal é aplicado para simulação de terminal frontal com linhas de sinal limitadas simuladas por uma vez. As linhas de transmissão no terminal traseiro do PCB, no entanto, são na verdade linhas de roteamento do PCB com influência do orifício de passagem e deslocamento dos planos. Nesta circunstância, o resultado de simulação obtido é extremamente confiável.

No processo de projeto do circuito central do sistema, a resistência de correspondência do terminal do sinal de terminal único deve estar na faixa de 40 a 60Ω e o valor do limite de diafonia entre as linhas de sinal de 165mV. Além disso, para tornar os controladores de rede DM9000 e DM9161 auto-adaptáveis para a taxa de velocidade de comunicação de 100Mbps e a impedância diferencial deve estar dentro da categoria de 100±5Ω. A simulação de PCB é implementada pelo software de simulação Hyper Lynx desenvolvido pela Mentor Graphic em SDRAM, linhas diferenciais Ethernet, integridade de energia e EMC.

uma. Projeto SDRAM

No processo de projeto de linha de tira, diafonia e furo passante são as principais causas que levam ao atraso de tempo. Embora o PCB seja preenchido de acordo com as regras de roteamento determinadas pelas ferramentas de simulação de linha, alguns problemas são evitáveis, como muitos pinos de componentes e dimensão limitada do PCB. Portanto, é necessário simular adequadamente várias redes por meio de ferramentas de simulação de placa.

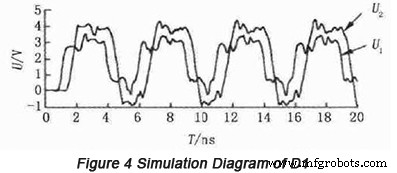

Com base no resultado da simulação, a intensidade de crosstalk da rede analógica EBI_D0 e EBI_D2 é superior a 165mV. As duas redes atacam EBI_D1 e procuram local de acoplamento porque o espaçamento é inadequado entre linhas em forma de serpente na área de marcação amarela. Pode-se ilustrar que o aumento do espaçamento de roteamento ajudará a eliminar tal problema. No entanto, o que realmente nos importa é por que a rede hack sofre uma interferência tão forte. A razão possivelmente está na escolha inadequada do resistor, levando à impedância não compatível. Até agora, a resistência determinada do resistor de terminação é 43,1Ω. Na condição de excitação de 220MHz, a onda de simulação de análise da rede EBI_D1 é mostrada na Figura 4 abaixo.

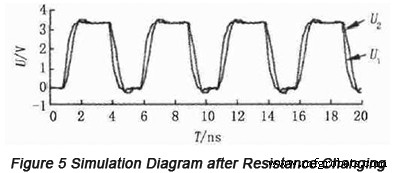

Com base na Figura 4, a descontinuidade da impedância ocorre na linha de transmissão EMI_D1 e a deformação ocorre nas ondas de sinal. Embora a falha de partida do sistema não possa ser causada, a estabilidade da operação do produto dificilmente pode ser garantida. De volta à simulação da placa, são aplicados furos passantes e simulação de danos para alterar a resistência do terminal de EBI_D0 e EBI_D1 para 46,9Ω. Portanto, o diagrama de simulação de crosstalk após a mudança de resistência é exibido na Figura 5 abaixo.

Com base nesta figura, pode-se ilustrar que o sinal da rede foi melhorado e a intensidade de interferência gerada em EBI_D1 foi evidentemente reduzida.

b. Projeto de barramento diferencial da Internet

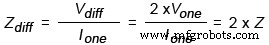

Com atributos de interconexões de alta velocidade e 3GIO, o módulo de simulação de placa desenvolvido pela Hyper Lynx aplica caminho de dados serial super rápido e tecnologia de sincronização de fonte baseada em barramento de sinal diferencial, fornecendo esquema de solução conveniente e altamente eficaz para design de PCB de alta velocidade. Tanto o DM9000 quanto o DM9161 neste sistema possuem dois pares de barramento diferencial de sinal de alta velocidade:TX+, TX- e RX+, RX- com impedância diferencial de 100Ω. Devido à teoria da transmissão, a impedância diferencial pode ser calculada com base na fórmula: .

.

Nesta fórmula, Z refere-se à impedância de transmissão de cada linha de sinal, tendo um efeito crucial na distância de comunicação e na capacidade de resistência ao ruído. Aqui o DM9000 é selecionado para transmitir diferencial para a rede TP_E_TX+ e TP_E_TX-. A fim de reduzir o efeito de reflexão, um resistor de 100Ω é colocado em paralelo nas linhas de sinal com furos passantes aplicados.

c. Projeto de integridade de energia deste sistema

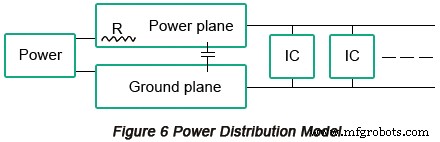

A Figura 6 é um modelo básico de distribuição de energia no qual a corrente é transmitida para cada portadora através das camadas de energia e depois para a camada de terra.

No processo de projeto de PCB de alta velocidade, o consumo de energia em cada unidade deve ser calculado no sistema de circuito com a largura da rede de energia corretamente distribuída e adequadamente amplificada.

A integridade de energia de 6 camadas pode ser resumida da seguinte forma:a queda de pressão máxima é de 2,1mV, próximo a 0,06%; a densidade máxima de corrente é 16,3mA/m²; dentro de uma categoria adequada, se a densidade de corrente ultrapassar 50 mA/m², a temperatura do PCB aumentará, o que influencia o chip principal e as linhas de sinal no processo de operação. O aumento da largura do cobre é capaz de diminuir a densidade de corrente e aumentar a espessura dos condutores de sinal é útil para diminuir a temperatura do PCB.

d. Análise de compatibilidade eletromagnética do sistema

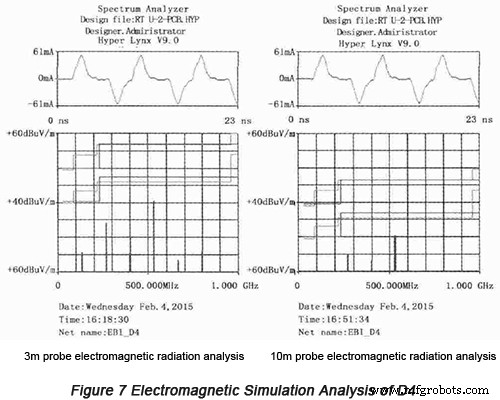

A interferência eletromagnética é geralmente transmitida como portadora com sinais úteis na forma de acoplamento. Neste projeto, o software de simulação Hyper Lynx é aplicado para analisar a intensidade de radiação do PCB após o projeto preliminar. A linha de sinal crucial, D4, é captada entre ARM9 e SDRAM com posições de sonda de 3m e 10m, respectivamente. Sob a situação de fonte de excitação de 220MHz, ambos os dados de simulação de padrão internacional FCC e CISPR podem ser obtidos, exibidos na Figura 7 abaixo.

Com base no resultado da simulação, a curta distância do PCB leva a alta radiação da placa de circuito e a radiação muda com a mudança das frequências do sinal. No processo de projeto de circuito de alta velocidade, a anti-interferência do PCB pode ser otimizada enquanto a radiação de ruído deve ser reduzida.

Recursos úteis

• Dicas de layout de alta velocidade

• Técnicas de roteamento de PCB de alta velocidade para reduzir a influência de EMI

• Mal-entendidos e estratégias no projeto de PCB de alta velocidade

• Componente incorporado Tecnologia de Fabricação de PCB

• Tecnologia Embutida e Procedimento de Montagem de PCB Embutida de Componentes

• Serviço de Fabricação de PCB Completo da PCBCart - Várias opções de valor agregado

• Serviço Avançado de Montagem de PCB da PCBCart - Comece a partir de 1 peça

Tecnologia industrial

- Software de layout de PCB

- Considerações de layout de PCB

- Tutorial de design de placa de circuito impresso do Ultiboard

- 3 técnicas de roteamento no projeto de circuito de sinal de alta velocidade PCB

- Dicas de layout de alta velocidade

- Considerações de design térmico de PCB

- Processamento isométrico diferencial e verificação de simulação de projeto de PCB de alta velocidade

- Os erros mais comuns que os engenheiros tendem a cometer no projeto de PCB

- Análise de integridade de sinal e projeto de PCB em circuito misto analógico-digital de alta velocidade

- Desafios de projeto de PCB de alta velocidade sobre integridade do sinal e suas soluções