As tarefas do sistema de exibição são usadas principalmente para exibir mensagens informativas e de depuração para rastrear o fluxo de simulação de arquivos de log e também ajuda a depurar mais rapidamente. Existem diferentes grupos de tarefas de exibição e formatos nos quais eles podem imprimir val

Os relógios são fundamentais para a construção de circuitos digitais, pois permitem que diferentes blocos estejam sincronizados entre si. Propriedades de um relógio As principais propriedades de um relógio digital são sua frequência que determina o período do relógio , seu ciclo de trabalho e a fa

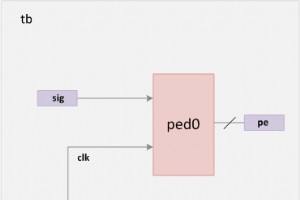

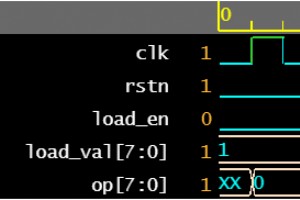

O design Verilog e o testbench normalmente têm muitas linhas de código compostas por always ou initial blocos, atribuições contínuas e outras instruções de procedimento que se tornam ativas em momentos diferentes no decorrer de uma simulação. Cada mudança no valor de um sinal no modelo Verilog é c

A simulação Verilog depende de como o tempo é definido, pois o simulador precisa saber o que significa #1 em termos de tempo. O `timescale A diretiva do compilador especifica a unidade de tempo e a precisão dos módulos que a seguem. Sintaxe `timescale <time_unit>/<time_precision>

Verilog é uma linguagem de descrição de hardware e não é necessário que os projetistas simulem seus projetos RTL para poder convertê-los em portas lógicas. Então, qual é a necessidade de simular? A simulação é uma técnica de aplicação de diferentes estímulos de entrada ao projeto em momentos dif

Primitivas padrão Verilog como nand e not pode nem sempre ser fácil ou suficiente para representar uma lógica complexa. Novos elementos primitivos chamados UDP ou primitivas definidas pelo usuário pode ser definido para modelar lógica combinacional ou sequencial. Todos os UDPs têm exatamente uma s

O Verilog também fornece suporte para modelagem de nível de transistor, embora raramente seja usado por designers atualmente, pois a complexidade dos circuitos exigiu que eles mudassem para níveis mais altos de abstrações, em vez de usar a modelagem de nível de switch. NMOS/PMOS module des (in

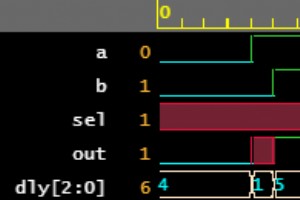

Os elementos digitais são entidades binárias e só podem conter um dos dois valores - 0 e 1. No entanto, a transição de 0 para 1 e 1 para 0 tem um atraso de transição e também cada elemento de porta para propagar o valor da entrada para a saída. Por exemplo, uma porta AND de duas entradas tem que m

Algumas das principais primitivas internas foram discutidas no artigo anterior e seria bom ver alguns exemplos práticos de uso simples de and , nor e not portões. Observe que para escrever o código Verilog usando portas, é necessário que você saiba como conectar os elementos. Isso é muito diferent

A maioria dos projetos digitais são feitos em um nível mais alto de abstração como RTL, embora às vezes se torne intuitivo construir circuitos determinísticos menores em um nível mais baixo usando elementos combinacionais como e e ou . A modelagem feita neste nível geralmente é chamada de modelagem

A maioria das linguagens de programação tem um recurso característico chamado escopo que define a visibilidade de certas seções de código para variáveis e métodos. O escopo define um namespace para evitar a colisão entre diferentes nomes de objetos dentro do mesmo namespace. Verilog define um no

As instruções de atraso Verilog podem ter atrasos especificados no lado esquerdo ou no lado direito do operador de atribuição. Atrasos entre tarefas // Delay is specified on the left side #<delay> <LHS> = <RHS> Uma atribuição entre tarefas A instrução de atraso tem valor d

Existem dois tipos de controles de tempo no Verilog - atraso e evento expressões. O atraso O controle é apenas uma maneira de adicionar um atraso entre o momento em que o simulador encontra a instrução e quando ele realmente a executa. A expressão de evento permite que a instrução seja atrasada até

A Verilog suporta algumas diretivas de compilador que essencialmente direcionam o compilador a tratar o código de uma determinada maneira. Por exemplo, uma parte do código pode representar uma implementação de um determinado recurso e deve haver alguma maneira de não incluir o código no design se o

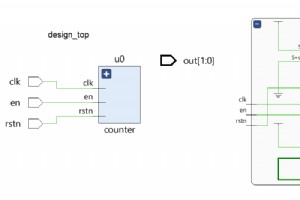

Os parâmetros são construções Verilog que permitem que um módulo seja reutilizado com uma especificação diferente. Por exemplo, um somador de 4 bits pode ser parametrizado para aceitar um valor para o número de bits e novos valores de parâmetro podem ser passados durante a instanciação do módulo.

Um function destina-se a fazer algum processamento na entrada e retornar um único valor, enquanto um task é mais geral e pode calcular vários valores de resultado e devolvê-los usando saída e dentro argumentos de tipo. As tarefas podem conter elementos demorados de simulação, como @ , postado e outr

Muitas vezes, encontramos certos trechos de código repetitivos e chamados várias vezes dentro da RTL. Eles geralmente não consomem tempo de simulação e podem envolver cálculos complexos que precisam ser feitos com diferentes valores de dados. Nesses casos, podemos declarar um function e coloque o có

O case A instrução verifica se a expressão fornecida corresponde a uma das outras expressões na lista e ramifica de acordo. Normalmente é usado para implementar um multiplexador. A construção if-else pode não ser adequada se houver muitas condições a serem verificadas e sintetizar em um codificador

A for loop é o loop mais usado em software, mas é usado principalmente para replicar lógica de hardware em Verilog. A ideia por trás de um for loop é iterar um conjunto de instruções fornecidas dentro do loop, desde que a condição dada seja verdadeira. Isso é muito semelhante ao while loop, mas é us

O comportamento do hardware não pode ser implementado sem instruções condicionais e outras formas de controlar o fluxo da lógica. A Verilog possui um conjunto de blocos de fluxo de controle e mecanismos para alcançar o mesmo. if-else-if Esta declaração condicional é usado para tomar uma decisão so

Verilog