Bloqueando Bloqueando instruções de atribuição são atribuídas usando = e são executados um após o outro em um bloco procedural. No entanto, isso não impedirá a execução de instruções que são executadas em um bloco paralelo. module tb; reg [7:0] a, b, c, d, e; initial begin a = 8hDA

Colocar valores em redes e variáveis é chamado de atribuições. Existem três formas básicas: Procedimento Contínuo Procedimento contínuo Valores legais do LHS Uma atribuição tem duas partes - lado direito (RHS) e lado esquerdo (LHS) com um símbolo igual (=) ou um símbolo menor que igual (<=) entr

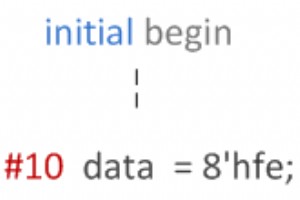

Existem maneiras de agrupar um conjunto de instruções que são sintaticamente equivalentes a uma única instrução e são conhecidas como instruções de bloco . Existem dois tipos de instruções de bloco:sequenciais e paralelas. Sequencial As instruções são encapsuladas usando begin e end palavras-chave

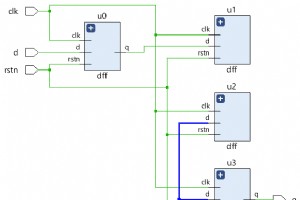

Um exemplo anterior explorou um detector de sequência simples. Aqui está outro exemplo para um detector de padrão que detecta um padrão ligeiramente mais longo. Projeto module det_110101 ( input clk, input rstn, input in, output out )

Um exemplo muito comum de um FSM é o de um detector de sequência em que se espera que o design do hardware detecte quando um padrão fixo é visto em um fluxo de bits binários que são inseridos nele. Exemplo module det_1011 ( input clk, input rstn, input in,

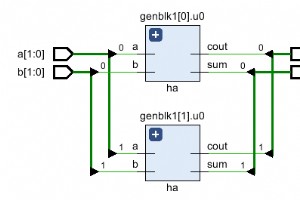

A generate block permite multiplicar instâncias de módulo ou realizar instanciação condicional de qualquer módulo. Ele fornece a capacidade de o projeto ser construído com base nos parâmetros Verilog. Essas instruções são particularmente convenientes quando a mesma operação ou instância de módulo pr

Todo o código comportamental é escrito dentro de module e endmodule . Portanto, seja qual for o design digital que você pretende criar, ele ficará dentro de um module quadra. Pode ou não ter portas definidas - permite que os sinais entrem no bloco como input ou escape do bloco como output . Módulo

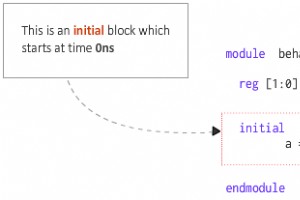

Um conjunto de instruções Verilog geralmente é executado sequencialmente em uma simulação. Essas instruções são colocadas dentro de um procedural quadra. Existem basicamente dois tipos de procedimentos blocos em Verilog - inicial e sempre Sintaxe initial [single statement] initial begin

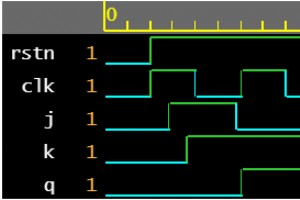

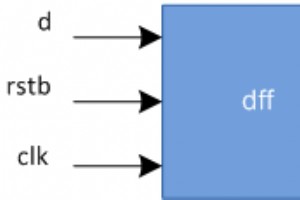

Um artigo anterior mostrou diferentes exemplos de uso de um always bloco para implementar a lógica combinacional. Um always bloco também é usado principalmente para implementar sequencial lógica que tem elementos de memória como flip-flops que podem armazenar valores. Flip Flop JK Um flip-flop JK

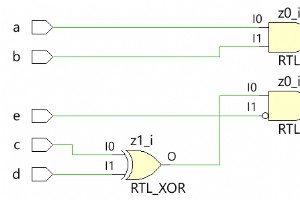

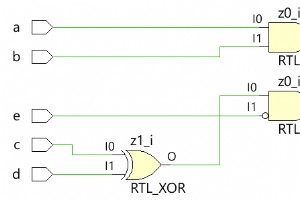

O bloco verilog always pode ser usado para lógica sequencial e combinacional. Alguns exemplos de design foram mostrados usando um assign declaração em artigo anterior. O mesmo conjunto de designs será explorado a seguir usando um always quadra. Exemplo nº 1:lógica combinacional simples O código mo

Um always bloco é um dos procedimentos blocos em Verilog. As instruções dentro de um bloco sempre são executadas sequencialmente. Sintaxe always @ (event) [statement] always @ (event) begin [multiple statements] end O always bloco é executado em algum evento particular. O evento é defi

Fios e variáveis multi-bit Verilog podem ser agrupados para formar um fio ou variável multi-rede maior usando concatenação operadores { e } separados por vírgulas. A concatenação também pode ter expressões e constantes de tamanho como operandos, além de fios e variáveis. O tamanho de cada operan

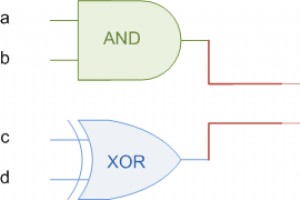

Dados que não podem ser processados são inúteis, sempre haverá alguma forma de cálculo necessária em circuitos digitais e sistemas de computador. Vejamos alguns dos operadores em Verilog que permitiriam que as ferramentas de síntese realizassem os elementos de hardware apropriados. Operadores ari

A instrução de atribuição verilog é normalmente usada para conduzir continuamente um sinal de wire tipo de dados e é sintetizado como lógica combinacional. Aqui estão mais alguns exemplos de design usando o assign declaração. Exemplo nº 1:lógica combinacional simples O código mostrado abaixo imple

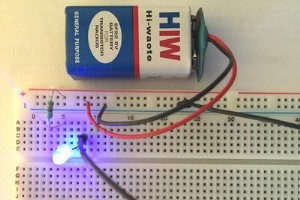

Sinais do tipo wire ou um tipo de dados semelhante a um fio requer a atribuição contínua de um valor. Por exemplo, considere um fio elétrico usado para conectar peças em uma placa de ensaio. Contanto que a bateria de +5V seja aplicada a uma extremidade do fio, o componente conectado à outra extremid

Como vimos em um artigo anterior, projetos maiores e complexos são construídos integrando vários módulos de forma hierárquica. Os módulos podem ser instanciados dentro de outros módulos e portas dessas instâncias pode ser conectado com outros sinais dentro do módulo pai. Essas conexões de porta po

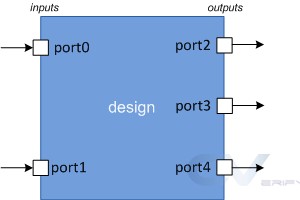

As portas são um conjunto de sinais que atuam como entradas e saídas para um módulo específico e são a principal forma de comunicação com ele. Pense em um módulo como um chip fabricado colocado em um PCB e fica bastante óbvio que a única maneira de se comunicar com o chip é através de seus pinos. As

Um module é um bloco de código Verilog que implementa uma determinada funcionalidade. Os módulos podem ser incorporados a outros módulos e um módulo de nível superior pode se comunicar com seus módulos de nível inferior usando suas portas de entrada e saída. Sintaxe Um módulo deve estar entre modu

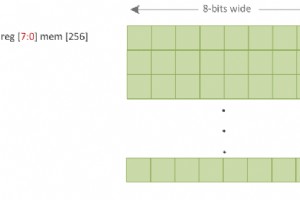

Uma matriz declaração de uma rede ou variável pode ser escalar ou vetorial. Qualquer número de dimensões pode ser criado especificando um intervalo de endereços após o nome do identificador e é chamado de matriz multidimensional. Arrays são permitidos em Verilog para reg , wire , integer e real tipo

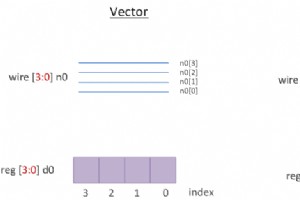

Verilog precisa representar bits individuais, bem como grupos de bits. Por exemplo, um elemento sequencial de bit único é um flip-flop. No entanto, um elemento sequencial de 16 bits é um registrador que pode conter 16 bits. Para isso, a Verilog tem escalar e vetor redes e variáveis. Escalar e Vetor

Verilog