IBM na SPIE:Sete avanços para além dos chips 7nm

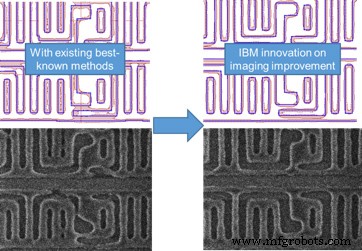

Figura 1 :Melhoria na otimização de contraste na fiação de metal bidimensional demonstrada com litografia EUV. Com o tipo de melhoria ilustrado à direita, recursos 20-30 {ccf696850f4de51e8cea028aa388d2d2d2eef894571ad33a4aa3b26b43009887} menores do que aqueles do nó de 7 nm podem ser impressos de forma mais robusta e a variabilidade física / elétrica pode ser drasticamente reduzida.

Em Investigação de pilhas de máscaras alternativas em litografia EUV, Martin Burkhardt simula o desempenho de novos materiais que não estão sendo usados atualmente para máscaras EUV. Ao considerar toda a tabela periódica, ele consegue ilustrar que as máscaras EUV que proporcionam um contraste ainda melhor estão ao nosso alcance. Na verdade, a fabricação de máscaras com alguns desses materiais permitiria padrões de maior fidelidade em um wafer de silício sem qualquer mudança adicional na tecnologia EUV e, assim, permitiria que a indústria escalasse facilmente além de 7 nm.

Em Análise abrangente de rugosidade de borda e largura de linha para litografia EUV , Ravi Bonam ilustra como pequenas imperfeições e oscilações em uma linha de fiação podem ser caracterizadas claramente e, ao fazer isso, mostra quais condições produzem os recursos mais retos, essenciais para melhorar a capacidade de fabricação do processo de padronização EUV e o desempenho e rendimento do chip.

Em Fundamentos de EUV resistir a interações com máscara rígida inorgânica , Dario Goldfarb procura melhorar a pilha de filmes de material de padronização (o ponto de transferência do padrão para o wafer), melhorando as interações físicas e químicas nas interfaces entre esses filmes, que muitas vezes não gostam de grudar uns nos outros. Ele aproveita essa compreensão para criar interações químicas específicas para manter esses materiais juntos (mostrado na Figura 2), o que é fundamental para garantir que essas formas minúsculas de padrão EUV sejam capazes de permanecer no lugar por tempo suficiente para transferir seus padrões para o substrato abaixo.

Figura 2 :Uma máscara EUV que antes era impossível de padronizar em uma máscara de silicone inorgânica agora pode ser claramente padronizada após a customização da superfície feita sob medida para a combinação de máscara / máscara dura.

Em um tema semelhante à palestra de Dario Goldfarb, Indira Seshadri demonstra em Ultrathin EUV patterning stack usando um pincel de polímero como uma camada de promoção de adesão , que ao empregar um material semelhante a um polímero que faz a ponte entre os pequenos recursos padronizados de EUV e o substrato subjacente, esses padrões de resolução muito alta podem ser gravados no substrato abaixo e reter a forma de design pretendida, fundamental para garantir chips rendíveis neste comprimento escalas.

Com tantas novas soluções de filme fino em jogo, a capacidade de discernir e melhorar processos dignos de fabricação no início das fases de pesquisa é fundamental. Em uma palestra intitulada Reduzindo a densidade de defeitos em pilhas de filmes de padronização EUV , Luciana Meli demonstra estudos de caso sistemáticos, usando um híbrido de técnicas de inspeção de defeitos disponíveis, para mostrar as melhorias de processo e materiais necessárias para fornecer a baixa defeituosa necessária para a capacidade de fabricação de 7 nm e além do EUV.

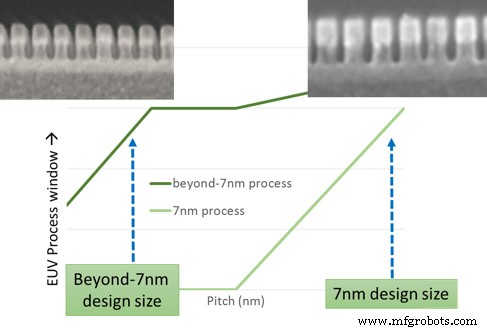

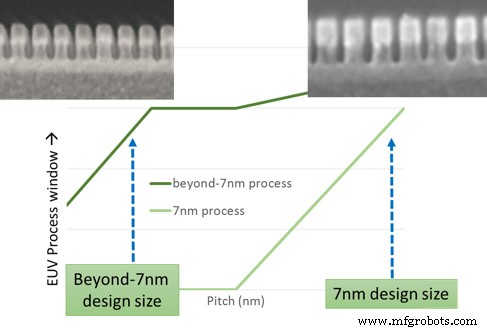

Reunindo muitos desses conceitos de melhoria de imagem e materiais, Anuja De Silva apresentará uma palestra intitulada Desenvolvimento de padrões de exposição única para litografia EUV , apresentando padronização bem-sucedida de circuitos de fiação nas dimensões de 30nm e abaixo exigidos além do nó de 7nm. A capacidade de conseguir isso representa um grande salto em relação aos recursos disponíveis inicialmente para o nó de 7nm (consulte a Figura 3) e pode realmente melhorar o próprio nó de 7nm, embora ela vá destacar os desafios que ainda permanecem para permitir o funcionamento total de chips rendíveis em dimensões exigidas para tecnologia além de 7 nm.

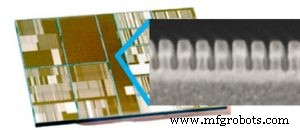

Um chip de 7 nm tem 20 bilhões de transistores no espaço aproximadamente do tamanho de uma unha. Eles entrarão em sistemas e dispositivos, ampliando os recursos - e a Lei de Moore - para realizar tarefas cada vez mais exigentes em análise de dados, computação cognitiva e tudo o que a próxima geração de aplicativos móveis comporta. O trabalho apresentado na SPIE este ano empurra a indústria para mais perto de soluções de padronização que não apenas tornam o processo de 7 nm mais robusto com EUV de exposição única, mas também permitem um dimensionamento adicional para obter ainda mais benefícios de potência / desempenho nos próximos anos.

Figura 3 :A inovação em vários aspectos do processo de padronização permite que a IBM forneça uma capacidade de processo de padronização holística para fornecer os tamanhos de recursos necessários além do nó de 7 nm.

Outras apresentações da IBM no SPIE 2017

Otimização da intenção do projeto no nó além de 7 nm:a interseção das técnicas de mitigação estocástica DTCO e EUVL , Michael Crouse, Nicole Saulnier, Derren Dunn

Investigação de pilhas de máscaras alternativas em litografia EUV , Martin Burkhardt

Decomposição do TCC usando kernels não coerentes para cálculo mais rápido de imagens litográficas, Alan Rosenbluth

Desenvolvimento de máscaras contendo Ti por meio de deposição PEALD, Anuja De Silva

Opções de padronização de DSA para aplicativos lógicos e de memória, Charlie Liu

Estudo elétrico do processo de redução de DSA e efeito de retificação de CD em sub-60nm usando veículo de teste EUV, Cheng Chi

Alcançando a sobreposição verdadeira em nós avançados, Chiew-Seng Koay

Estratégias sem cobertura para controle de orientação de copolímeros de alto χBlock totalmente orgânicos, Dan Sanders

Identificação e análise de sensibilidade de confiabilidade de um sistema de regras básicas correlacionado (arco de projeto), Eric Eastman

Desenvolvimento rápido e avançado de modelo DSA 3D e calibração para co-otimização de tecnologia de projeto, Kafai Lai

Impactos inesperados de gases RIE em filmes litográficos, Martin Glodde

Previsão de testes elétricos usando metrologia híbrida e aprendizado de máquina, Mary Breton

Reduzindo LER em Si e SiN por meio da otimização RIE para aplicações de guia de ondas fotônicas, Nathan Marchack

Estratégias de padronização de automontagem direcionadas para aplicativos de memória de mudança de fase, R. Bruce

Caracterização de materiais para integração de processos de dispositivos de porta multicanal (GAA), Raja Muthinti

Análise abrangente de rugosidade de borda e largura de linha para litografia EUV, Ravi Bonam

Nanomateriais

- Alvo de liga de tungstênio titânio para chips

- Alvo de tungstênio de alta pureza para chips semicondutores

- Vá além dos requisitos mínimos de rede do Skypes para obter melhores resultados

- Argumentando sobre chips neuromórficos para computação IA

- Cientistas da IBM inventam um termômetro para nanoescala

- IBM 5 em 5:laboratórios médicos "em um chip" servirão como detetives de saúde para rastrear doenças em nanoescala

- Pesquisadores da IBM levam para casa o prêmio de inovação para pesquisa de semicondutores

- IBM apresenta uma arquitetura Hybrid Blockchain para a Internet das coisas

- Além do AIOps:observabilidade para operações de TI eficazes

- Os sete requisitos para usinagem otimizada

Nossa equipe IBM está apresentando sete artigos na conferência de litografia avançada da Sociedade Internacional de Óptica e Fotônica (SPIE) 2017 desta semana focado na exploração e capacitação de tecnologia além do nó de 7 nm. E começa com a litografia ultravioleta extrema (EUV).

Nossa equipe IBM está apresentando sete artigos na conferência de litografia avançada da Sociedade Internacional de Óptica e Fotônica (SPIE) 2017 desta semana focado na exploração e capacitação de tecnologia além do nó de 7 nm. E começa com a litografia ultravioleta extrema (EUV).