A otimização da engenharia do espaçador para DRAM sem capacitor baseada no transistor de túnel de porta dupla

Resumo

A DRAM baseada no FET de tunelamento de porta dupla (DGTFET) tem as vantagens de uma estrutura sem capacitor e um alto tempo de retenção. Neste artigo, a otimização da engenharia do espaçador para DGTFET DRAM é sistematicamente investigada pela ferramenta Silvaco-Atlas para melhorar ainda mais seu desempenho, incluindo a redução da corrente de leitura “0” e extensão do tempo de retenção. Os resultados da simulação mostram que os espaçadores nos lados da fonte e do dreno devem aplicar os dielétricos low-k e high-k, respectivamente, o que pode aumentar a leitura da corrente “1” e reduzir a leitura da corrente “0”. Aplicando esta engenharia de espaçador otimizada, o DGTFET DRAM obtém o desempenho ideal - leitura extremamente baixa de corrente “0” (10 −14 A / μm) e grande tempo de retenção (10s), o que diminui o consumo de energia estática e a taxa de atualização dinâmica. E a leitura baixa da corrente “0” também aumenta sua proporção de corrente (10 7 ) da leitura “1” para a leitura “0”. Além disso, a análise sobre escalabilidade revela sua deficiência inerente, que oferece uma direção de investigação mais aprofundada para DGTFET DRAM.

Histórico

Com a redução da geometria do dispositivo, a memória de acesso aleatório (DRAM) dinâmica de 1 transistor (1T) -1 capacitor (1C) encontrou dificuldade em reduzir, porque é difícil para o capacitor reduzir seu tamanho [1,2,3] . A indústria de memória tem proposto alguns métodos eficazes para o empacotamento de memórias de alta densidade, como novos materiais e novas estruturas de dispositivos [4, 5]. A DRAM 1T com a estrutura sem capacitor foi relatada pela primeira vez no início dos anos 90 [6, 7] e atrai cada vez mais atenção. Na DRAM 1T, o estado 1 (armazenamento de portadora) é obtido de quatro maneiras:ionização de impacto [8], transistor de junção bipolar [9], tunelamento banda-a-banda (BTBT) [10] e tunelamento de porta [11].

O transistor de efeito de campo de tunelamento (TFET) baseado no BTBT foi considerado uma alternativa potencial para o MOSFET devido à maior relação de comutação e corrente de estado desligado extremamente baixa [12,13,14]. As vantagens do TFET - baixa corrente no estado desligado e fraca dependência da temperatura - são extraordinariamente benéficas para DRAM. Especialmente, a baixa corrente no estado desligado pode reduzir a leitura de corrente “0” e o consumo de energia estática. Atualmente, existem alguns grupos trabalhando na investigação do TFET DRAM [15,16,17,18,19,20]. É relatado que TFET DRAM tem a corrente “0” de leitura baixa e tempo de retenção alto (RT). Entre esses TFET DRAMs, o TFET de porta dupla (DGTFET) DRAM é o mais proeminente [19, 20]. Em DGTFET DRAM, as operações de escrita e leitura são baseadas no BTBT. A pesquisa mostra que a leitura da corrente “0” do DRAM DGTFET pode chegar a 1 nA / μm, que é muito menos do que o DRAM 1T1C tradicional. E o RT de 2 s é muito superior ao valor alvo de 64 ms, que geralmente é definido como tempo de atualização dinâmica no sistema de computação [21]. O RT do DGTFET DRAM ainda é maior que 300 ms quando a temperatura é elevada para 85 ° C, o que autoriza sua praticabilidade em condições adversas. Além disso, no DGTFET DRAM, a eliminação de capacitores com tamanho maior também exibe sua competitividade em embalagens de alta densidade. Essas vantagens indicam plenamente que é necessário estudar DGTFET DRAM. Embora essas pesquisas tenham demonstrado que DGTFET tem desempenho superior do que o DRAM 1T1C convencional, os resultados (RT e leitura de corrente “0”) não são ideais devido ao fato de que a configuração do dispositivo de DGTFET não é otimizada.

Neste artigo, a engenharia do espaçador do DGTFET é otimizada para fazer o DGTFET obter o desempenho ideal. Em TFETs, os dielétricos espaçadores têm forte influência no BTBT [22, 23]. No DGTFET, os espaçadores nos lados da fonte e do dreno são fechados para junções de tunelamento, de modo que afetam muito o desempenho do DRAM DGTFET. Este artigo analisa sistematicamente as influências do dielétrico do espaçador (dielétricos de baixo k ou alto k) em cada espaçador no DGTFET DRAM e propõe uma engenharia de espaçador otimizada. Pela otimização da engenharia do espaçador, a leitura da corrente “0” é reduzida para 10 −14 A / μm e RT podem chegar a 10 s. Finalmente, a escalabilidade do DGTFET DRAM com a engenharia do espaçador otimizada também é discutida neste trabalho.

Estrutura do dispositivo e método de simulação

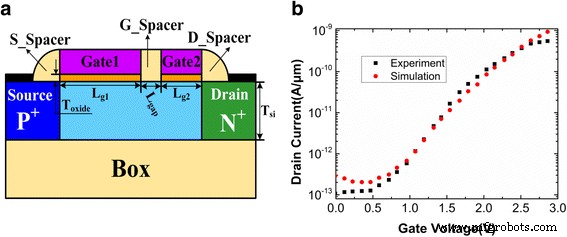

O DGTFET com uma configuração P-I-N é ilustrado na Fig. 1a. As regiões de origem e drenagem são P + dopagem (10 20 / cm 3 ) e N + dopagem (10 20 / cm 3 ), respectivamente. A região intrínseca do canal é dividida em duas partes:região Gate1 com o N + polissilício e região Gate2 com o P + polissilício. Há um pequeno intervalo entre o Gate1 e o Gate2. O P + polysilicon Gate2 pode criar, bem como manter o poço físico para armazenamento de carga e substituir a DRAM baseada em TFET convencional que utiliza um P + região do bolso como área de armazenamento. Enquanto para um N + polissilício Gate1, a concentração do orifício na região subjacente entre Gate1 e Gate2 é baixa, o que é útil para a operação de leitura. Assim, um P + polysilicon Gate2 optou por criar uma região de armazenamento mais profunda que poderia facilitar um maior tempo de retenção, enquanto um N + O polissilício Gate1 é selecionado para controlar o mecanismo de tunelamento durante a operação de leitura [20]. Na Fig. 1a, o S_Spacer e D_Spacer referem-se aos espaçadores nos lados da fonte e do dreno, respectivamente. O G_spacer se refere ao espaçador entre o Gate1 e o Gate2. O material padrão dos espaçadores é SiO 2 . Os parâmetros padrão do dispositivo são os seguintes:espessura do filme de silício (T si ) é de 20 nm, o comprimento do Gate1 (L g1 ) é 400 nm, comprimento do Gate2 (L g2 ) é de 200 nm, comprimento da lacuna de porta (L lacuna ) é de 50 nm e a espessura do óxido de porta HfO 2 (T óxido ) é 3 nm.

a Esquema da célula DRAM TFET de porta dupla (DGTFET). b Comparação entre a característica de transferência simulada com resultados experimentais para SOI TFET [25]

As simulações do DRAM DGTFET são realizadas no Silvaco Atlas utilizando um modelo BTBT não local. O modelo de tunelamento não local BTBT leva em consideração a variação espacial das bandas de energia e geração / recombinação do tipo de portadora oposta [24]. Os parâmetros do modelo de tunelamento são calibrados de acordo com os resultados experimentais do SOI TFET [25]. A massa do elétron e do túnel do buraco é ajustada para 0,22 m 0 e 0,52 m 0 , respectivamente, onde m 0 é a massa restante do elétron. A característica de transferência simulada do SOI TFET é consistente com os resultados experimentais, conforme mostrado na Fig. 1b, que autoriza os modelos aplicados neste trabalho. Devido ao forte doping nas regiões de origem e drenagem, o modelo de estreitamento de bandgap e as estatísticas de Fermi-Dirac também são considerados. Além disso, a recombinação Shockley-Read-Hall, bem como modelos de mobilidade dependente de dopagem e campo elétrico também são aplicados. Todos os parâmetros do modelo são consistentes com aqueles em [19, 20]. Como o tempo de vida da portadora governa a geração / recombinação da portadora durante a operação de manutenção, ela influencia o RT de DGTFTET DRAM. De acordo com os diferentes tempos de vida do portador, variando entre 1 μs e 10 ns em [26,27,28], os tempos de vida do elétron e do buraco são definidos para 100 ns. A relação de Scharfetter e os modelos de Schenk são usados para incluir dopagem e dependência da temperatura ao longo da vida, respectivamente.

Resultados e discussão

Mecanismo operacional

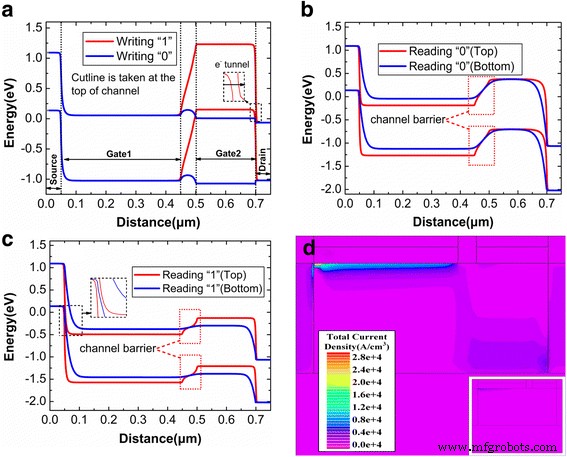

Em DGTFET DRAM, as operações de escrita e leitura são controladas por BTBT nas junções de tunelamento de dreno e fonte, respectivamente. A Figura 2 mostra as faixas de energia durante as diferentes operações. Conforme mostrado na Fig. 2a, durante a escrita “1”, o Gate2 com uma polarização negativa coloca significativamente a banda de energia do canal sob o Gate2, de forma que uma barreira de tunelamento extremamente pequena é criada no lado do dreno. Assim, o túnel de elétrons em direção ao lado do dreno e os orifícios são acumulados no poço de potencial profundo (1,2 V), conforme mostrado na Fig. 3a. Durante a escrita “0”, o Gate2 com viés positivo faz com que os furos se expulsem desse poço de potencial e se recombinem no lado do dreno [29]. A Figura 2b, c mostra as bandas de energia após a leitura “1” e “0”, respectivamente. A Figura 2b ilustra que há uma barreira de canal entre o Gate1 e o Gate2, mas ela não existe na parte inferior do canal. Além disso, a distância de tunelamento no lado da fonte é menor no topo do canal. Isso demonstra que um caminho de condução inclinado (da interface frontal para Gate1 para interface traseira para Gate2) é formado durante a leitura "1", o que também pode ser demonstrado pela densidade de corrente da Fig. 2d. Durante a leitura “0”, a barreira óbvia do canal pode ser encontrada na Fig. 2c, que restringe a leitura da corrente “0”. A inserção da Fig. 2d mostra que o tunelamento de elétrons da região de origem não pode cruzar essa barreira de canal para formar a corrente “0” de leitura mais alta.

Faixas de energia da fonte ao dreno. a Bandas de energia depois de escrever “1” com polarização Gate2 negativa e depois de escrever “0” com polarização Gate2 positiva. b Bandas de energia na parte superior e inferior do canal após a leitura “1”. c Bandas de energia na parte superior e inferior do canal após a leitura “0”. d Densidade de corrente total após ler “1”

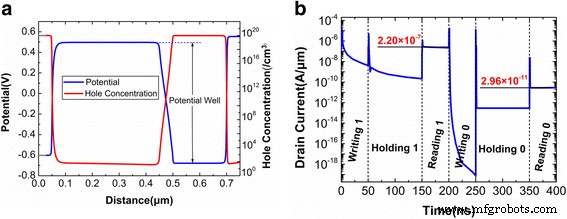

a Potencial e concentração do orifício na superfície do canal após escrever “1”. b Resposta transitória da corrente de drenagem para DGTFET DRAM operado na Tabela 1

Uma condição de programação adequada é importante para DGTFET DRAM. Uma polarização negativa maior deve ser aplicada no Gate2 para que o BTBT saturado seja induzido durante a gravação de “1”. Durante a retenção de “1”, uma pequena polarização negativa é aplicada no Gate2 para reter orifícios no poço de potencial por um longo tempo. Para operações de leitura, a polarização mais alta do Gate1 fortalece o BTBT durante a leitura “1”, mas que é prejudicial para a leitura da corrente “0”. O Gate2 com a polarização apropriada não só pode melhorar a leitura da corrente “1”, mas também pode enfraquecer a leitura da corrente “0”. Aplicando a condição de programação otimizada na Tabela 1, a resposta transitória de DGTFET DRAM com os parâmetros padrão é mostrada na Fig. 3b. Os tempos de gravação e leitura, bem como de espera, são definidos em 50 ns e 100 ns, respectivamente. A proporção atual obtida de leitura “1” para leitura “0” é de cerca de 10 4 , que é o mesmo que em [17, 19, 20].

Impacto dos dielétricos do espaçador

Em DGTFET DRAM, o uso de dielétricos de baixo k ou alto k em três espaçadores (S_Spacer, G_Spacer e D_Spacer) influenciará seu desempenho. Neste projeto, os dielétricos de baixo k e alto k escolhem o SiO 2 e HfO 2 , respectivamente. Se cada espaçador usa SiO 2 ou HfO 2 , haverá oito combinações de engenharia de espaçadores. Para uma análise mais abrangente, as propriedades de desempenho do DGTFET DRAM com cada combinação, incluindo a leitura “1” ( I 1 ) e “0” ( I 0 ) correntes, bem como relação de corrente ( I 1 / eu 0 ), são extraídos das respostas transitórias, conforme mostrado na Tabela 2. Para avaliar o TR, esses parâmetros também são extraídos quando o tempo de espera é aumentado para 2 s, o que será discutido nas seções seguintes. Na Tabela 2, as letras “S” e “H” representam SiO 2 e HfO 2 , respectivamente, e três letras de cada abreviatura representam respectivamente S_Spacer, G_Spacer e D_Spacer.

Na Tabela 2, a engenharia de espaçador ideal pode ser selecionada. O eu 1 são cerca de 10 −7 A / μm e 10 −9 A / μm quando o SiO 2 e HfO 2 são usados no S_Spacer, respectivamente. Quando o D_Spacer aplica o HfO 2 , o eu 0 é baixo para cerca de 10 −14 A / μm. Portanto, a configuração ideal do espaçador do DGTFET DRAM é que dielétricos de baixo k e alto k devem ser usados nos lados da fonte e do dreno. As razões específicas serão analisadas sistematicamente nas seções seguintes.

Impactos do dielétrico S_Spacer

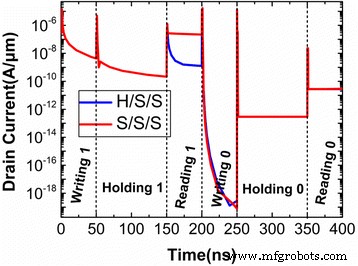

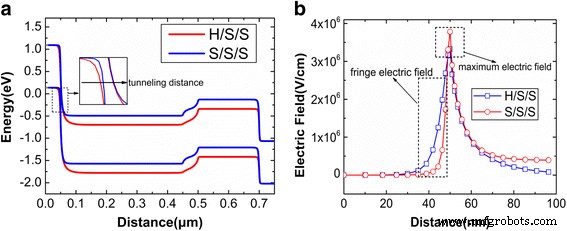

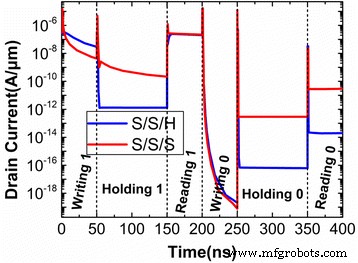

Para analisar as influências do S_Spacer, as respostas transitórias das correntes de drenagem para H / S / S e S / S / S são comparadas na Fig. 4. Pode-se observar que a leitura da corrente “1” é melhorada em cerca de dois ordens de magnitude quando o SiO 2 é escolhido como o dielétrico S_Spacer.

Respostas transitórias de correntes de drenagem para H / S / S e S / S / S operadas na Tabela 1

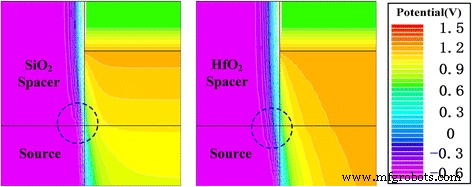

A Figura 5 mostra os contornos potenciais de S / S / S e H / S / S. Na junção de tunelamento da fonte, a região de depleção da superfície de H / S / S é estendida obviamente em comparação com a de S / S / S, como mostrado no círculo na Fig. 5. A região de depleção da superfície estendida aumenta a largura da barreira de tunelamento. A Figura 6a mostra as faixas de energia após a leitura “1”. Conforme mostrado na região local aumentada desta figura, a distância de tunelamento (veja as setas) de H / S / S é obviamente maior do que a de S / S / S, que é causada pela região de depleção da superfície estendida. Além disso, após a leitura “1”, o campo elétrico no topo da junção de tunelamento de fonte é mostrado na Fig. 6b. Pode-se constatar que o campo elétrico da franja de H / S / S é maior do que o de S / S / S, o que é o principal motivo para a extensão da região de depleção da superfície. Em uma palavra, S_Spacer com high-k (HfO 2 ) dielétrico gera o campo elétrico de franja maior de modo que a região de depleção da superfície na junção de tunelamento da fonte seja estendida, o que aumenta a distância de tunelamento de elétrons e diminui a corrente de leitura "1". Além disso, também pode ser verificado na Fig. 6b que o campo elétrico máximo de S / S / S é maior do que o de H / S / S. A relação exponencial entre a taxa de BTBT e o campo elétrico torna a corrente de tunelamento de S / S / S muito maior do que a de H / S / S [30]. Portanto, o S_Spacer com o dielétrico baixo-k (SiO 2 ) é benéfico para a corrente de leitura “1”.

Contornos potenciais de S / S / S (esquerda) e H / S / S (direita) depois de ler "1"

a Faixa de energia da fonte à drenagem e b campo elétrico no topo da junção de tunelamento de fonte

Na Fig. 6a, o dielétrico S_Spacer também traz o impacto na banda de energia da região do canal. Na Fig. 6b, o campo elétrico de S / S / S é maior na região do canal, então seu potencial de canal é menor do que o de H / S / S. Como resultado, o nível de energia mais alto pode ser encontrado em S / S / S. Mas isso não pode trazer efeitos na barreira de tunelamento e leitura de corrente “1”.

Impactos do Dielétrico D_Spacer

Posteriormente, o D_Spacer também é investigado neste artigo. Mantendo o S_Spacer e G_Spacer constantes (SiO 2 é usado nesses dois espaçadores), as diferentes correntes de drenagem transiente causadas pelos diferentes dielétricos D_Spacer são ilustradas na Fig. 7. Além da leitura “1” e escrita “0”, as outras operações têm dependência óbvia do dielétrico D_Spacer. Isso ocorre porque esse D_Spacer está longe do caminho de condução de leitura “1” (parte inferior do canal sob o Gate2). Pode-se aprender com o mecanismo de operação anterior que as operações de gravação e retenção são governadas pelo Gate2, de modo que o dielétrico D_Spacer pode ter influências nessas duas operações.

Respostas transitórias de correntes de drenagem para S / S / H e S / S / S operadas na Tabela 1

Durante a operação de retenção, os orifícios acumulados durante a gravação “1” são removidos do poço de potencial e recombinados no lado do dreno. Portanto, a corrente de retenção “1” vem principalmente da corrente de recombinação SRH. Devido à maior controlabilidade do Gate2 sobre o canal em S / S / S, S / S / S tem a maior taxa de recombinação e mantém a corrente “1”. Mas é muito menor do que a corrente BTBT durante a leitura “1”, portanto, a corrente de retenção mais alta “1” não pode ser refletida na leitura da corrente “1”.

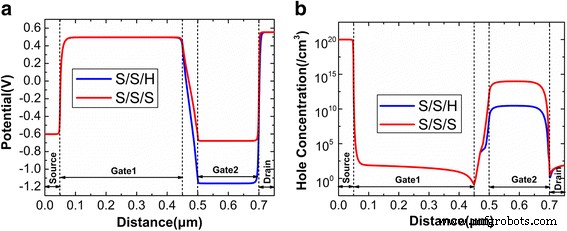

Durante a gravação “1”, o dielétrico D_Spacer influencia significativamente a profundidade potencial do poço. O contorno potencial na Fig. 8a mostra que D_Spacer com HfO 2 dielétrico cria um poço de potencial mais profundo. Isso implica que o BTBT efetivo entre o dreno e o canal é estendido para a região mais profunda do canal. Portanto, a corrente de escrita “1” de S / S / H é maior que a de S / S / S. Mantendo “0”, embora uma pequena polarização negativa (- 0,2 V) seja aplicada no Gate2, ele também pode colocar a banda de energia do canal sob o Gate2, o que induz o BTBT no lado do dreno. Através da análise anterior, pode ser aprendido que D_Spacer com SiO 2 dielétrico aumenta o BTBT na junção de tunelamento de dreno durante a manutenção “0”, o que pode ser demonstrado pela concentração de furo mais alta para S / S / S, como mostrado na Fig. 8b. Portanto, o D_Spacer com SiO 2 o dielétrico resulta na corrente de retenção “0” mais alta.

a Contorno potencial após escrever “1”. b Concentração do furo após manter “0”

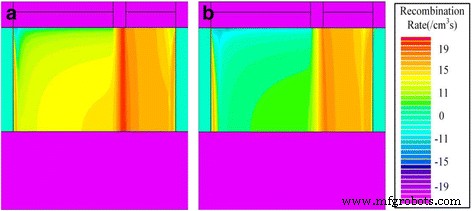

Durante a leitura "0", porque a barreira do canal entre o Gate1 e o Gate2 impede que os elétrons fluam em direção ao lado do dreno, a diferença da leitura da corrente "0" para S / S / H e S / S / S é causada principalmente pela corrente de recombinação . Quanto mais buracos são acumulados durante a retenção "0" para S / S / S, a banda de energia de queda torna a taxa de recombinação de S / S / S maior do que a de S / H / S durante a leitura "0", como mostrado na Fig. 9. Como resultado, quando o D_Spacer usando SiO 2 , a leitura de corrente “0” mais alta deve ser atribuída à corrente de recombinação mais alta, que é causada por mais furos acumulados durante a manutenção de “0”.

Taxa de recombinação de a S / S / S e b S / S / H depois de ler “0”

Em resumo, a engenharia de espaçador ideal para DGTFET DRAM é que os espaçadores nos lados da fonte e do dreno devem aplicar os dielétricos de baixo k e alto k, respectivamente. Pode ser visto na Tabela 2 que G_Spacer não tem influência no DGTFET DRAM quando os outros espaçadores permanecem inalterados. Isso ocorre porque os BTBTs que dominam as operações de escrita e leitura estão livres da influência do G_Spacer.

Tempo de retenção

Conforme explicado anteriormente, a recombinação e geração de orifícios durante a manutenção de “1” e “0” degradam o estado “1” e “0”, respectivamente. Como resultado, é necessário estudar a degradação do desempenho de DGTFET DRAM no tempo de espera mais longo. Na Tabela 2, o I 1 e eu 0 degradam muito com o aumento do tempo de espera. Em todos os dispositivos, eu 1 / eu 0 ainda é maior que 10 4 para dispositivos com engenharia de espaçador ideal (S / S / H e S / H / H) quando o tempo de espera aumenta para 2 s.

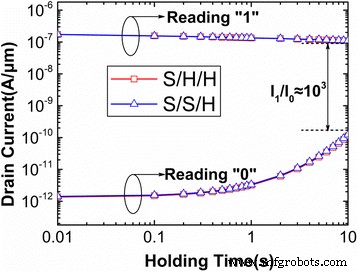

Geralmente, o tempo de espera necessário para reduzir a margem de detecção máxima (diferença entre I 1 e eu 0 ) em 50% é avaliado como RT. Neste projeto, um RT mais estrito é definido como o tempo máximo de retenção quando o I 1 / eu 0 é maior que 10 3 . A Figura 10 mostra a variação da corrente de leitura com o tempo de espera para S / S / H e S / H / H. Pode-se descobrir que a proporção atual de S / H / S e S / H / H é tão alta quanto 10 3 quando o tempo de espera sobe para 10 s. Como resultado, o RT de DGTFET DRAM com a engenharia de espaçador ideal pode chegar a 10 s. Isso é muito mais alto do que o valor alvo de 64 ms. A Tabela 3 compara as propriedades de desempenho neste trabalho com aquelas em [17,18,19,20]. Em [19, 20], a proporção atual é de apenas 10 2 , e o RT é muito menor que 10 s. Além disso, a leitura da corrente “0” neste trabalho é duas ordens de magnitude menor do que em [19, 20]. Os resultados do experimento sobre FD-SOI TFET DRAM também mostram que suas leituras de corrente “0” e RT são inferiores às deste trabalho. Este desempenho superior mostra que DGTFET é um substituto para DRAM de baixa potência. A otimização da engenharia dos espaçadores faz com que o DGTFET DRAM obtenha baixa leitura de corrente “0” e alto RT, o que auxilia na redução do consumo de energia estática e dinâmica.

Variação da corrente de leitura com o tempo de espera para S / S / H e S / H / H

Escalabilidade de DRAM DGTFET

Embora o DGTFET DRAM resolva o problema de densidade das células de memória devido à eliminação do capacitor com o tamanho grande, é necessário estudar sua escalabilidade. O objetivo da escalabilidade é manter o RT maior que 2 s. A Tabela 4 extrai as propriedades de desempenho de S / S / H com a diminuição de L g1 , L g2 e L lacuna . Na Tabela 4, os três números de cada abreviatura representam L g1 , L lacuna e L g2 .

Da Tabela 4, pode-se observar que eu 1 diminui extremamente quando o L g1 reduz para 100 nm de 200 nm. A escala de L g1 além de 100 nm estreita a barreira induzida do tipo n, resultando em controlabilidade de porta reduzida e degradado I 1 . O eu 0 aumenta significativamente com a diminuição de L g1 e L g2 . A redução de L g2 diminui a largura da barreira do canal entre o Gate1 e o Gate2, o que faz com que uma parte dos elétrons atravesse a barreira para formar o I superior 0 . Além disso, a redução contínua de L g1 enfraquece a capacidade do Gate1 de restringir os elétrons de tunelamento na superfície do canal durante a leitura de “0”. Na Tabela 4, o L lacuna não tem influência óbvia sobre o eu 1 , mas o eu 0 aumenta ligeiramente com a diminuição do L lacuna . Reduzindo L lacuna abaixo de 20 nm permite um tunelamento maior em direção à Gate2, degradando o estado “0” e reduzindo o tempo de retenção.

A fim de garantir que o eu 1 / eu 0 e o tempo de retenção é maior que 10 2 e 2 s, respectivamente, o mínimo L g1 , L g2 e L lacuna são considerados como 200, 150 e 20 nm, respectivamente. Este tamanho mínimo do dispositivo é ligeiramente menor do que em [17,18,19,20], conforme mostrado na Tabela 3. No entanto, o tamanho mínimo de DGTFET DRAM é ainda maior do que 20 nm / 18 nm nó 1T1C DRAM [31 ], que é a deficiência inerente ao DGTFET DRAM. Mas suas vantagens de sem capacitor, baixa potência e alto RT não podem ser ignoradas com a ajuda da otimização da engenharia do espaçador. Reduzir o tamanho do DRAM DGTFET além de 100 nm será o foco do nosso trabalho no futuro.

Conclusões

Neste artigo, a otimização da engenharia de espaçadores para DGTFET DRAM é estudada pela ferramenta Silvaco-Atlas. Os espaçadores nas laterais da fonte e do dreno têm as principais influências no desempenho do DRAM DGTFET. O campo elétrico de franja ampliado pelo espaçador de fonte com HfO 2 faz com que a região de depleção da superfície se estenda na junção de tunelamento da fonte, o que diminui a leitura da corrente “1”. Quando o SiO 2 dielétrico é usado no espaçador de dreno, o BTBT mais forte induz mais furos durante a retenção de “0”, o que aumenta a corrente de recombinação durante a leitura de “0”. Portanto, a engenharia de espaçador ideal é que dielétricos de baixo k e alto k devem ser usados em espaçadores de dreno e fonte, respectivamente. Através da otimização da engenharia do espaçador, o DGTFET DRAM obtém vantagens importantes - corrente de leitura “0” extremamente baixa e tempo de retenção mais alto (10s) em comparação com outros trabalhos relacionados. Além disso, a análise sobre escalabilidade revela que o tamanho mínimo do dispositivo ainda é maior do que na DRAM 1T1C de nó de 20 nm / 18 nm mais recente. Esta deficiência inerente indica que a redução do tamanho do DGTFET DRAM além de 100 nm será o foco de nosso trabalho para DGTFET DRAM no futuro.

Abreviações

- DGTFET:

-

Transistor de efeito de campo de túnel de porta dupla

- DRAM:

-

Memória de acesso aleatório dinâmico

Nanomateriais

- O Transistor de Unijunção (UJT)

- Idéias de projetos baseados em sensores para alunos do último ano de engenharia

- Princípios de Engenharia de Confiabilidade para o Engenheiro de Fábrica

- Cientistas da IBM inventam um termômetro para nanoescala

- O valor da divisão baseada na nuvem e do gerenciamento de arquivos para impressão 3D

- Otimização de Filme Fino Altamente Refletivo para Micro-LEDs de Ângulo Total

- O Melhor Nível de Otimização e Organização na Fábrica Inteligente

- Como encontrar as soluções de engenharia personalizadas que você procura

- A falta de diversidade pode ser a culpada pela crescente lacuna de habilidades do setor

- Obrigado pelas lembranças!