Supressão de crescimento excessivo de filamento na memória de acesso aleatório da ponte condutiva por Ta2O5 / TaOx Estrutura de duas camadas

Resumo

A estrutura de duas camadas foi amplamente adotada para melhorar a confiabilidade da memória de acesso aleatório de ponte condutiva (CBRAM). Neste trabalho, propomos uma solução conveniente e econômica para alcançar um Ta 2 O 5 / TaO x estrutura de duas camadas usando um processo de recozimento de baixa temperatura. A adição de um TaO x camada atuou como uma resistência externa suprimindo a corrente de transbordo durante a programação definida, conseguindo assim a comutação de auto-conformidade. Como resultado, as distribuições de estados de alta resistência e estados de baixa resistência são melhoradas devido à supressão do fenômeno de sobredefinição. Além disso, a retenção LRS do CBRAM é obviamente aprimorada devido à recuperação de defeitos no filme de comutação. Este trabalho fornece um método simples e econômico para melhorar a confiabilidade do CBRAM.

Introdução

A memória de comutação resistiva de ponte condutiva (CBRAM) é uma tecnologia inovadora e é considerada como memória não volátil de próxima geração (NVM) devido à sua alta escalabilidade, estrutura simples, facilidade de integração 3D e operação de alta velocidade [1,2, 3]. Para aplicação prática, as questões de confiabilidade, incluindo a retenção de dados e durabilidade, dificultam a introdução definitiva desses dispositivos de memória no mercado de memória. A engenharia de estrutura é a abordagem mais popular para melhorar a confiabilidade do CBRAM [4,5,6,7]. Zhao et al. injeção de cátions confinados para melhorar o desempenho do CBRAM por camada de grafeno nano-poro [8]. Embora a confiabilidade do dispositivo tenha melhorado muito, ele dificulta os custos no controle de material e não pode ser usado em um processo CMOS padrão. Para resolver esse problema, Gong et al. propôs um método compatível com CMOS e auto-alinhado para formar uma camada interfacial CuSiN em eletrodo de Cu para melhorar a retenção do estado de baixa resistência (LRS) [9]. Cao et al. propôs uma camada de barreira TiN para melhorar a confiabilidade do dispositivo em dispositivos CBRAM, eliminando o fenômeno de supercrescimento de nano-filamento e comportamento de SET negativo [10]. Os métodos acima utilizaram a estrutura de duas camadas para otimizar a confiabilidade do CBRAM de forma eficaz. No entanto, eles geram custos de fluxo de processo complexo ou velocidade de programação.

Neste trabalho, propomos um método compatível com CMOS para formar um dispositivo de duas camadas por um processo simples de recozimento em baixa temperatura. O dispositivo de camada dupla de Ta 2 O 5 / TaO x estrutura foi formada espontaneamente, o que apresenta melhores características de confiabilidade em comparação com o dispositivo não recozido. A confiabilidade aprimorada do dispositivo recozido pode ser explicada pelos filamentos concentrados formados ao longo do limite do grão durante a programação. Além disso, para um dispositivo de recozimento de duas camadas, devido à existência de TaO x , o comportamento de auto-conformidade é alcançado porque o TaO x camada serve como um resistor em série com um Ta 2 O 5 -camada resistente. Este resultado fornece um método simples compatível com CMOS para formar um dispositivo de camada dupla e melhorar a confiabilidade do CBRAM.

Métodos

O plug W com um diâmetro de 1 μm após CMP é servido como o eletrodo inferior (BE). Depois de depositar a camada de Ta 5 nm por pulverização catódica DC, o Ta 2 O 5 foi formado através de um processo de oxidação térmica, abaixo de 350 ° C, em plasma O 2 por 300 s por deposição química de vapor aprimorada por plasma (PECVD). Então, 40 nm Cu top eletrodo (TE) é sputtered e padronizado por litografia. As células de memória são padronizadas através do processo de corrosão com uma mistura de gás de SF 6 e C 3 F 8 usando o TE como máscara rígida. Posteriormente, o BE é extraído pelo Al pad. Finalmente, o dispositivo é completado com um processo de recozimento de baixa temperatura compatível com CMOS abaixo de 400 ° C por 30 min. O tamanho do dispositivo é definido pela área do eletrodo inferior, que é 1 μm 2 . Como referência, o dispositivo sem o processo de recozimento também é preparado. As medições elétricas DC são realizadas usando um analisador de parâmetros de semicondutor Keithley 4200-SCS. Para todas as medições, a tensão é aplicada ao Cu TE com o W BE aterrado.

Resultados e discussão

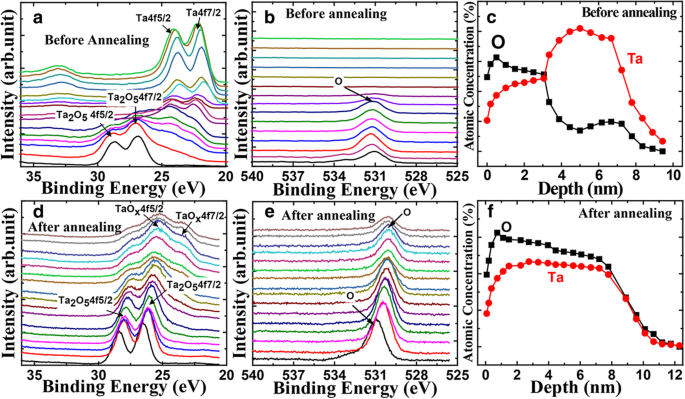

Para uma visão profunda do processo de recozimento, a composição e o estado de ligação química no Ta 2 O 5 filmes antes e depois do processo de recozimento são analisados por espectroscopia de fotoelétrons de raios-X (XPS). A taxa de corrosão da amostra é de 0,5 nm / ponto. Na Fig. 1a, os picos de Ta 2 O 5 4f dupleto com energias de ligação de pico de 26,70 eV (Ta 2 O 5 4f 7/2 ) e 28,60 eV (Ta 2 O 5 4f 5/2 ) com separação de pico de 1,9 eV são observados na superfície [11,12,13]. Este caso demonstra a existência de Ta 2 O 5 camada.

O XPS mostra o perfil de profundidade de Ta antes ( a ) e depois ( d ) anelamento. b , e Perfil de profundidade de O antes e depois do recozimento, respectivamente. c, f Perfil de concentração atômica de O e Ta com profundidade antes e depois do recozimento, respectivamente

Com o aumento da profundidade, os picos de Ta 2 O 5 4f o dupleto desaparece e os picos em 22,33 eV, 23,96 eV correspondendo a Ta 4f 7/2 , Ta 4f 5/2 aparecer. A Figura 1b verifica se não há sinal O na mesma profundidade onde o Ta 4f 7/2 e Ta 4f 5/2 existir. Em outras palavras, existe Ta metálico na superfície de Ta 2 O 5 para o dispositivo não recozido. As profundezas do Ta 2 O 5 e Ta analisado da Fig. 1c são 4 nm e 2,5 nm, respectivamente. Além disso, há o pico da concentração atômica de O na profundidade de 7 nm, indicando a existência do oxigênio absorvido. As Figuras 1d ee mostram os perfis de profundidade dos espectros XPS do Ta 2 O 5 filmes após o processo de recozimento. Os picos de Ta 4f doublet e Ta 2 O 5 4f dupleto existem juntos em uma certa profundidade. A intensidade do Ta 5+ o estado de oxidação enfraquece gradualmente com o aumento da profundidade. Combinado com o sinal de oxigênio geral ao longo da profundidade do filme, confirmamos que o TaO x existe na superfície de Ta 2 O 5 [11, 14]. Calculado a partir da Fig. 1f, a espessura do Ta 2 O 5 é 4 nm e TaO x é 3,5 nm. Portanto, o TaO x é formado pela mudança do oxigênio adsorvido em oxigênio da rede no processo de recozimento. A redistribuição de oxigênio alcançaria um ponto de saturação saturado após o processo de recozimento. A espessura do TaOx, bem como a tensão de formação não aumentará mesmo que o tempo de recozimento aumente, comprovando a grande margem de processo deste processo de recozimento.

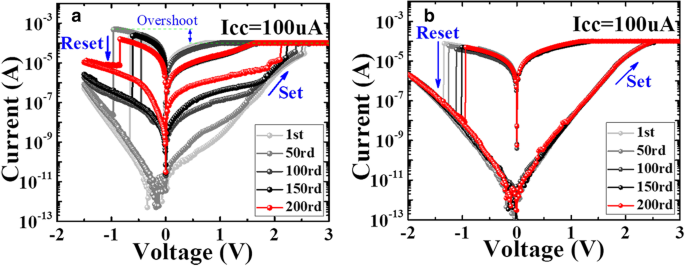

As Figuras 2a eb são as características de comutação resistiva de Cu / Ta 2 O 5 / W antes e depois do recozimento no modo de varredura DC. As resistências iniciais ( R inicial ) dos dois dispositivos estão em estado de alta resistência (HRS) com valores de ~ 10 9 Ω e 10 10 Ω, respectivamente. Quanto maior o R inicial do dispositivo recozido é devido ao filme de óxido mais espesso formado sob o processo térmico. Notavelmente, este dispositivo não precisa de um processo de formação, o que é bastante esperado na aplicação prática. Para o dispositivo não recozido, ele muda para LRS abruptamente quando a tensão aplicada atinge um valor crítico durante a varredura de tensão positiva. Algum LRS ultrabaixo ocorreu durante o processo de ajuste. A corrente de RESET, neste caso, é muito maior do que a corrente de conformidade predefinida, indicando o fenômeno de ultrapassagem ocorrido neste dispositivo. A Figura 3b exibe o LRS e HRS instáveis dentro de 200 ciclos para o dispositivo não recozido. A grande variação entre ciclo a ciclo leva à janela de memória reduzida para tão pequena quanto 20. A Figura 2b mostra o comportamento de comutação dos dispositivos recozidos. A corrente que flui pela célula aumenta gradativamente e atinge a corrente de conformidade. Nenhum ponto de comutação óbvio é observado, evitando o fenômeno de overshoot ocorrido nos dispositivos não recozidos. Uma janela de memória de até 10 4 foi alcançado durante os ciclos de comutação, devido à distribuição uniforme de HRS e LRS.

Curvas I-V típicas de dispositivos Cu / TaOx / W antes do recozimento ( a ) e após o recozimento ( b ) com 200 ciclos

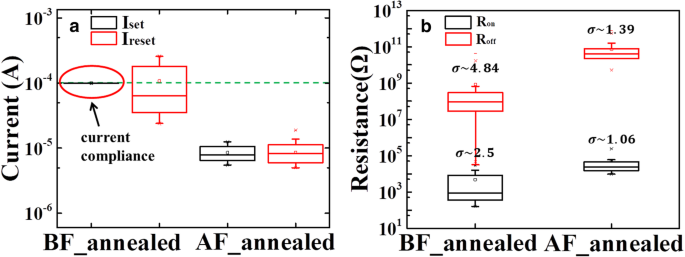

a Defina e RESET as distribuições de corrente antes e depois do recozimento, respectivamente. b A distribuição da resistência de HRS e LRS antes / depois do recozimento

A supressão do fenômeno de overet no dispositivo recozido também pode ser verificada pela melhor distribuição da corrente de RESET ( I REINICIAR ) e definir a corrente ( I Conjunto ) no dispositivo recozido, como mostrado na Fig. 3a. O eu Conjunto do dispositivo não recozido está preso no I CC mas eu REINICIAR distribui amplamente. Em contraste, para o dispositivo recozido, o I REINICIAR é semelhante a I Conjunto . A uniformidade dispositivo a dispositivo é avaliada analisando o R em e R desligado em 20 dispositivos diferentes no modo DC. Conforme mostrado na Fig. 3 (b), o R em extraído em V ler de 0,1 V para o dispositivo não recozido distribui de 10 2 Ω a 10 5 Ω, enquanto o R em do dispositivo recozido distribui de 10 4 Ω a 10 5 Ω. O relativamente mais alto R em do dispositivo recozido resultou da resistência em série do TaO x camada. Além disso, a distribuição de HRS do dispositivo recozido também é muito melhorada. Conforme mostrado na Fig. 3b, o desvio padrão (SD) de R desligado é reduzido de 4,84 para 1,39.

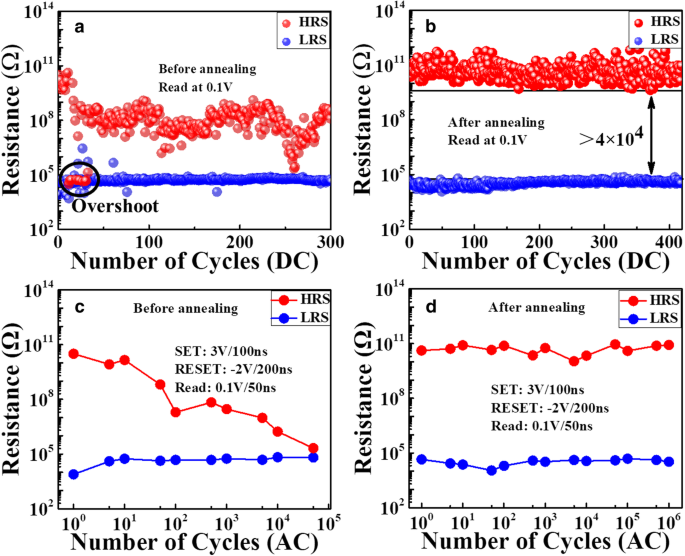

Os resultados do ciclo em varredura DC são mostrados nas Fig. 4a e b. Para o dispositivo não recozido, a proporção HRS / LRS é de cerca de 10 5 no início, depois diminui gradualmente e, por fim, mantém-se no LRS. Observe que alguns erros de software podem ser observados durante o ciclo, na forma de HRS (pontos vermelhos) e LRS (pontos azuis) executados para frente e para trás ocasionalmente. Para o dispositivo recozido, a relação HRS / LRS permanece estável (~ 10 4 ) sem qualquer degradação. Durante as medições de pulso, as condições de programação de pulso adequadas são otimizadas como 3 V / 100 ns para operação de configuração, - 2 V / 200 ns para operação de RESET e 0,1 V / 50 ns para operação de leitura. O tempo de detecção para a operação Set / RESET / Read é de 15 ns / 12 ns / 25 ns, respectivamente. Como pode ser visto na Fig. 4c, a resistência para o dispositivo não recozido é geralmente inferior a 5 × 10 4 ciclos de comutação. No entanto, a partir da Fig. 4d, é surpreendente que o dispositivo recozido ainda funcione bem sem falha após mais de 10 6 ciclos de comutação. Com base em nosso estudo anterior [15], a falha de resistência no CBRAM está relacionada à operação de RESET instável resultante do crescimento excessivo do filamento no contra-eletrodo. Por outro lado, o filamento crescido precisa de mais energia para se romper e tende a causar RESET incompleto e menor HRS. Por outro lado, o crescimento excessivo do filamento no contra-eletrodo leva a íons de Cu residuais no contra-eletrodo, que podem servir como um reservatório de íons metálicos e tornar inesperado-SET negativo. Para o dispositivo recozido, o crescimento excessivo do filamento é bem suprimido pela incorporação de TaO x camada e resulta em uma operação de RESET mais estável. Como resultado, a janela de memória é bem mantida e a característica de ciclagem é muito melhorada.

Os resultados do ciclismo de a os dispositivos sem recozimento sob 300 ciclos DC e b os dispositivos com recozimento abaixo de 400 ciclos DC. c, d Características de resistência em modo CA com a configuração de operação otimizada:definir 3 V / 100 ns; RESET - 2 V / 200 ns. Até 10 6 ciclos foram obtidos para o dispositivo após o recozimento

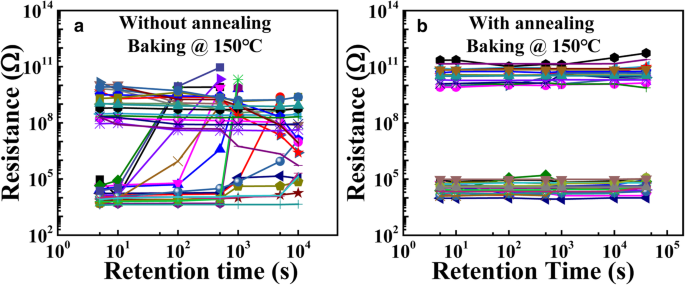

Considerar a característica de retenção desempenha um papel crucial para a aplicação prática do CBRAM [16]. As características de retenção são medidas abaixo de 150 ° C usando o forno a vácuo. A resistência de cada célula é verificada após o resfriamento à temperatura ambiente em cada intervalo de década. As Figuras 5a eb mostram a dependência do R HRS / R LRS no tempo de cozimento para o dispositivo sem recozimento e com recozimento, respectivamente. Para os dispositivos não recozidos (Fig. 5a), conforme o tempo aumenta, os dispositivos falharam gradualmente dentro de 10 4 s. No entanto, para o dispositivo recozido (Fig. 5b), entre os 20 dispositivos registrados, as resistências do LRS e HRS não mostram qualquer degradação à medida que o tempo de cozimento aumenta. Ou seja, a retenção dos dispositivos é altamente melhorada pelo processo de recozimento. O tempo de vida do dispositivo recozido a 85 ° C pode ser extraído como 10 anos pelo gráfico de Arrhenius, o que está de acordo com os CBRAMs relatados [17, 18]. A obtenção de uma melhor característica de retenção para o dispositivo recozido deve-se ao fato de o processo de recozimento recuperar alguns defeitos no filme de troca, o que retardaria a difusão das espécies de Cu.

Características de retenção do HRS / LRS para a dispositivo não recozido e b dispositivo recozido a 150 ° C

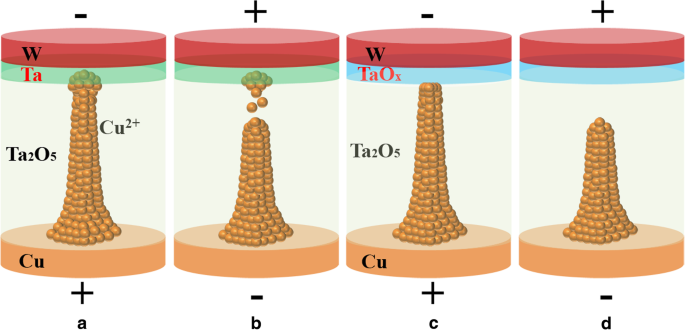

Com base nos resultados acima, um modelo físico para o comportamento de comutação dos dispositivos recozidos e não recozidos é ilustrado na Fig. 6a-d. O crescimento do filamento em CBRAM está associado ao transporte de íons Cu na rede de eletrólito [19]. O fenômeno de overshoot que aconteceu no dispositivo não recozido faz o filamento crescer demais no contra-eletrodo. Durante a operação de RESET, os íons de Cu residuais armazenados no contraeletrodo irão para a lacuna do túnel entre a ponta do filamento e o contraeletrodo, resultando no Cu + residual no final da operação RESET e variação séria de HRS. Como o coeficiente de difusão de Cu em TaO x (4,9 × 10 - 20 cm 2 / s) é muito menor do que em Ta (1,0 × 10 - 6 cm 2 / s), o Cu se difunde em TaO x é muito mais difícil sob o campo elétrico durante a operação Set na amostra de Cu / Ta 2 O 5 / TaO x / W [20, 21]. Conseqüentemente, o comportamento sobredefinido e o crescimento excessivo do filamento podem ser bem suprimidos e a operação RESET torna-se mais estável.

A modelagem física para o comportamento de comutação dos dispositivos recozidos e não recozidos. O a Definir e b Processo de RESET para o dispositivo não recozido com a estrutura de Cu / Ta 2 O 5 / Ta / W. c Definir e d Processo de RESET para o dispositivo recozido com a estrutura de Cu / Ta 2 O 5 / TaO x /C. O crescimento excessivo do filamento é suprimido pelo TaO x camada formada durante o processo de recozimento

Conclusões

Nesta carta, investigamos as características de comutação de um TaO x dispositivo CBRAM baseado em A Ta 2 O 5 / TaO x A pilha de duas camadas foi formada após um tratamento pós-recozimento térmico. O TaO x camada pode atuar como uma resistência externa suprimindo a corrente de transbordamento durante a operação definida. Ambas as distribuições HRS e LRS são bastante melhoradas devido à supressão do fenômeno de sobredefinição. Além disso, a retenção de dados do CBRAM é aprimorada devido à recuperação de defeitos no filme de comutação durante o recozimento térmico. Este trabalho fornece a solução mais conveniente e econômica para obter a estrutura de duas camadas e melhorar a confiabilidade do CBRAM.

Abreviações

- CBRAM:

-

Memória de acesso aleatório de ponte condutiva

- HRS:

-

Estados de alta resistência

- LRS:

-

Estados de baixa resistência

- NVM:

-

Memória não volátil

- PECVD:

-

Deposição de vapor químico intensificada por plasma

- TE:

-

Eletrodo superior

Nanomateriais

- Estreia FPGA de defesa com acesso antecipado

- Nano grafema, memória transparente flexível à base de silício

- Revelando a estrutura atômica e eletrônica das nanofibras de carbono de copo empilhado

- Estrutura e propriedades eletrônicas da nanoargila caulinita dopada com metal de transição

- Preparação e desempenho fotocatalítico de fotocatalisadores de estrutura oca LiNb3O8

- Um estudo coletivo sobre modelagem e simulação de memória de acesso aleatório resistiva

- Estrutura Eletrônica e Características I-V das Nanoribbons InSe

- Estrutura Eletrônica Dependente de Spin e Valley em Siliceno sob Potenciais Periódicos

- Um estudo da variabilidade na memória de acesso aleatório resistiva de contato por modelo de vacância estocástica

- Considerações sobre fornecimento de dispositivos de acesso remoto para segurança