Estudo comparativo de transistores de efeito de campo de capacitância negativa com diferentes capacitâncias MOS

Resumo

Demonstramos o efeito da capacitância negativa (NC) de HfZrO x com base em transistores de efeito de campo (FETs) nos experimentos. Melhorado I DS , SS e G m de NCFET foram alcançados em comparação com FET semicondutor de óxido de metal de controle (MOS). Neste experimento, os transistores MIS inferiores com diferentes tempos de passivação são equivalentes aos dispositivos NC com diferentes capacitâncias MOS. Enquanto isso, as propriedades elétricas do NCFET com passivação de 40 min são superiores às do NCFET com passivação de 60 min devido ao bom casamento entre C FE e C MOS . Embora SS de menos de 60 mV / década não seja alcançado, as características de transferência não histerética benéficas para as aplicações lógicas são obtidas.

Introdução

Com a redução do transistor, o nível de integração do circuito integrado (IC) está crescendo continuamente. Um problema de dissipação de energia que acompanha é urgente para ser resolvido. Para contornar este problema, a tensão de operação do transistor deve ser reduzida [1]. A oscilação subliminar (SS) do MOSFET não pode ser inferior a 60 mV / década à temperatura ambiente, o que restringe a redução da tensão limite V TH e tensão de alimentação V DD [2]. Muitos esforços têm sido dedicados à pesquisa e ao desenvolvimento de dispositivos com novos mecanismos de transporte e comutação para superar o limite de Boltzmann, incluindo transistor de efeito de campo de capacitância negativa (NCEFT) [3, 4], porta resistiva FET [5], nano- FET eletromecânico (NEMFET) [6, 7], semicondutor de óxido metálico de ionização por impacto (I-MOS) [8, 9] e FET de tunelamento [10, 11]. Entre eles, o NCFET tem despertado muita atenção porque pode atingir um SS acentuado sem perder a corrente de acionamento [12,13,14,15]. HfO dopado 2 (por exemplo, HfZrO x (HZO) e HfSiO x ) tem sido amplamente utilizado em NCFETs [4, 16, 17]; é compatível com o processo CMOS [18]. Um estudo teórico mostrou que a histerese indesejada ocorre devido à capacitância ferroelétrica não combinada C FE à capacitância MOS subjacente C MOS no NCFET [19]. No entanto, o efeito da correspondência entre C FE e C MOS sobre as características elétricas dos NCFETs ainda é uma preocupação nos experimentos.

Neste trabalho, as características elétricas de NC Ge FETs com diferentes capacitâncias MOS são estudadas com base no casamento diferente entre C FE e C MOS . Embora SS inferior a 60 mV / década não apareça, as características de transferência livre de histerese e melhores propriedades elétricas são obtidas. Picos aparentes de C FE versus V FE curvas demonstram o efeito NC de NCFETs baseados em HZO. A melhor correspondência de C FE e C MOS contribui para SS mais íngreme e mais alto na corrente, o que é benéfico para as aplicações lógicas.

Métodos

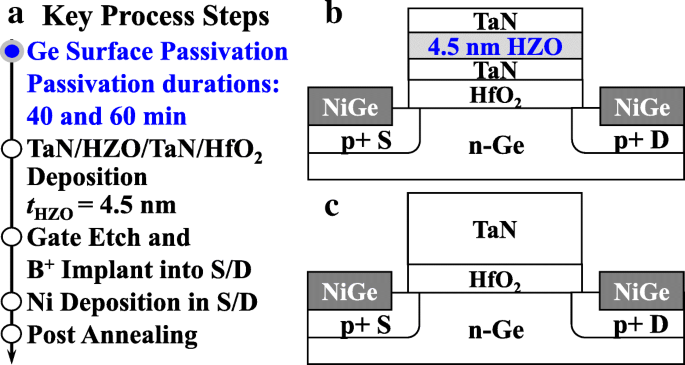

O principal processo de fabricação de Ge NCFETs é mostrado na Fig. 1a. Wafers n-Ge (001) de quatro polegadas com uma resistividade de 0,088–0,14 Ω · cm foram usados como substratos de partida. Após a limpeza do pré-portão, wafers de Ge foram carregados em uma câmara de ultra-alto vácuo para passivação de superfície usando Si 2 H 6 . Duas durações de passivação de 40 e 60 min foram usadas. Então, TaN / HZO / TaN / HfO 2 pilha foi depositada. A espessura do HfO 2 camada dielétrica e camada HZO FE são 4,35 e 4,5 nm, respectivamente. Após a padronização e ataque químico, as regiões de origem / drenagem (S / D) foram implantadas usando íons de boro (B + ) a uma energia de 30 keV e uma dose de 1 × 10 15 cm −2 . Metal S / D O níquel foi formado usando um processo de decolagem. Finalmente, o recozimento térmico rápido a 450 ° C por 30 s foi realizado. Controle MOSFET com TaN / HfO 2 pilha também foi fabricada. As Figuras 1b e c mostram os esquemas do NCFET fabricado e do MOSFET de controle, respectivamente. A porta de metal interna no NCFET fabricado contrabalança o potencial na superfície do canal, que é chamada de estrutura MFMIS.

a Principais etapas do processo de dispositivos NC fabricados. Os esquemas do b fabricado NCFET e c MOSFET de controle

Resultados e discussão

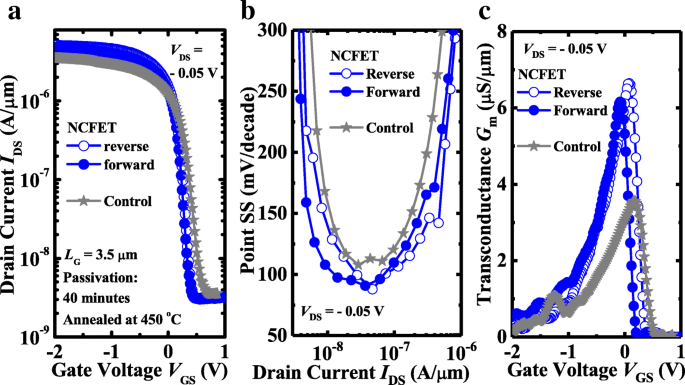

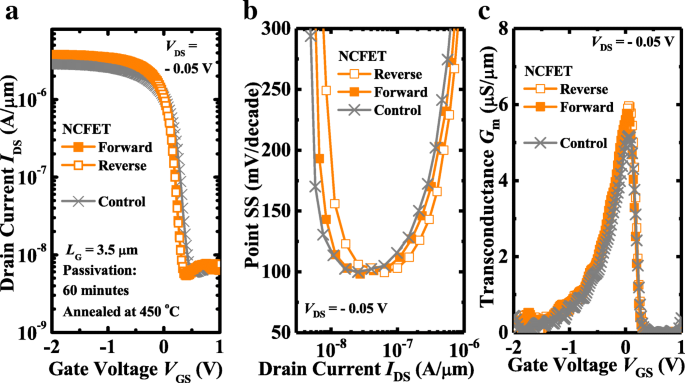

A Figura 2a representa o I medido DS - V GS curvas de um par de NCFET e MOSFET de controle com passivação de superfície de 40 min. Ambos os dispositivos têm um comprimento de porta L G de 3,5 μm. O dispositivo NC com passivação de 40 min tem um I significativamente melhorado DS do que o MOSFET de controle. As curvas de transferência do NCFET exibem uma característica não histérica. Ponto SS versus I DS curvas na Fig. 2b mostram que o transistor NC melhorou SS em relação ao dispositivo de controle, embora SS de sub-60 mV / década não apareça. A Figura 2c mostra que o transistor NC obtém uma transcondutância linear significativamente aumentada G m sobre o dispositivo de controle em V DS de - 0,05 V. A Figura 3 compara os desempenhos elétricos de NCFET e MOSFET de controle com passivação de superfície por 60 min. Da mesma forma, o eu DS , aponte SS e G m do NCFET são superiores aos do MOSFET de controle.

a O medido eu DS - V GS curvas do NCFET e controle MOSFET com passivação de 40 min. Comparação de b ponto SS versus I DS e c G m características entre NC FET e controle MOSFET

a O medido eu DS - V GS curvas do NCFET e controle MOSFET com passivação de 60 min. Comparação de b ponto SS versus I DS e c G m características entre NCFET e MOSFET de controle

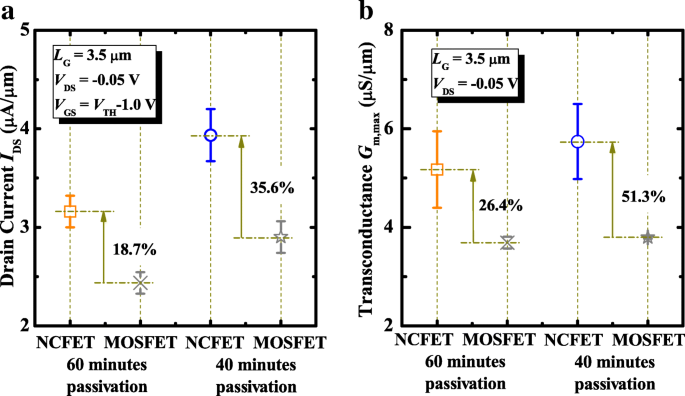

A Figura 4a mostra os resultados estatísticos da corrente de comando de NCFETs e MOSFETs de controle em V DS de - 0,05 V e V GS - V TH =- 1,0 V. NCFETs demonstram 18,7% e 35,6% de melhoria em I DS para passivação de superfície de 60 min e 40 min, respectivamente, em comparação com os dispositivos de controle. Especula-se que os NCFETs passivados por 40 min têm uma melhor correspondência entre C MOS e C FE sobre os dispositivos NC com 60 min. A Figura 4b mostra que os NCFETs obtêm 26,4% e 51,3% de melhoria na transcondutância máxima G m, máx para passivação de superfície de 60 min e 40 min, respectivamente, em comparação com os dispositivos de controle. Vê-se que os MOSFETs de controle com passivação de superfície por 40 min têm um I maior DS e G m, máx do que os dispositivos passivados por 60 min, que é devido ao maior C MOS induzida pela menor espessura de óxido equivalente ( E OT ) A porta de metal interna fornece um plano equipotencial; o dispositivo pode ser modelado de forma equivalente como um divisor de tensão capacitivo. A capacitância total C G é uma série de C FE e C MOS . A tensão da porta interna é amplificada devido ao efeito NC. O coeficiente de amplificação de tensão interna β =∣ C FE ∣ / ∣ C FE ∣ - C MOS obtém o máximo quando | C MOS | =| C FE | [20, 21]. Atingindo a correspondência otimizada de C FE e C MOS é o pré-requisito para o aprimoramento da corrente.

O a estatístico eu DS e b G m resultados de NCFETs e MOSFETs de controle com durações de passivação de 40 e 60 min

O extraído V int versus tensão da porta V GS curvas são mostradas na Fig. 5a. V int do transistor NC pode ser extraído com base na hipótese de que I DS - V int curva do transistor NC é exatamente idêntica a I DS - V GS curva do dispositivo de controle. O coeficiente de amplificação de tensão interna dV int / dV GS é mostrado na Fig. 5b. d V int / d V GS > 1 é alcançado na ampla faixa de varredura de V GS para o NCFET com passivação de superfície de 40 min, contribuindo para um SS mais íngreme do que o dispositivo de controle durante o processo de medição, o que se deve ao chaveamento da polarização local [22]. É consistente com os resultados mencionados na Fig. 2b. Para o NCFET com passivação de 60 min, o coeficiente de amplificação da tensão interna d V int / d V GS > 1 é alcançado durante o intervalo de V GS <0 V para a varredura dupla de V GS , que está de acordo com o SS elevado na Fig. 3b.

a Extraído V int em função de V GS curvas. b O coeficiente de amplificação de tensão interna versus V GS curvas

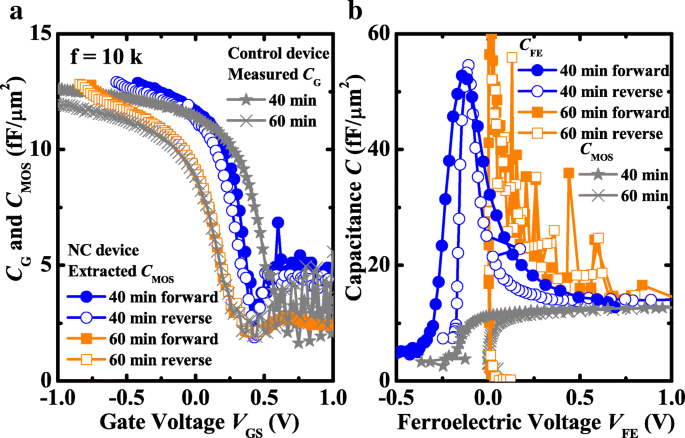

A Figura 6a mostra o C extraído MOS versus V GS curvas para o transistor NC, que depende do V int - V GS na Fig. 5a e o C G - V GS curvas de MOSFETs de controle. O C extraído MOS está de acordo com o medido C G. Assim, a validade do método de cálculo é demonstrada. O C FE e C MOS versus V FE as curvas são representadas na Fig. 6b. Desde o início do efeito NC, o valor absoluto de C negativo FE do transistor excede C MOS para varredura dupla de V GS o tempo todo na Fig. 6b. | C FE |> C MOS e C FE <0 pode causar características livres de histerese e a correspondência de C MOS e C FE é benéfico para as aplicações lógicas [23, 24]. Características livres de histerese nas Figs. 2a e 3a são observados atribuídos a todo o casamento de domínio e captura de carga inibida [25]. A comutação de polarização estável é responsável pelas características não histeréticas [26]. Além disso, o grande portão interno ganha d V int / d V G > 1 é atribuído à ligeira discrepância entre | C FE | e C MOS na região subliminar, resultando no SS íngreme do dispositivo NC. Enquanto isso, há uma correspondência melhor entre C FE e C MOS para o NCFET com passivação de 40 min do que para o NCFET com passivação de 60 min. Assim, isso fornece evidências diretas para indicar que o NCFET com passivação de 40 min possui um melhor desempenho elétrico do que o NCFET com passivação de 60 min. A polarização FE muda o V FE ; portanto, a carga de FE varia. A carga total se multiplica, o que é atribuído à polarização FE além do incremento de V GS . Em outras palavras, para o V fornecido GS , a carga no canal aumenta, então o I DS melhora. Como consequência, o SS acentuado de característica de transferência aparece nos experimentos.

a Medido C G e extraiu C MOS em função de V GS . b C FE e C MOS versus V FE curvas

Conclusões

As características de transferência sem histerese são obtidas para os NCFETs com passivação de 40 e 60 min. Os pFETs NC Ge com passivação de 40 min têm melhores características elétricas do que o dispositivo NC com passivação de 60 min em experimentos. Também demonstramos o efeito NC de NCFETs baseados em HZO. Para NCFETs, o SS e d V íngremes int / d V GS > 1 são obtidos. O NCFET com passivação de 40 min alcançou uma boa combinação entre C FE e C MOS , o que contribui para as características não histéricas. Os diferentes comportamentos do NC são considerados relacionados à troca de parede do domínio microscópico nos filmes finos de FE.

Disponibilidade de dados e materiais

Os conjuntos de dados que suportam as conclusões deste artigo estão incluídos no artigo.

Abreviações

- B + :

-

Íons de boro

- E OT :

-

Espessura de óxido equivalente

- FETs:

-

Transistores de efeito de campo

- HZO:

-

HfZrO x

- IC:

-

Circuito integrado

- I-MOS:

-

Semicondutor de óxido metálico de ionização de impacto

- MOS:

-

Semicondutor de óxido de metal

- NC:

-

Capacitância negativa

- NCFET:

-

Transistor de efeito de campo de capacitância negativa

- NEMFET:

-

FET nanoeletromecânico

- S / D:

-

Fonte / dreno

- SS:

-

Balanço de sublimiar

Nanomateriais

- Transistores, efeito de campo de junção (JFET)

- Transistores, efeito de campo de porta isolada (IGFET ou MOSFET)

- Transistores de efeito de campo de junção

- Transistores de efeito de campo de porta isolada (MOSFET)

- Introdução aos transistores de efeito de campo de junção (JFET)

- Introdução aos transistores de efeito de campo de porta isolada

- MoS2 com Espessura Controlada para Evolução Eletrocatalítica de Hidrogênio

- Transistores de efeito de campo Nanoflake SnSe multicamadas com contatos óhmicos de baixa resistência

- Estudo do Efeito da Direção de Impacto no Processo de Corte Nanométrico Abrasivo com Dinâmica Molecular

- Fabricação, Caracterização e Atividade Biológica de Sistemas de Nanotransmissão de Avermectina com Diferentes Tamanhos de Partículas