Garantindo o sucesso inicial no projeto de PCB EMC

Como plataforma para componentes cujas aplicações podem ser bem implementadas em produtos eletrônicos, as PCBs (Placas de Circuito Impresso) desempenham um papel fundamental como conexão elétrica entre componentes e respondem pela base em dispositivos ou equipamentos eletrônicos. Portanto, seu desempenho e qualidade levam diretamente ao dos produtos eletrônicos. Juntamente com o rápido desenvolvimento da tecnologia de microeletrônica, vários produtos eletrônicos tendem a trabalhar juntos, de modo que a interferência entre eles aumenta cada vez mais. Além disso, o aumento da densidade do PCB leva ao fato de que a qualidade do projeto do PCB desempenha um papel crítico na determinação da extensão da interferência e da resistência à interferência. Como resultado, além da seleção de componentes e do projeto do circuito, o excelente layout e roteamento de componentes também contribuem para o projeto de PCB EMC (Compatibilidade Eletromagnética) se o circuito for necessário para capturar o desempenho ideal.

EMC refere-se à capacidade do dispositivo ou sistema que eles são capazes de funcionar normalmente em ambiente eletromagnético, recusando-se a gerar interferência eletromagnética inaceitável para dispositivos ou sistemas ambientais. A interferência eletromagnética é formada devido a várias razões resumidas principalmente em frequência de trabalho extraordinariamente alta ou layout ou roteamento inaceitável. Sob o pano de fundo da inevitável alta frequência de rádio (RF), os projetistas devem se concentrar no layout de componentes, roteamento, energia e projeto de aterramento ao implementar o projeto de PCB para preocupação da EMC. Além disso, para PCBs com diferentes contagens de camadas, diferentes elementos de design devem ser levados em consideração para alcançar o desempenho ideal.

Fonte de interferência

• Corrente de modo diferencial e corrente de modo comum

uma. Transmissão em modo diferencial e transmissão em modo comum

Qualquer circuito contém corrente de modo comum (CM) e corrente de modo diferencial (DM). Ambos decidem a extensão da transmissão de RF. Na verdade, existe uma enorme extinção entre eles. Quando um par de derivações ou traços e uma fonte de retorno de referência são fornecidos, qualquer tipo de corrente estará disponível. De um modo geral, os sinais DM transportam dados ou informações úteis. O modo comum, no entanto, causa mais problemas à EMC como efeito negativo da corrente DM. A transmissão DM é geralmente definida como transmissão de linha para linha, enquanto a transmissão CM é geralmente definida como transmissão de linha para terra. A intensidade máxima de campo gerada pelo circuito fechado pode ser calculada pela fórmula

. E refere-se à intensidade máxima de campo (μV/m); r refere-se à distância entre o circuito fechado e a antena de medição (m); f refere-se à frequência (MHz); Eus refere-se a corrente (mA); A refere-se à área do laço (cm²).

. E refere-se à intensidade máxima de campo (μV/m); r refere-se à distância entre o circuito fechado e a antena de medição (m); f refere-se à frequência (MHz); Eus refere-se a corrente (mA); A refere-se à área do laço (cm²). Com base na fórmula acima, é claramente indicado que a intensidade do campo é diretamente proporcional à área do loop. Para reduzir o nível de transmissão DM (TL), a área do loop deve ser reduzida além da redução da corrente da fonte.

A radiação CM resultante da queda de tensão faz com que a tensão de aterramento parcial seja maior do que a do aterramento de referência. O cabo conectado com o sistema de aterramento influente é considerado uma antena que é um componente da radiação CM. O componente de campo distante pode ser representado pela fórmula

, K refere-se ao coeficiente de transmissão; I refere-se à corrente CM (A); l refere-se ao comprimento do cabo (m); f refere-se à frequência de transmissão (MHz); r refere-se à distância (m).

, K refere-se ao coeficiente de transmissão; I refere-se à corrente CM (A); l refere-se ao comprimento do cabo (m); f refere-se à frequência de transmissão (MHz); r refere-se à distância (m). Esta fórmula indica claramente que a intensidade do campo é diretamente proporcional ao comprimento do cabo. A redução da transmissão CM depende da diminuição da corrente CM e da redução do comprimento do cabo.

b. Conversão entre CM e DM

DM e CM podem ser mutuamente convertidos quando duas linhas de sinal com impedância diferente estão disponíveis. A impedância é determinada principalmente por condutores ou capacitor e indutor em forma de pente que são correlacionados com o traçado físico. Para o rastreamento da maioria dos PCBs, a capacitância e a indutância parasitas devem ser bem controladas ao mínimo, de modo que CM e DM possam ser evitados. Portanto, os circuitos que são sensíveis ao ambiente precisam alcançar o equilíbrio através de um determinado método para que a capacitância em forma de fio ou pente de cada condutor seja equivalente à capacitância parasita.

c. Método geral de parar a interferência CM e DM

A diretriz fundamental para interromper a corrente CM e DM e a interferência de RF está no deslocamento da capacidade atual ou na minimização da capacidade atual. À medida que a corrente flui em traços, linhas de força magnética são geradas, levando à ocorrência de campo elétrico. Ambos os campos são capazes de irradiar energia de RF. Se as linhas de força magnética forem deslocadas ou reduzidas ao mínimo, a energia de RF não existirá mais, o que finalmente interromperá a interferência. Medidas ou regras específicas que podem ser conformadas serão discutidas na última parte deste artigo.

• Diafonia

Como um elemento crucial do projeto de PCB, a diafonia deve ser cuidadosamente considerada em cada elo de todo o processo. Crosstalk refere-se ao acoplamento eletromagnético indesejado entre traços, condutores, feixes de cabos, componentes ou outros componentes eletrônicos que tendem a ser influenciados por interferência eletromagnética.

Como uma abordagem de transmissão EMI (Interferência Eletromagnética) líder, a diafonia tende a causar interferência entre os traços. Crosstalk pode ser classificado em acoplamento de capacitância e acoplamento de indutância. O primeiro geralmente deriva do fato de que o traço está localizado sobre outros traços ou plano de referência. Este último geralmente deriva de traços fisicamente aproximados entre si. Quando se trata de traços paralelos, a diafonia apresenta dois modos:para frente e para trás. Para PCBs, o crosstalk inverso vale mais a pena do que o crosstalk direto. Em circuitos, quanto maior a impedância entre a potência e os traços de interferência, maior será o nível de diafonia. A diafonia de indutância pode ser controlada adicionando distância de ponta a ponta entre traços e linhas de transmissão ou condutores ou minimizando a distância entre traços e plano de referência.

• Análise de Espectro de Sinal Digital

uma. Sinais digitais

O atributo dos sinais digitais é onda quadrada e os sinais de onda quadrada são compostos por onda fundamental e muitos senos harmônicos. A transformada de Fourier pode ser aplicada para capturar a forma de onda da faixa de frequência dos sinais digitais. Portanto, quanto menor o período de repetição do pulso, maior será sua frequência de repetição e, portanto, a frequência harmônica. Teoricamente, o tempo de subida da onda quadrada é zero, de modo que o conteúdo harmônico é infinito. No entanto, é uma forma de onda trapezoidal com borda ascendente e borda descendente.

b. Conversão de domínio de tempo de pulso e domínio de frequência (transformada de Fourier)

A transformada de Fourier leva o pulso retangular a ser decomposto em ondas cosseno ou seno, de acordo com a fórmula

. Nesta equação, ADn refere-se à amplitude de cada forma de onda cosseno; n refere-se à contagem de ondas harmônicas; w refere-se à frequência angular.

. Nesta equação, ADn refere-se à amplitude de cada forma de onda cosseno; n refere-se à contagem de ondas harmônicas; w refere-se à frequência angular. • Desacoplamento e Aterramento

uma. Projeto de desacoplamento

Composto por indutor e capacitor, o filtro passa-baixa é capaz de filtrar sinais de interferência de alta frequência. A indutância parasita nas linhas desacelerará a fonte de alimentação de modo que a corrente de saída dos dispositivos de acionamento diminua. A colocação adequada do capacitor de desacoplamento e a aplicação da função de armazenamento de energia do indutor e do capacitor permitem fornecer corrente aos dispositivos no momento de ligar e desligar. Em um loop DC, a mudança de carga irá provocar ruído de energia. A configuração do capacitor de desacoplamento pode impedir que o ruído seja gerado devido à mudança de carga.

b. Projeto de aterramento

Para dispositivos eletrônicos, o aterramento é um método crucial para controlar a interferência. Se o aterramento for combinado corretamente com as medidas de blindagem, a maioria dos problemas de interferência serão resolvidos.

• Layout e roteamento de componentes

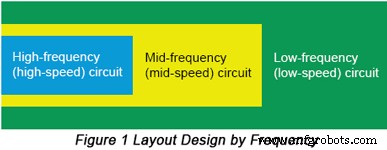

O layout do circuito determina diretamente a extensão da interferência eletromagnética e a intensidade da resistência à interferência. O layout apropriado não apenas aumenta a eficiência do circuito, mas também melhora a EMC de todo o sistema. Quanto maior a frequência de trabalho do circuito da unidade, maior será a velocidade e o espectro do sinal mais diversificado será. Consequentemente, quanto maior a proporção do componente de alta frequência, mais forte será a interferência. Do ponto de vista da frequência, primeiro vem o circuito de alta frequência, depois o circuito de média frequência e, finalmente, o circuito de baixa frequência. Da perspectiva da velocidade lógica, no entanto, primeiro vem o circuito de alta velocidade, depois o circuito de velocidade média e, finalmente, o circuito de baixa velocidade. De acordo com essa teoria, o layout do circuito deve ser implementado de acordo com o projeto a seguir.

Além da classificação de acordo com a frequência ou velocidade, a função e o tipo também podem ser usados como padrão de classificação. As medidas detalhadas a serem tomadas serão discutidas na parte restante deste artigo em breve. Continue lendo e você os obterá em detalhes.

Regras de projeto de PCB para EMC

Como as fontes de interferência que indicam danos ao desempenho EMC dos circuitos foram escavadas, as regras de projeto correspondentes para preocupação com EMC devem ser elaboradas atendendo a essas fontes. Aqui estão as regras de projeto de PCB para alcançar o sucesso da EMC.

• Layout de Superfície

uma. O tamanho do PCB deve ser considerado. Quando se trata de placas com tamanho extraordinariamente grande, o rastreamento tem que percorrer um longo caminho com o aumento da impedância, a redução da resistência ao ruído e o aumento dos custos de fabricação. Quando se trata de placas com tamanho extraordinariamente pequeno, problemas serão causados por dissipação térmica e diafonia tende a ocorrer entre traços adjacentes. O tamanho recomendado do PCB é de forma retangular com relação entre comprimento e largura de 3:2 ou 4:3. Além disso, quando o tamanho da placa ultrapassa 200mm*150mm, a intensidade mecânica retirada pela placa deve ser considerada. Assim, é muito importante que você conheça o limite da dimensão da placa do fabricante do seu PCB. Por exemplo, PCBCart pode imprimir placas de circuito em min 6*6mm e max 600*700mm. Verifique seus recursos de fabricação de PCB personalizados para obter mais detalhes.

b. O particionamento deve ser cuidadosamente considerado para o design do layout do componente. Circuitos digitais, circuitos analógicos e fonte de ruído devem ser colocados independentemente na placa e o circuito de alta frequência deve ser isolado do circuito de baixa frequência. Além disso, deve-se prestar atenção à distribuição de componentes com sinais fortes e fracos e à questão da direção da transmissão do sinal.

c. O layout deve centrar-se no componente principal em cada circuito de função para garantir que o componente seja posicionado de forma uniforme e compacta ao longo da mesma direção. Para impedir que o acoplamento entre os sinais seja formado, os componentes facilmente influenciados pela interferência não devem ser posicionados de forma vizinha.

d. Os componentes de sinal sensível devem estar longe de dispositivos de energia e de alta potência e as linhas de sinal sensível nunca podem passar por dispositivos de alta potência. Os componentes termicamente sensíveis devem ser posicionados longe dos dispositivos térmicos, enquanto os componentes sensíveis à temperatura devem ser posicionados na área com a temperatura mais baixa.

e. A distância deve ser aumentada entre os componentes com alta diferença de potencial para evitar a possibilidade de ocorrência de curto-circuito. Além disso, os componentes de alta potência devem tentar ser dispostos em locais inacessíveis ao toque manual nos testes e passar pela proteção de isolamento.

f. Um orifício passante trará capacitância distribuída de 0,5pF, portanto, uma redução dos orifícios passantes é benéfica para a melhoria da velocidade de operação.

• Layout do Componente

uma. Em comparação com componentes discretos, os componentes IC devem receber seleção prioritária devido às suas vantagens de excelente embalagem, menos juntas de solda e baixa taxa de falha. Além disso, dispositivos com uma inclinação de sinal relativamente lenta devem ser selecionados para que as seções de alta frequência geradas pelos sinais possam ser reduzidas. A aplicação de dispositivos de montagem em superfície pode reduzir o comprimento de rastreamento com impedância reduzida e EMC aprimorada.

b. Os componentes devem ser posicionados com base na mesma classificação. Os componentes incompatíveis devem ser colocados de forma independente para garantir que os componentes não interfiram uns com os outros no espaço.

c. Componentes com peso superior a 15g não devem passar por solda até que sejam consertados pelo suporte. Componentes grandes e pesados e que geram muito calor não devem ser montados a bordo; em vez disso, eles devem ser montados na placa inferior da caixa acabada. Além disso, a dissipação térmica deve ser garantida e os componentes termicamente sensíveis devem estar longe dos componentes geradores de calor.

d. Quando se trata de componentes ajustáveis, como potenciômetro, bobina de indutância ajustável, capacitor variável e microinterruptor, os requisitos estruturais de todo o sistema devem ser considerados. Esses componentes devem ser colocados na placa de circuito se for necessário um ajuste interno, enquanto devem estar em locais compatíveis com a placa da máquina se for necessário um ajuste externo.

• Projeto de roteamento

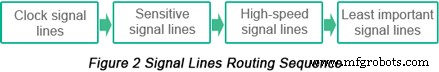

A regra geral de roteamento segue a seguinte sequência:

Além dessa regra geral de roteamento, alguns detalhes nunca devem ser ignorados:

uma. Para minimizar a interferência de radiação, PCBs multicamadas devem ser escolhidos com camadas internas definidas como plano de potência e plano de aterramento para que a impedância do circuito de alimentação possa ser reduzida e o ruído de impedância pública possa ser interrompido com um plano de aterramento uniforme a ser gerado para linhas de sinal. Ele desempenha um papel fundamental na interrupção da radiação, melhorando a capacitância distribuída entre as linhas de sinal e o plano de aterramento. Mais notas de projeto para PCBs multicamadas estão descritas na seção de Camada de PCB e Projeto EMC abaixo.

b. A baixa impedância deve ser mantida em sinais de alta frequência por linhas de energia, linhas de aterramento e traços na placa de circuito. Quando a frequência é mantida tão alta, as linhas de energia, as linhas de aterramento e os traços da placa de circuito tornam-se pequenas antenas responsáveis por receber e transmitir interferências. Para derrotar essa interferência, em comparação com a adição de capacitores de filtragem, é mais importante reduzir a impedância de alta frequência de linhas de energia, linhas de aterramento e traços de placa de circuito. Portanto, os traços na placa de circuito devem ser curtos, grossos e organizados uniformemente.

c. Linhas de energia, linhas de aterramento e traçados impressos devem ser organizados adequadamente para que possam ser curtos e retos para minimizar a área de loop formada por linhas de sinal e linhas de retorno.

d. O gerador de clock deve estar o mais próximo possível dos dispositivos de clock.

e. A carcaça do oscilador de cristal de quartzo deve ser conectada ao terra.

f. O domínio do relógio deve ser circundado por linhas de aterramento e as linhas de relógio devem ser o mais curtas possível.

g. Linhas quebradas com um ângulo de 45° em vez de 90° devem ser aplicadas na placa de circuito para diminuir a transmissão e o acoplamento de sinais de alta frequência.

h. A conexão de ponto único com energia e a conexão de ponto único com terra devem ser aplicadas em PCB de camada única e PCB de camada dupla. Tanto as linhas de energia quanto as linhas de aterramento devem ser tão grossas quanto possível.

i. O circuito de acionamento de E/S deve estar próximo aos conectores na borda da placa de circuito.

j. As linhas principais devem tentar ser grossas e o solo de proteção deve ser adicionado em ambos os lados. As linhas de alta velocidade devem ser curtas e retas.

k. Os pinos dos componentes devem ser os mais curtos possíveis, o que funciona especialmente para desacoplamento de capacitores, utilizando capacitores de montagem sem pinos.

l. Quando se trata de componentes A/D, as linhas de aterramento na seção digital e na seção analógica não devem ser cruzadas.

m. Os sinais de seleção de clock, barramento e chip devem estar longe das linhas e conectores de E/S.

n. Linhas de entrada de tensão analógica, terminal de tensão de referência deve estar longe das linhas de sinal do circuito digital, especialmente clock.

o. A interferência é menor quando as linhas de clock são verticais às linhas de E/S do que paralelas às linhas de E/S. Além disso, os pinos dos componentes do relógio devem estar distantes dos cabos de E/S.

p. O rastreamento nunca deve ser organizado sob cristal de quartzo ou dispositivos sensíveis ao ruído.

q. O loop de corrente nunca deve ser gerado em torno de circuitos de sinal fraco ou circuitos de baixa frequência.

r. Qualquer sinal não deve gerar loop. Se um loop tiver que ser organizado, ele deve ser o menor possível.

• Roteamento de rastreamento

uma. O layout paralelo deve ser realizado em sinais de corrente com a mesma saída, mas direções opostas para eliminar a interferência magnética.

b. A descontinuidade de leads impressos deve ser reduzida ao máximo. por exemplo. a largura do cabo não deve sofrer uma mudança repentina com o canto do cabo superior a 90°.

c. A EMI tende a ser gerada pela maioria das linhas de sinal de clock e as linhas de sinal de clock devem estar próximas ao loop de aterramento no processo de roteamento.

d. O motorista do ônibus deve estar ao lado do ônibus a ser conduzido. Quando se trata de fios longe de PCBs, os drivers devem ser colocados próximos aos conectores.

e. Como as linhas de sinal dos terminais de clock, driver de linha ou drivers de barramento geralmente carregam grandes correntes transitórias, os terminais impressos devem ser o mais curtos possível. Para componentes discretos, a largura do chumbo impresso pode atingir aproximadamente 1,5 mm. Para CIs, no entanto, a largura das derivações impressas deve estar entre 0,2 mm a 1,0 mm.

f. A folha de cobre de grande área deve ser evitada ao redor de dispositivos térmicos ou condutores com grande corrente fluindo, caso contrário, problemas como inflação ou queda da folha de cobre possivelmente serão causados se os produtos permanecerem em ambiente térmico por um longo tempo. Se for necessário usar uma folha de cobre de grande área, é melhor aproveitar a grade, que é benéfica para eliminar o escape de gás gerado devido à adesão térmica entre a folha de cobre e o substrato.

g. A abertura da via no centro do bloco deve ser adequadamente maior do que a dos pinos do componente. A solda a seco tende a ser gerada se as almofadas forem muito grandes.

• Projeto de energia

O design de energia inadequado leva a uma grande geração de ruído, o que acaba reduzindo o desempenho dos produtos. Dois fatores primários causam energia instável:

#1:No estado de comutação de alta velocidade, a corrente de troca transitória é muito grande;

#2:Existe indutância no retorno da corrente.

Como resultado, a integridade da energia deve ser totalmente considerada no projeto de PCB, além do que as seguintes regras também devem ser observadas.

uma. Projeto de filtragem de desacoplamento de energia

A ponte de um capacitor de desacoplamento com capacitância de 0,01μF a 0,1μF em dois terminais de alimentação do chip IC pode reduzir drasticamente o ruído e a corrente de surto em toda a placa. Com a compensação de corrente cumprida, quanto menor a capacitância de desacoplamento, melhor. Os capacitores de montagem devem ser usados de maneira ideal devido à sua baixa indutância de chumbo.

O método mais eficaz para filtrar a energia está na disposição do filtro no fio da fonte de alimentação CA. Para impedir que os condutores se acoplem mutuamente ou ocorram loops, as linhas de entrada e saída do filtro devem ser direcionadas de ambos os lados da placa de circuito e os condutores devem ser o mais curtos possível.

b. Projeto de proteção de energia

O design de proteção de energia abrange proteção contra sobrecorrente, alarme de falta de tensão, partida suave e proteção contra sobretensão. A proteção contra sobrecorrente pode ser alcançada na seção de potência do PCB através da aplicação de fusível. Para impedir que o fusível afete outros módulos no processo de fusão, a tensão de entrada também deve ser projetada para manter a capacitância. Para impedir que a sobretensão danifique os componentes por acidente, um potencial igual deve ser estabelecido por meio de dispositivos de proteção, como tubo de descarga e varistor, entre a linha de distribuição e o potencial de terra para obter proteção contra sobretensão.

• Projeto do solo

Para dispositivos de potencial equivalente com ponto base de potencial elétrico, os fios terra apresentam potencial inconstante. Distinções relativamente grandes podem ser observadas ao usar o medidor para medir o potencial entre pontos nos fios terra, o que eventualmente causará erros quando o circuito estiver funcionando.

A principal razão para EMI por fios terra está na impedância em fios terra. Quando a corrente está fluindo através dos fios de aterramento, a tensão será gerada, que na verdade é o ruído de aterramento. Sob a condução de tal tensão, a corrente de loop nos fios de aterramento será causada, o que posteriormente gera interferência de loop de aterramento. Se dois circuitos geralmente usam o mesmo fio terra, o acoplamento público de impedância ocorrerá.

As soluções para interferência de loop de aterramento contêm corte de loop de aterramento, adição de impedância de loop de aterramento e aplicação de circuito balanceado. Os métodos para anular o acoplamento de impedância pública estão na redução de impedância no fio terra público ou no aterramento de ponto único paralelo. As regras específicas em termos de design do fio terra são as seguintes.

uma. Separação entre terra digital e terra analógica

Se os circuitos analógicos e os circuitos lineares estiverem disponíveis na placa de circuito, eles devem ser isolados um do outro. Os circuitos de baixa frequência devem depender mais do aterramento paralelo de ponto único. Quando ocorrem problemas no processo de roteamento prático, o aterramento em série pode ser parcialmente implementado antes do aterramento paralelo. Os circuitos de alta frequência tendem a depender do aterramento em série multiponto e os fios de aterramento devem ser curtos e grossos. A folha de cobre em forma de grade deve ser aplicada massivamente em torno dos componentes de alta frequência.

b. Os fios de aterramento devem ser tão grossos quanto possível

Os fios de aterramento devem ser tão grossos quanto possível para que a corrente duas vezes maior do que a corrente permitida da PCB possa passar para aumentar a resistência ao ruído. Se o vazamento de cobre for aplicado para fazer fios de aterramento, o cobre morto deve ser evitado. Além disso, cobre com funções semelhantes devem ser conectados entre si através de fios grossos para que a qualidade dos fios terra possa ser garantida com redução de ruído.

c. Circuito de malha fechada formado por fios terra

Para placa de circuito contendo apenas circuitos digitais, a capacidade de resistência ao ruído pode ser aumentada projetando o circuito de aterramento em loop circular.

Camada PCB e design EMC

• Contagem de camada de PCB apropriada

Em termos de contagem de camadas, PCBs de camada única, PCBs de camada dupla e PCBs multicamadas.

uma. PCBs de camada única e PCBs de camada dupla são aplicáveis para roteamento de média/baixa densidade ou circuitos de baixa integridade. Com base na preocupação com o custo de fabricação, a maioria dos produtos eletrônicos de consumo depende de PCBs de camada única ou PCBs de camada dupla. No entanto, ambos geram muita EMI como resultado de defeitos de suas estruturas e também são sensíveis a interferências externas.

b. PCBs multicamadas tendem a ser mais aplicados em roteamento de alta densidade e circuitos de chip de alta integridade. Portanto, quando a frequência do sinal é alta com componentes eletrônicos distribuídos em alta densidade, pelo menos PCBs de 4 camadas devem ser selecionados. No projeto de PCB multicamada, o plano de potência e o plano de aterramento devem ser dispostos especificamente com a distância entre as linhas de sinal e as linhas de aterramento reduzidas. Como resultado, a área de loop de todos os sinais pode ser magnificamente diminuída. Do ponto de vista da EMC, os PCBs multicamadas são capazes de reduzir efetivamente a radiação e melhorar a capacidade anti-interferência.

• Design de PCB de camada única

PCBs de camada única geralmente funcionam em uma baixa frequência de várias centenas de KHz, pois muitas condições de design de alta frequência são limitadas devido a limites de baixa frequência, como falta de retorno do circuito de RF e condições de controle exigidas pelo fechamento completo, efeito óbvio de pele de linha ou problemas inevitáveis de antenas magnéticas e de loop. Portanto, PCBs de camada única tendem a ser sensíveis à interferência de RF, como eletricidade estática, pulso rápido, radiação ou RF conduzida. No projeto de PCB de camada única, a integridade do sinal e a correspondência de terminais não são levadas em consideração. Primeiro vem o design do fio de energia e terra, depois o design de sinal de alto risco que deve ser colocado próximo ao fio terra. Quanto mais perto, melhor. Finalmente vem o design de outras linhas. As medidas específicas de projeto incluem:

a. Os fios de alimentação e de aterramento devem ser assegurados ao longo dos pontos de aterramento da caixa de alimentação na rede de sinal do circuito principal.

b. Os rastreamentos devem ser roteados de acordo com as subfunções e os requisitos de projeto devem ser considerados criticamente em componentes sensíveis e terminais e conectores de E/S correspondentes.

c. Todos os componentes da rede de sinais críticos devem ser colocados adjacentes.

d. Quando os PCBs exigem vários pontos de aterramento, certifique-se de que esses pontos estejam mutuamente conectados entre si e incluam o projeto do método de conexão.

e. Para outras linhas de roteamento, as linhas com maior capacidade de resistência a RF devem utilizar o método de projeto de mini-passagem com caminho de retorno de RF livre no caminho.

• Design de PCB Dupla/Múltipla Camada

uma. O plano de potência chave deve ser disposto adjacente ao plano de aterramento correspondente com a capacitância de acoplamento gerada. Cooperando com o capacitor de desacoplamento de PCB, o plano de potência chave é benéfico para a redução de impedância no plano de potência com excelente efeito de filtragem adquirido.

b. Sinais-chave em planos adjacentes não podem atravessar a zona de divisão para interromper a ampliação do loop de sinal, diminuir a radiação intensa e reduzir a sensibilidade à interferência.

c. Sinais-chave, como sinais de clock, sinais de alta frequência e sinais de alta velocidade, exigem um plano de terra adjacente. Por exemplo, o plano de sinal adjacente ao plano de aterramento pode ser considerado como um plano ideal para roteamento de sinal, de modo que a área do loop de sinal e a radiação de blindagem possam ser reduzidas.

d. O plano de potência deve ser menor que o plano de aterramento geralmente devido à conformidade com a regra 20H.

O projeto EMC para PCBs deriva da complexidade de técnicas, conhecimento e experiência. Todas as regras de projeto listadas neste artigo visam fornecer diretrizes fundamentais e conceituais para que os engenheiros garantam seu primeiro sucesso no projeto EMC. Na verdade, um excelente projeto de EMC exige que os engenheiros levem em consideração o maior número possível de elementos no projeto da placa e os engenheiros devem saber o que são e como reagir a eles.

Recursos úteis:

• A introdução mais abrangente de ferramentas automatizadas EMI e EMC

• Influência do layout de PCB do desempenho de EMC de produtos eletrônicos

• Regras de projeto de particionamento de PCB para aprimoramento de EMC

• Projeto de PCB para Circuito de Radiofrequência e Compatibilidade Eletromagnética

• Três Considerações de Projeto Garantindo EMC de PCB de Laptop

• Serviço de Fabricação de PCB Completo da PCBCart - Várias opções de valor agregado

• Serviço Avançado de Montagem de PCB da PCBCart - Comece a partir de 1 peça

Tecnologia industrial

- Guia para reduzir erros de projeto de PCB

- Redução de emissões de PCB Práticas de design de baixo ruído

- Software de layout de PCB

- Considerações de layout de PCB

- Dicas e truques:aprenda a melhorar seu design atual de PCB

- Tutorial de design de placa de circuito impresso do Ultiboard

- Tutorial de design de PCB KiCAD

- Retrocessos e soluções no projeto de PCB de RF

- Dicas de layout de alta velocidade

- Considerações de design térmico de PCB