O flip-flop J-K

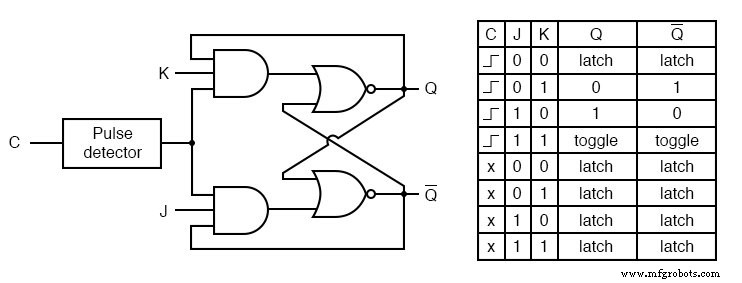

Outra variação do tema multivibradores biestáveis é o flip-flop J-K. Essencialmente, esta é uma versão modificada de um flip-flop S-R sem nenhum estado de saída “inválido” ou “ilegal”. Observe atentamente o diagrama a seguir para ver como isso é feito:

As entradas J e K

O que costumava ser as entradas S e R agora são chamadas de entradas J e K, respectivamente. As antigas portas AND de duas entradas foram substituídas por portas AND de 3 entradas, e a terceira entrada de cada porta recebe feedback das saídas Q e não Q.

O que isso faz para nós é permitir que a entrada J tenha efeito apenas quando o circuito é reiniciado, e permite que a entrada K tenha efeito apenas quando o circuito é definido.

Em outras palavras, as duas entradas são interligadas , para usar um termo lógico de relé, de modo que ambos não possam ser ativados simultaneamente.

Se o circuito estiver “ativado”, a entrada J é inibida pelo status 0 de não-Q por meio da porta AND inferior; se o circuito for “resetado”, a entrada K é inibida pelo status 0 de Q por meio da porta AND superior.

Quando ambas as entradas J e K são 1, no entanto, algo único acontece. Por causa da ação de inibição seletiva dessas portas AND de 3 entradas, um estado "configurado" inibe a entrada J de modo que o flip-flop atua como se J =0 enquanto K =1 quando na verdade ambos são 1.

No próximo pulso de clock, as saídas mudarão (“alternar”) de definidas (Q =1 e não-Q =0) para reinicializar (Q =0 e não-Q =1). Inversamente, um estado de “reset” inibe a entrada K de forma que o flip-flop atue como se J =1 e K =0 quando na verdade ambos são 1. O próximo pulso de clock alterna o circuito novamente de reset para set.

Sequência lógica do flip-flop J-K

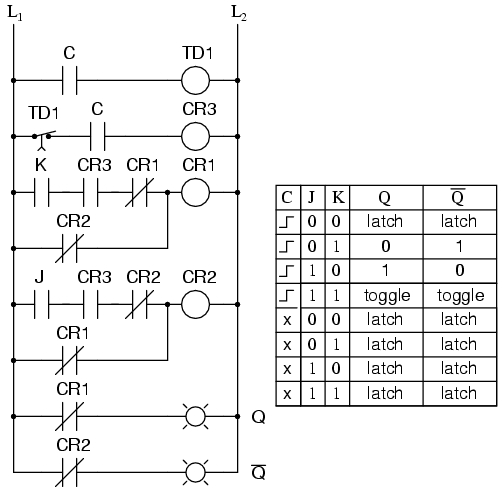

Veja se você pode seguir esta sequência lógica com a lógica ladder equivalente ao flip-flop J-K:

O resultado final é que o estado "inválido" do flip-flop SR é eliminado (junto com a condição de corrida que ele gerou) e temos um recurso útil como um bônus:a capacidade de alternar entre os dois estados de saída (biestáveis) a cada transição do sinal de entrada do relógio.

Não existe trava J-K, apenas flip-flops J-K. Sem o disparo de borda da entrada do relógio, o circuito alternaria continuamente entre seus dois estados de saída quando J e K fossem mantidos altos (1), tornando-o um dispositivo astável em vez de um dispositivo biestável nessa circunstância.

Se quisermos preservar a operação biestável para todas as combinações de estados de entrada, devemos use o disparo por borda para que alterne apenas quando for solicitado, um passo (pulso de clock) de cada vez.

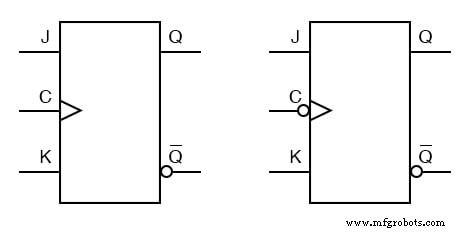

O símbolo de bloco para flip-flops J-K

O símbolo de bloco para um flip-flop J-K é muito menos assustador do que seu circuito interno e, assim como os flip-flops S-R e D, os flip-flops J-K vêm em duas variedades de clock (acionado por borda negativa e positiva):

REVER:

- Um flip-flop J-K nada mais é do que um flip-flop S-R com uma camada adicional de feedback. Este feedback ativa seletivamente uma das duas entradas de definir / redefinir para que ambas não possam transportar um sinal ativo para o circuito multivibrador, eliminando assim a condição inválida.

- Quando as entradas J e K são ativadas e a entrada do relógio é pulsada, as saídas (Q e não-Q) trocarão de estado. Ou seja, o circuito irá alternar de um estado definido para um estado de redefinição ou vice-versa.

PLANILHAS RELACIONADAS:

- Planilha de flip-flops J-K

Tecnologia industrial