Novo SCR de alta tensão de retenção com estrutura de recombinação de portadora incorporada para proteção imune de travamento e proteção ESD robusta

Resumo

Um novo retificador controlado de silício de alta tensão compatível com o processo CMOS (HHV-SCR) para proteção contra descarga eletrostática (ESD) é proposto e demonstrado por simulação e teste de pulso de linha de transmissão (TLP). A região de recombinação de buraco (ou elétron) recém-introduzida H-RR (ou E-RR) não apenas recombina a portadora minoritária na base do transistor PNP (ou NPN) parasita pela camada N + (ou P +), mas fornece a recombinação adicional para eliminar a portadores de avalanche de superfície pela camada P + (ou N +) recém-adicionada em H-RR (ou E-RR), que traz uma melhoria adicional da tensão de retenção ( V h ) Comparado com o V medido h de 1,8 V de retificador controlado por silício disparado de baixa tensão (LVTSCR), o V h de HHV-SCR pode ser aumentado para 8,1 V, mantendo uma corrente de falha suficientemente alta ( I t2 > 2,6 A). Consegue-se uma melhoria de mais de quatro vezes na figura de mérito (FOM).

Introdução

Com o desenvolvimento da tecnologia integrada de semicondutor e a miniaturização consistente do tamanho do recurso do dispositivo semicondutor, o dano ao dispositivo induzido por ESD está se tornando mais grave. Ao custo de uma grande área de chip, os dispositivos convencionais, tais como MOSFET de canal N aterrado por diodo e porta (ggNMOS) apresentando robustez ESD normal, foram relatados [1]. A fim de realizar a capacidade ESD aprimorada com uma dimensão de dispositivo menor, o retificador controlado por silício disparado de baixa tensão (LVTSCR) tem sido considerado um dispositivo atraente devido à sua capacidade de alta corrente por unidade de área [2]. Para aplicações de baixa tensão, devido à tensão de disparo baixo embutida ( V t1 ) ggNMOS, o LVTSCR com excelente robustez ESD é capaz de fornecer uma velocidade de resposta ESD mais rápida do que a obtida em SCR convencional. No entanto, o forte feedback positivo inerente causa um V extremamente baixo h (1 ~ 2 V), que é responsável pelo engate e disparo incorreto transiente [3]. Esses efeitos negativos podem ser efetivamente suprimidos simplesmente aumentando V h [3,4,5,6,7,8,9,10,11]. O dispositivo ficará livre do travamento e do disparo incorreto transitório, enquanto o V h é maior do que a tensão da fonte de alimentação (VDD). Consequentemente, a região N + ESD e a região P + LDD foram adicionadas ao SCR com máscaras adicionais e etapas de implante de íons para melhorar V h [3]. No entanto, a robustez ESD pode se deteriorar devido à dissipação de energia adicional junto com o V aumentado h . Além disso, a tecnologia de grampo de tensão do emissor para V h melhoria com corrente de falha aceitável ( I t2 ) também foi proposto [5]. No entanto, o V h nas abordagens acima mencionadas não é ajustável, o que ainda apresenta inconvenientes e limitações em aplicações versáteis.

Nesta carta, um novo retificador controlado de silício de alta tensão de retenção (HHV-SCR) é proposto e demonstrado por simulação TCAD e testes TLP. O dispositivo atinge simultaneamente alto V h , alto eu t2 , e ajustável V h sem quaisquer máscaras e etapas adicionais. O teste TLP foi realizado para validar que o V h pode ser melhorado de forma eficaz, mantendo um nível de I suficientemente alto t2 . De acordo com os resultados testados, o HHV-SCR apresenta mais de quatro vezes maior V h do que no LVTSCR com a degradação insignificante em I t2 .

Método

Neste trabalho, um novo SCR de alta tensão com uma estrutura de recombinação de portadora embutida é investigado. Os modelos físicos IMPACT.I, BGN, CONMOB, FLDMOB, SRH e SRFMOB são usados na simulação numérica. Com base no modelo, H-RR e E-RR são otimizados para atingir alto V h e alto P M . Os HHV-SCRs e LVTSCR fabricados são testados pelo sistema TLP.

Estrutura e mecanismo

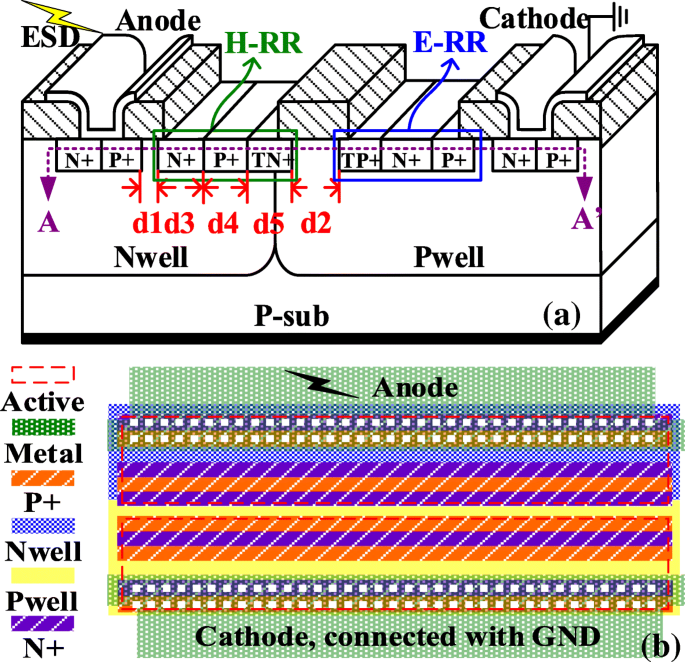

A vista esquemática em corte transversal do HHV-SCR proposto e o diagrama de layout são mostrados na Fig. 1a, b, respectivamente. Os recém-introduzidos H-RR e E-RR formados por N + e P + flutuantes são idênticos ao N + e P + nas áreas do ânodo e do cátodo, respectivamente. O N + flutuante em H-RR (ou P + flutuante em E-RR) é colocado próximo à região P + no ânodo (ou região N + no cátodo). Além disso, o novo P + flutuante em H-RR (ou N + flutuante em E-RR) também está localizado próximo ao N + flutuante acima mencionado em H-RR (ou P + flutuante em E-RR). O N + de gatilho baixo em H-RR (TN +) e P + de gatilho baixo em E-RR (TP +) também são fabricados pelos mesmos processos que a região N + (ou P +) no ânodo (ou cátodo) para garantir o V t1 dentro de uma faixa aceitável. Como uma tensão ESD positiva ( V ESD ) subindo até um certo nível, a junção TN + / P-well / TP + com uma baixa tensão de ruptura quebrará primeiro, seguida pelo snapback dos transistores parasitas acionados pela corrente de avalanche. O forte feedback positivo dos BJTs parasitas é responsável pelo V consideravelmente baixo h do LVTSCR. No HHV-SCR, o N + em H-RR (ou o P + em E-RR) irá recombinar os portadores minoritários injetados da borda do ânodo P + (ou cátodo N +), o que reduz o ganho de corrente ( β ) do PNP parasita (ou NPN) e elimina o efeito bipolar de superfície. É importante notar que o P + em H-RR (ou o N + em E-RR) bloqueia o caminho de baixa resistência da superfície ao recombinar os elétrons da superfície (ou lacunas). Comparado com o H-RR sem P + (ou E-RR sem N +), o novo P + em H-RR (ou o N + em E-RR) fornece a recombinação adicional para eliminar os elétrons de superfície (ou buracos) injetados do cátodo ( ou ânodo) e aqueles induzidos por ionização de impacto (mostrado na Fig. 3a), o que provoca o aumento adicional de V h . Ao combinar essas modificações, uma melhoria significativa no FOM é verificado. A figura de mérito (FOM) é citada de [7] e definida como a densidade de potência tolerável de um único dispositivo dada por FOM =( V h · Eu t2 ) / ( N · W ) para avaliar o V h e eu t2 desempenho de um único dispositivo. Geralmente, acompanhada pela melhoria de V h desempenho, ainda causa a degradação de I t2 devido à dissipação de alta potência. Portanto, o FOM mais alto significa que o único dispositivo pode atingir a capacidade de corrente mais alta no V mais alto h nível ( N é o número do dispositivo de empilhamento; W é a largura do dispositivo).

a A visão esquemática em corte transversal do HHV-SCR proposto. b O diagrama de layout do HHV-SCR proposto

Resultados e discussão

Resultados simulados

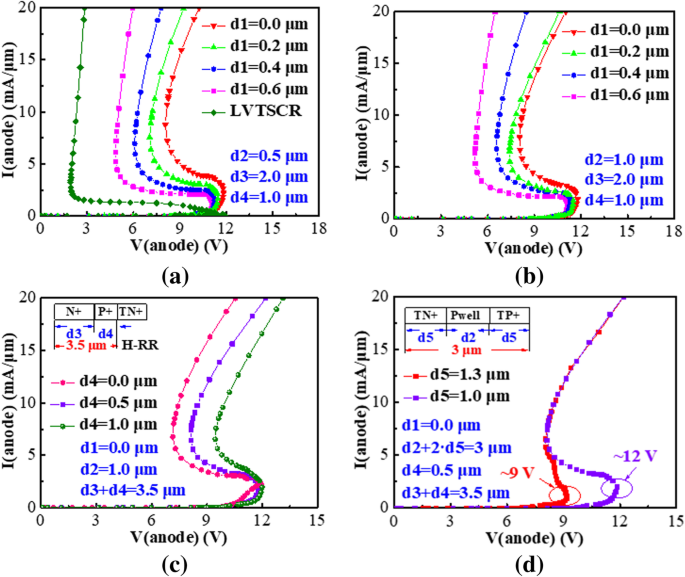

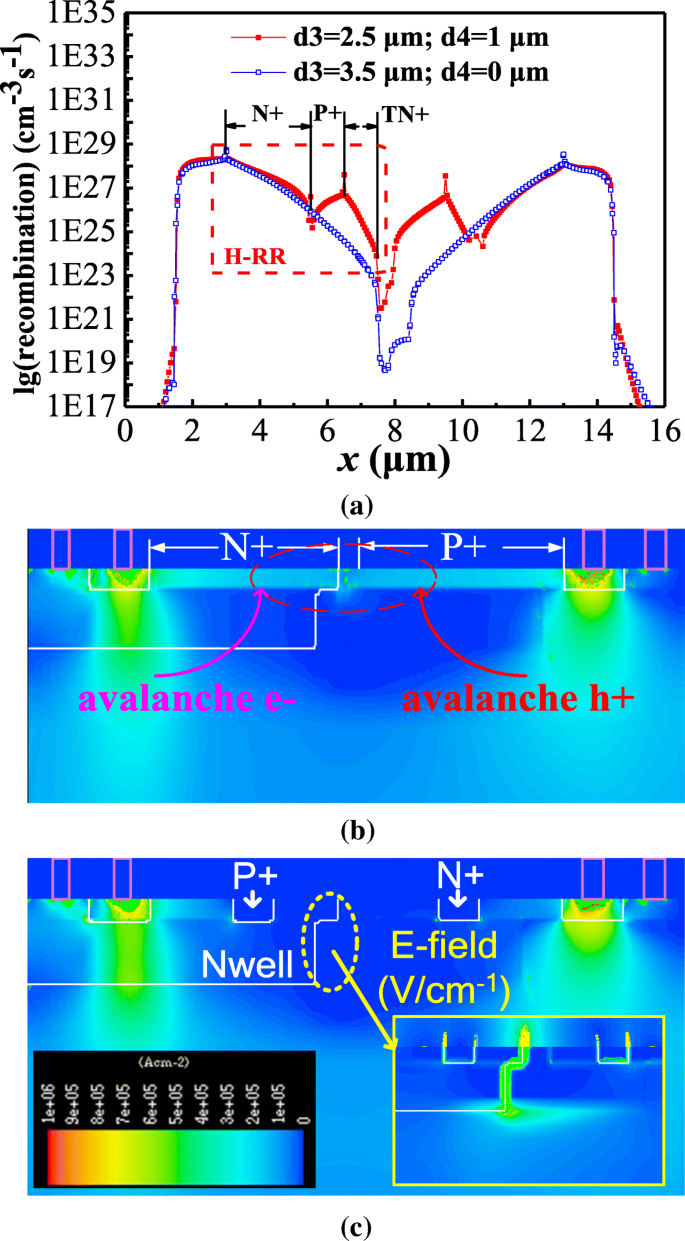

As características do dispositivo foram estudadas e simuladas pelo TCAD Medici, onde os modelos correspondentes, como ionização por impacto e modelo de mobilidade dependente da concentração, foram usados. As curvas I-V simuladas do LVTSCR e HHV-SCRs são mostradas na Fig. 2. O V h do LVTSCR é tão baixo quanto 1,8 V, enquanto o V h do HHV-SCR é melhorado de 4,6 V para 8,1 V com d1 diminuído de 0,6 μm para 0 μm para d2 =0,5 μm. Na verdade, o menor d1 é favorecido para melhorar a capacidade de recombinação de N + em H-RR (ou P + em E-RR) para obter um menor β , o que explica que o HHV-SCR sempre atinge o V mais alto h para d1 =0 μm. Os resultados simulados na Fig. 2b indicam que o V h de HHV-SCR é ainda melhorado com d2 aumentado de 0,5 para 1 μm devido ao aumento do comprimento do dispositivo. Para demonstração, o P + em H-RR (ou N + em E-RR) também é um fator chave para aumentar V h . Os resultados simulados são mostrados na Fig. 2c. Quando o H-RR (ou E-RR) com d3 + d4 fixo é completamente formado por dopagem pesada N + (ou P +) (por exemplo, d3 =3,5 μm, d4 =0 μm), o simulado V h é 7,1 V. Ao inserir P + dentro de H-RR e N + dentro de E-RR com d3 + d4 fixo (por exemplo, d3 =2,5 μm, d4 =1,0 μm), o V simulado h pode ser aumentado até cerca de 9,5 V. Pode-se inferir que o novo P + em H-RR (ou N + em H-RR) é eficaz na recombinação de elétrons de avalanche de superfície (ou lacunas) para bloquear o caminho da corrente de superfície. Portanto, um V superior h é necessário para o HHV-SCR sustentar a mesma corrente de retenção ( I h ) A curva de recombinação apenas a linha AA ′ mostrada na Fig. 3a demonstra o aumento da taxa de recombinação induzida por novo P + em H-RR (ou N + em E-RR). O TN + e o TP + são adotados para garantir o V t1 dentro de uma faixa aceitável. Ajustando d2 e d5 no d5 + d2 + d5 fixo, o V t1 de HHV-SCR pode ser significativamente reduzido de 12 V para 9,0 V para atender a janela de projeto de circuitos de 5 V com o impacto insignificante em V h , mostrado na Fig. 2d. Os diagramas de distribuição de corrente dos dispositivos simulados no ponto de espera também são mostrados na Fig. 3b, c, respectivamente. Comparado com a distribuição de corrente no HHV-SCR com d3 =3,5 μm, d4 =0 μm, o caminho da corrente de superfície no HHV-SCR proposto está bloqueado devido à taxa de recombinação adicional beneficiada por P + em H-RR e N + em E -RR.

Características simuladas de snapback I-V de LVTSCR convencional e HHV-SCR proposto com o d1 aumentando de 0 μm para 0,6 μm em a d2 =0,5μm e b d2 =1μm. c As curvas I-V de HHV-SCR com diferentes d3 e d4 para o d3 + d4 fixo (d3 + d4 =3,5 μm). d As curvas I-V de HHV-SCR com vários V t1

a As curvas de distribuição de recombinação e as distribuições atuais de HHV-SCR com ( b ) d3 =3,5 μm, d4 =0 μm, e ( c ) d3 =2,5 μm, d4 =1 μm

Resultados Experimentais

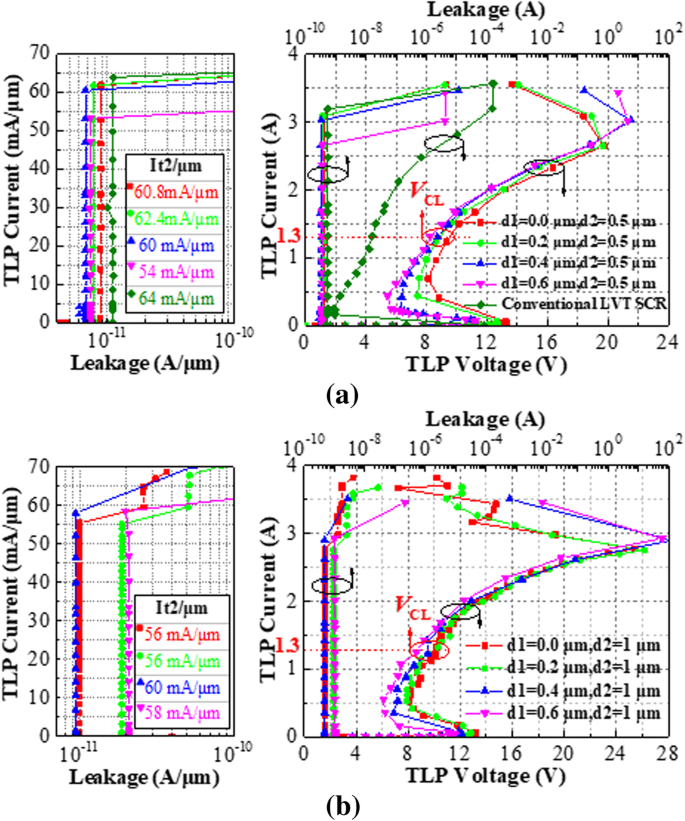

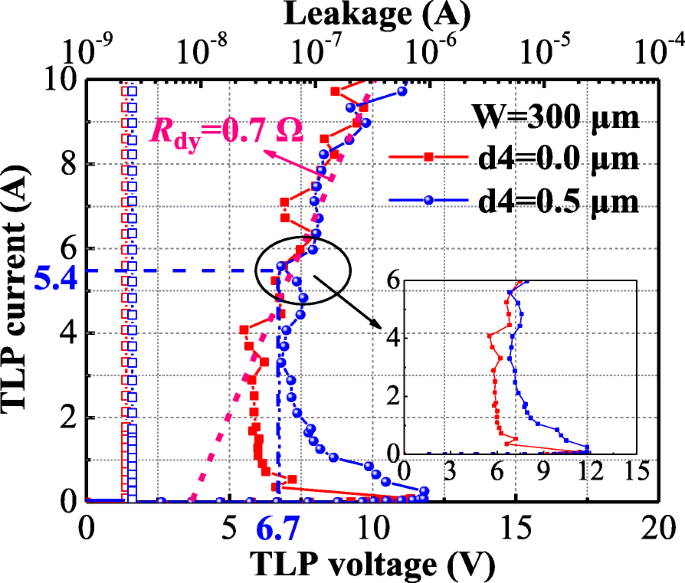

Os dispositivos fabricados são testados pelo sistema TLP. As larguras totais (W) de todos os SCR testados são 50 μm e com um único dedo para a comparação do parâmetro (Tabela 1). Todos os dispositivos testados ocupam a área de layout semelhante. Os parâmetros do dispositivo são mostrados na Tabela 2. A Figura 4a mostra as curvas de medição TLP dos HHV-SCRs com d2 =0,5 μm (chamados dispositivos B1) e o LVTSCR. De acordo com os resultados experimentais, o V h de HHV-SCR é aumentado de 5,5 para 8,0 V com o d1 diminuído de 0,6 μm para 0,0 μm, que é muito maior do que 1,8 V obtido no LVTSCR convencional. Conforme o d2 aumenta de 0,5 para 1 μm, os HHV-SCRs correspondentes (chamados dispositivos B2) obtêm um V maior h mostrado na Fig. 4b. Considerando a janela de projeto, a tensão de aperto ( V CL ) sob o índice fornecido também é um parâmetro-chave para avaliar a capacidade de fixação. Dos resultados testados, o V CL de HHV-SCR de dedo único também é mantido dentro da faixa aceitável no HBM =2 kV ( I TLP =1,3 A) embora a largura do dedo seja de apenas 50 μm. No entanto, todos os dispositivos não podem fornecer o V elegível CL sob o estresse ESD mais forte devido ao alto V h e grande resistência dinâmica ( R dy ) induzida pela largura subdimensionada do dispositivo. Para satisfazer o maior requisito de ESD no chip, a largura do dedo é estendida para 300 μm aceitáveis para d1 =0,6 μm, d4 =0,5 μm e d1 =0,6 μm, d4 =0 μm. O teste de TLP mostrado na Fig. 5 demonstra que o HHV-SCR com d4 =0,5 μm apresenta o R extremamente baixo dy (cerca de 0,7 Ω), robustez ESD superior ( I t2 > 10 A) e alto V h de 6,7 V. Pode-se observar que o V CL é tão baixo quanto 6,7 V no I TLP =5,4 A (HBM =8 KV). Além disso, quanto maior o V h beneficiou de P + em H-RR (ou N + em E-RR) também é provado, em comparação com a curva TLP de SCR com d4 =0 μm. Os resultados testados de dispositivos de dedo único de 50 μm estão listados na Tabela 1.

Corrente de falha experimental na largura da unidade e características TLP I-V correspondentes de LVTSCR convencional e HHV-SCRs propostos com a d2 =0,5 μm e b d2 =1 μm em W =50 μm

Característica experimental de TLP de HHV-SCR com d4 =0,0 μm e d4 =1,0 μm em d1 =0,6 μm, W =300 μm

Conclusão

Um novo HHV-SCR compatível com o processo CMOS é estudado e medido por simulação TCAD e sistema TLP. Comparado com o LVTSCR convencional, os recursos HHV-SCR melhoraram significativamente V h (uma melhoria de mais de 450% no V h é alcançado) e sem sacrificar a área de chip. Além disso, o V h do HHV-SCR pode ser ajustado de 5,5 V a 8,1 V para satisfazer os diferentes V h requisitos com degradação insignificante em I t2 . Em termos de P M , em comparação com o LVTSCR convencional, uma melhoria de mais de 200% também é alcançada.

Disponibilidade de dados e materiais

Todos os dados gerados ou analisados durante este estudo estão incluídos neste artigo publicado.

Nanomateriais

- Um resumo sobre tecnologia IC para microcontroladores e sistemas incorporados

- Maxim:transceptor IO-Link duplo com regulador DC-DC e proteção contra surtos

- TRS-STAR:sistemas incorporados robustos e sem ventoinha de avalue

- Novel Biocompatible Au Nanostars @ PEG Nanopartículas para imagens In Vivo CT e propriedades de depuração renal

- Nanoesferas de carbono monodispersas com estrutura porosa hierárquica como material de eletrodo para supercapacitor

- Melhoria de modulação e absorção de frequência do microbolômetro THz com estrutura de microponte por antenas tipo espiral

- Novela dupla mitocondrial e nanopartículas de direcionamento do receptor CD44 para liberação desencadeada por estímulos redox

- Morfologia, estrutura e propriedades ópticas de filmes semicondutores com Nanislands GeSiSn e camadas deformadas

- Automação e segurança cibernética:proteção completa para clientes

- Materiais e design de PCB para alta tensão