Um regulador de tensão transiente aprimorado com estabilidade e reforço de rejeição da fonte de alimentação

Resumo

Um regulador de tensão de alta estabilidade (VR) é proposto neste artigo, que integra o aumento de transiente e proteção de sobrecorrente (OCP). Levando em consideração o desempenho e as vantagens de área dos dispositivos de baixa tensão, a maioria das partes de controle do VR proposto são fornecidas pela tensão de saída regulada, que forma a técnica de auto-alimentação (SPT) com reforço de rejeição da fonte de alimentação (PSR). Além disso, a estabilidade e a resposta transitória são aprimoradas pela técnica de carga dinâmica (DLT). Um loop de realimentação de sobrecorrente embutido também é adotado para proteger o VR apresentado de danos em situações de sobrecarga. O VR proposto é implementado em uma tecnologia BCD padrão de 350 nm, cujos resultados indicam que o VR pode trabalhar continuamente com tensão de entrada de 5,5–30 V, faixa de carga de 0–30 mA e capacitor de saída de 0,1–3,3 μF. Uma regulação de linha de 2,98 μV / V e uma regulação de carga de 0,233 mV / mA são alcançadas com uma limitação de corrente de 40 mA. O PSR é melhor do que -64 dB até 10 MHz com um capacitor de saída de 0,1 μF.

Introdução

Em projetos modernos de sistema em chip (SoC) em escala nanométrica, diferentes sub-blocos geralmente requerem trilhos de abastecimento diferentes para realizar algumas funções específicas. Além disso, todo o sistema SoC pode precisar operar sob uma ampla faixa de tensão de entrada e ainda fornecer alto desempenho não afetado pelas mudanças nas condições de alimentação [1]. Assim, o regulador de tensão (VR) de ampla faixa de tensão de entrada implementado em tecnologia em escala nanométrica pode ser um dos candidatos mais adequados para este tipo de aplicações. Comparado com sua contraparte de comutação, como regulador de comutação e bomba de carga, o VR linear tem a vantagem de alta precisão, baixo ruído de saída e tamanho compacto. A maioria dos VRs lineares desempenha sua função de regulação de tensão com uma única fonte de tensão, mas apenas alguns podem alcançar a combinação de ampla faixa de fonte de alimentação, baixo ruído, transiente rápido, capacidade de alta carga e recursos extras de proteção [2,3,4] .

Para realizar uma ampla gama de fontes de alimentação, a utilização de transistores que possam suportar pressões de alta tensão é necessária. No entanto, este tipo de transistores geralmente ocupa mais área e tem pior desempenho em comparação com os transistores padrão. Duas das soluções existentes para reduzir o uso de transistores de alta tensão são o método pré-regulador [5, 6] e o método dos transistores de baixa tensão empilhados [7, 8]. O primeiro usa um pré-regulador adicional para fornecer uma tensão de alimentação interna para o regulador central. O último implementa transistores de baixa tensão empilhados e bem projetados para manter as tensões terminais dos transistores dentro do limite da tecnologia [7]. No entanto, esses métodos limitam o headroom de tensão. Este artigo adota a técnica de auto-alimentação (SPT) para atingir uma ampla faixa de fonte de alimentação, o que significa que a maioria dos módulos centrais no circuito de regulação são alimentados pela tensão de saída regulada do VR proposto [9]. Sem nenhum circuito adicional, o desempenho do VR pode ser melhorado pelo SPT e também reduzir o número de dispositivos de alta tensão.

Ao usar o SPT, o primeiro estágio de ganho do amplificador de erro (EA) é fornecido pela tensão de saída regulada do VR proposto. Ao projetar cuidadosamente o segundo estágio do EA, o ruído de alta frequência da tensão de entrada tem pouco impacto na tensão de saída do EA. Além disso, a arquitetura do transistor de potência do tipo N é adotada neste artigo. Portanto, o regulador proposto tem alta rejeição de fonte de alimentação (PSR) e bom desempenho de ruído [10,11,12,13,14,15].

A resposta transitória rápida também é um índice importante para medir o desempenho dos VRs [16,17,18,19,20], o que geralmente é obtido pela adição de um loop de aceleração extra [21]. Neste artigo, o aprimoramento transiente é realizado pela técnica de carregamento dinâmico (DLT). Durante o procedimento de resposta transiente, o DLT introduz uma corrente adicional alterada correspondentemente com as condições de carga para atuar como uma carga dinâmica, pela qual o overshoot e undershoot da tensão de saída regulada podem ser suprimidos [9].

Com a ajuda do DLT, a estabilidade do loop dentro de uma ampla faixa de carga é fortalecida porque a corrente de carga adicional pode reduzir a variação da posição do pólo não dominante. Para tornar o loop estável, a compensação de Miller com resistor de anulação também é usada para gerar um pólo de baixa frequência e um zero extra para compensar o pólo de saída. Além disso, uma série de resistores com o capacitor de saída introduz outro zero para compensar o pólo gerado pela capacitância da porta parasita do transistor de potência [6, 9, 22, 23].

Finalmente, uma malha de limitação de corrente embutida é projetada para evitar danos de sobrecorrente e melhorar a confiabilidade do VR proposto [9, 24,25,26,27].

Este artigo está estruturado da seguinte forma. O princípio e o mecanismo do VR proposto são ilustrados na seção “Método”, incluindo o circuito de proteção de sobrecorrente (OCP), o circuito de reforço de transiente e DLT, o método de reforço de estabilidade e a análise de PSR. Os resultados de desempenho e comparações com outras literaturas publicadas relacionadas são mostrados na seção “Resultados e discussão”. A seção “Conclusão” tira a conclusão da RV proposta.

Método

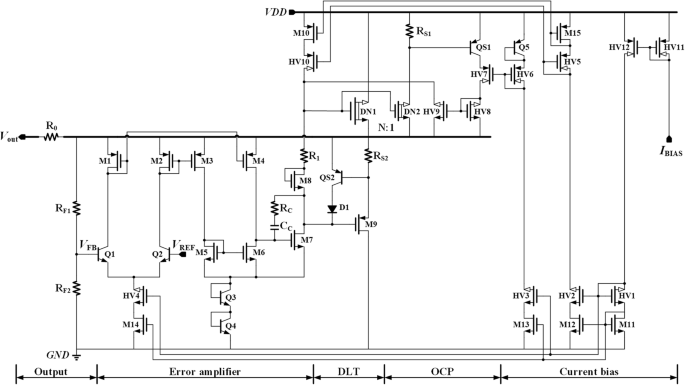

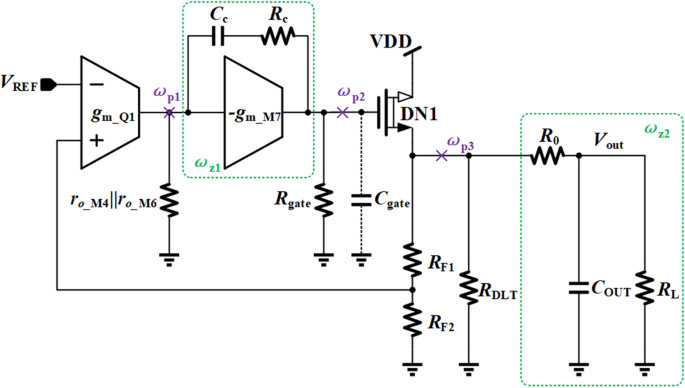

O circuito detalhado do VR proposto é mostrado na Fig. 1. Transistores MOS de baixa tensão padrão, transistores de alta tensão, BJTs, transistores LDMOS de depleção do tipo N (MOS difundido lateralmente) e diodos são chamados de M n , HV n , Q n , DN n e D n , respectivamente na figura, onde n é o número de sequência do dispositivo relevante.

O circuito detalhado do VR proposto

O VR proposto inclui principalmente cinco submódulos:polarização de corrente, OCP, DLT, EA e estágio de saída. O circuito de polarização de corrente fornece corrente de polarização para todo o sistema regulador [12, 14]. A tensão de referência pode ser gerada de muitas maneiras diferentes [1], e o circuito detalhado não é mostrado aqui. Um loop de limitação de corrente embutido funciona como um circuito OCP para limitar a corrente de carga a um valor predefinido. O circuito de aprimoramento de transiente, que é implementado pelo DLT, atinge o overshoot e a supressão de undershoots por meio da mudança adaptativa da corrente de carga durante o procedimento transiente. O loop de regulação de feedback negativo é formado por EA e o estágio de potência de saída para ajustar a tensão de saída. Supondo que a tensão de saída V SAÍDA e, portanto, a tensão de feedback V FB fosse menor do que o valor desejado, a tensão da porta do transistor de potência DN1 seria puxada para cima com a ajuda do loop de regulação para aumentar a tensão de saída e vice-versa. Finalmente, a tensão de saída pode estabilizar em

$$ {V} _ {\ mathrm {OUT}} \ aprox {V} _1 ={V} _ {\ mathrm {REF}} \ left ({R} _ {\ mathrm {f} 1} + {R} _ {\ mathrm {f} 2} \ right) / {R} _ {\ mathrm {f} 2} $$ (1)

Na Fig. 1, pode-se notar que a tensão de saída do VR proposto também alimenta o primeiro estágio de ganho do EA, que é denominado SPT. Com esta técnica de multiplexação de potência, a maioria dos dispositivos no circuito de regulação pode ser implementada por dispositivos de baixa tensão. Em comparação com suas contrapartes de alta tensão, os dispositivos de baixa tensão têm maior desempenho, menor custo e menor área, o que faz com que o circuito de regulação proposto alcance uma boa capacidade de regulação com muito mais facilidade. Quanto ao segundo estágio de EA, Q3 e Q4 são adicionados para levantar o trilho de alimentação de aterramento, que é adotado para limitar a tensão de dreno-fonte de M7, V DS_M7 . Em outras palavras, Q3 e Q4 podem impedir M7 de alta pressão de tensão.

Por uma questão de simplicidade, o circuito simplificado é usado para ilustrar as ideias de inovação na análise subsequente.

Circuito OCP proposto

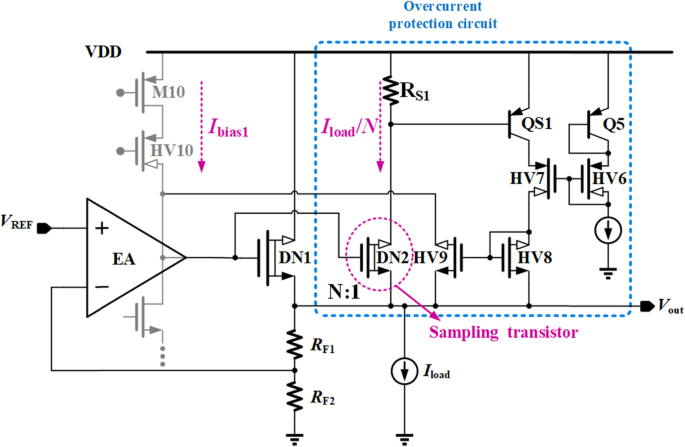

A Figura 2 mostra o circuito OCP proposto. A malha de limitação de corrente proposta pode alterar automaticamente o modo de operação de acordo com diferentes condições de carga. A corrente máxima do VR proposto pode ser limitada reduzindo a tensão da porta do transistor de potência quando ocorre sobrecarga.

Princípio do OCP proposto

O mecanismo de OCP proposto é o seguinte. O transistor de amostragem DN2 detecta proporcionalmente a corrente fluindo através de DN1, que é aproximadamente igual à corrente de carga I Carregar , o que faz com que a tensão caia em R S1 , V RS1 , refletem o nível de corrente de carga. Uma vez V RS1 atinge a tensão de ativação de QS1, HV8 e HV9 formará um espelho de corrente para desviar de uma corrente do segundo estágio de EA. Em seguida, a tensão da porta de DN1 pode ser reduzida para limitar a corrente de carga a um valor predefinido, que pode ser expresso como

$$ {I} _ {\ mathrm {Carregar}} \ le N \ times \ left ({V} _ {EB \ left (\ mathrm {QS} 1 \ right)} / {R} _ {S1} \ right ) $$ (2)

onde N é a razão do fator de tamanho de DN1 para DN2. O objetivo de Q5 e HV6 é fornecer uma tensão de polarização adequada para HV7 e, assim, proteger QS1 da condição de sobretensão.

Há um loop de feedback negativo embutido no OCP proposto. O ganho de loop T e o pólo dominante p dominante deste loop de limite de corrente pode ser dado por,

$$ T ={g} _ {m \ _ \ mathrm {DN} 2} {R} _ {S1} {g} _ {m \ _ \ mathrm {QS} 1} {R} _ {\ mathrm {portão } \ _ \ mathrm {OC}} $$ (3) $$ {p} _ {\ mathrm {dominante}} =1 / \ esquerda ({R} _ {\ mathrm {portão} \ _ \ mathrm {OC} } {C} _ {\ mathrm {portão}} \ direita) $$ (4)

onde g m_DN2 e g m_QS1 são a transcondutância de DN2 e QS1, respectivamente. R gate_OC ≈ ( g m_HV10 r o_HV10 r o_M10 ) || r o_M7 || r o_HV9 e C portão ≈ C gs_DN1 são a resistência de saída e capacitância equivalentes no nó de porta do transistor de potência DN1 quando ocorre sobrecorrente, respectivamente. Quando o VR proposto normalmente opera sem sobrecorrente, HV9 está na região de corte e, portanto, a resistência de saída equivalente no nó da porta de DN1 denominado R portão pode ser expresso como [( g m_HV10 r o_HV10 r o_M10 ) || r o_M7 ]

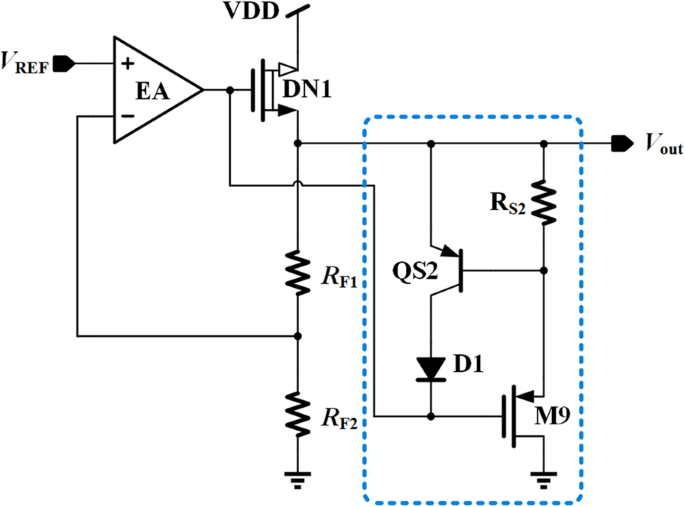

DLT proposto e circuito de aprimoramento de transiente

A Figura 3 mostra o circuito de intensificação de transiente usando DLT. Uma vez que a corrente de carga é proporcional a Vgs_DN1 e inversamente proporcional a Vsg_M9, a corrente que flui através de M9 é maior na condição de carga leve e próxima de zero sob condição de carga pesada. Portanto, à medida que a corrente de carga aumenta, uma corrente diminuída pode ser introduzida na carga de saída total. Por este método, este circuito pode ser equalizado para uma carga dinâmica, o que pode ser útil tanto para o aumento do transiente quanto para o aumento da estabilidade do circuito de regulação.

O circuito de intensificação de transiente proposto

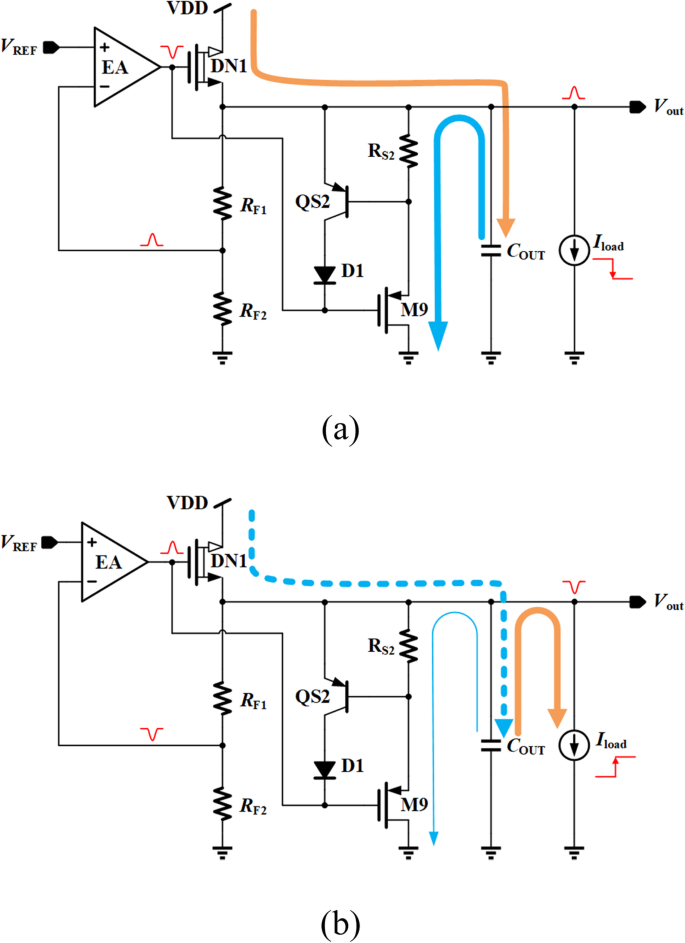

O princípio operacional de aprimoramento transiente detalhado é o seguinte. Se a corrente de carga sofrer uma diminuição repentina, a corrente que flui através do transistor de potência DN1 não mudará imediatamente devido à capacidade limitada de ajuste de loop e taxa de variação. Esta corrente, mostrada na Fig. 4a como um caminho amarelo, causará um overshoot na tensão de saída e, assim, aumentará a queda de tensão em R S2 e M9. Em seguida, uma corrente adicional fluindo através de R S2 e M9, mostrado na Fig. 4a como um caminho azul, é gerado na saída regulada para cancelar a indesejada corrente de caminho amarelo. Portanto, o pico de tensão de saída é reduzido de forma eficaz.

Resposta transitória do VR proposto. a mudança de corrente de carga pesada para leve. b mudança de corrente de carga leve para pesada

A Figura 4b demonstra o caso de mudança de corrente de carga leve para pesada, onde ocorre um undershoot na saída regulada e, em seguida, a corrente fluindo através de R S2 e M9 diminui. Isso pode ser equivalente a fornecer uma carga de corrente reduzida, de forma que a corrente líquida que flui através do transistor de potência DN1 seja aumentada e a supressão de tensão inferior possa ser alcançada.

Para proteger M9 de sobrecorrente, QS2 e D1 são adicionados. Quando a tensão passa de R S2 for maior do que a tensão de ativação de QS2, a corrente extra fluirá para QS2 e D1. A corrente máxima em M9 é definida em

$$ {I} _ {\ mathrm {M} 9 \ _ \ max} \ le \ left ({V} _ {BE \ _ QS2} / {R} _ {S2} \ right) $$ (5)

O objetivo de D1 é evitar que QS2 caia na região de amplificação reversa e flua uma corrente reversa nela, o que é um estado anormal da função de limite de corrente M9.

Aumento da estabilidade da RV proposta

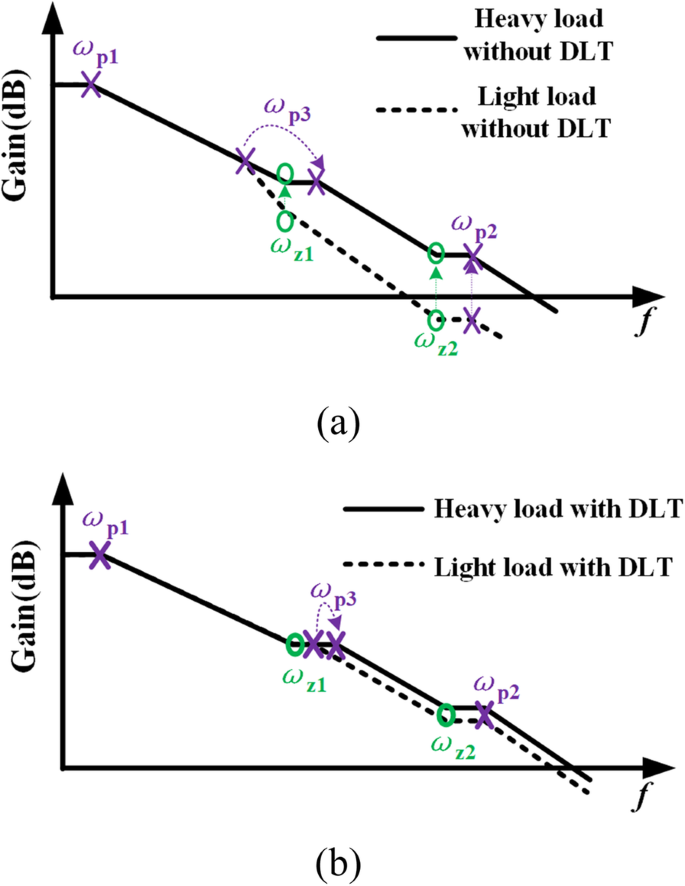

Conforme mostrado na Fig. 5, existem três pólos ω p1 , ω p2 e ω p3 , e dois zeros ω z1 e ω z2 na malha de controle, e o ganho da malha do VR proposto é

$$ {A} _ {\ mathrm {Vloop}} ={A} _O \ beta $$ (6)

Distribuição de polos e zeros do VR proposto

onde A O é o ganho de malha aberta do VR, e β é o coeficiente de feedback,

$$ {A} _O ={A} _ {\ mathrm {CD} 0} {A} _ {E0} \ frac {\ left (1 + s / {\ omega} _ {Z1} \ right) \ left ( 1 + s / {\ omega} _ {Z2} \ right)} {\ left (1 + s / {\ omega} _ {P1} \ right) \ left (1 + s / {\ omega} _ {P3} \ right) \ left (1 + s / {\ omega} _ {P2} \ right)} $$ (7) $$ \ beta =\ frac {R _ {\ mathrm {F} 2}} {R _ {\ mathrm {F} 1} + {R} _ {\ mathrm {F} 2}} $$ (8)

onde A CD0 ≈ 1 é o ganho de baixa frequência do estágio de potência que opera como um seguidor de tensão e A E0 é o ganho de baixa frequência do EA,

$$ {A} _ {E0} ={g} _ {m \ _Q1} \ left ({r} _ {o \ _M4} \ Big \ Vert {r} _ {o \ _M6} \ right) {g} _ {m \ _M7} {R} _ {\ mathrm {portão}} $$ (9)

Considerando o efeito Miller e a capacitância parasita no nó da porta de DN1, os pólos e zeros são escritos como [13]

$$ {\ omega} _ {p1} =1 / \ left [{g} _ {m \ _M7} {R} _ {\ mathrm {gate}} {C} _c \ times \ left ({r} _ { o \ _M4} \ Big \ Vert {r} _ {o \ _M6} \ right) \ right] $$ (10) $$ {\ omega} _ {p2} ={g} _ {m \ _M7} / { C} _ {\ mathrm {gate}} $$ (11) $$ {\ omega} _ {p3} =1 / \ left \ {\ left [{R} _L \ Big \ Vert \ left ({g} _ {m \ _ \ mathrm {DN} 1} ^ {- 1} \ Big \ Vert {R} _ {\ mathrm {DLT}} + {R} _0 \ direita) \ direita] {C} _ {\ mathrm { OUT}} \ right \} $$ (12) $$ {\ omega} _ {z1} =1 / \ left [{C} _c \ left ({R} _c-1 / {g} _ {m \ _M7 } \ right) \ right] $$ (13) $$ {\ omega} _ {z2} =1 / \ left [\ left ({R} _0 \ Big \ Vert {R} _L \ right) {C} _ {\ mathrm {OUT}} \ right] $$ (14)

onde R DLT é a resistência equivalente do circuito de realce de transiente; C SAÍDA é o capacitor de saída do VR proposto.

Já que o capacitor de compensação C C é ampliado em ( g m_M7 R portão ) devido ao efeito miller no nó p1, o pólo ω p1 é o pólo dominante. O segundo pólo deve ser ω p3 , porque C SAÍDA geralmente está na faixa de vários microfarads. Embora o capacitor parasita C portão é relativamente grande, ainda é menor que a capacitância equivalente no nó p1 e o capacitor de saída. Além disso, a resistência no nó p2 é apenas 1 / g m_M7 . Portanto, o pólo ω p2 está localizado em alta frequência. O zero ω z1 é cancelar o pólo de frequência média ω p3 . O resistor R 0 gera um zero ω z2 para compensar o pólo parasita interno ω p2 . A estabilidade do VR proposto pode ser melhorada como resistor R 0 aumentando. No entanto, o resistor R 0 aumentará o erro da tensão de saída devido à queda de tensão causada pela corrente de carga. Portanto, resistor R 0 deve ser definido em um valor razoável para fazer uma boa compensação entre a precisão da tensão de saída e a estabilidade do circuito.

Em um regulador de tensão convencional sem DLT, o pólo no nó de saída estará em uma frequência diferente por causa da variação da corrente de carga, variação da transcondutância do transistor de potência induzida. Conforme a corrente de carga aumenta, a transcondutância do transistor de potência g m _DN1 aumentará e, portanto, o pólo de saída se moverá em direção à alta frequência, enquanto outros zeros e pólos se manterão na mesma posição, como mostrado na Fig. 6a. Isso pode tornar a compensação de frequência do sistema mais difícil e retardar a resposta transitória em condições de carga leve. Mais seriamente, o sistema pode ser instável.

Resposta de frequência do regulador de tensão. a Regulador de tensão sem técnica de carga dinâmica. b O regulador de tensão proposto com a técnica de carga dinâmica

Com o auxílio do DLT proposto, o VR apresentado tem melhor estabilidade com diferentes cargas. Conforme analisado anteriormente, a corrente através do circuito de carga dinâmica diminui à medida que a corrente de carga aumenta no estado estacionário e vice-versa. Uma vez que esta corrente é fornecida por DN1, ela pode suprimir as variações de transcondutância de DN1 dentro de uma faixa de corrente de carga mais ampla, o que é útil para a estabilidade do sistema e constância de largura de banda durante uma faixa de carga mais ampla usando o DLT proposto. A resposta em frequência do VR proposto está na Fig. 6b, o que pode garantir a estabilidade com resposta transitória rápida.

O capacitor de saída define a posição do zero ω z2 . Colocando o pólo zero razoavelmente, o sistema terá melhor estabilidade com diferentes C SAÍDA .

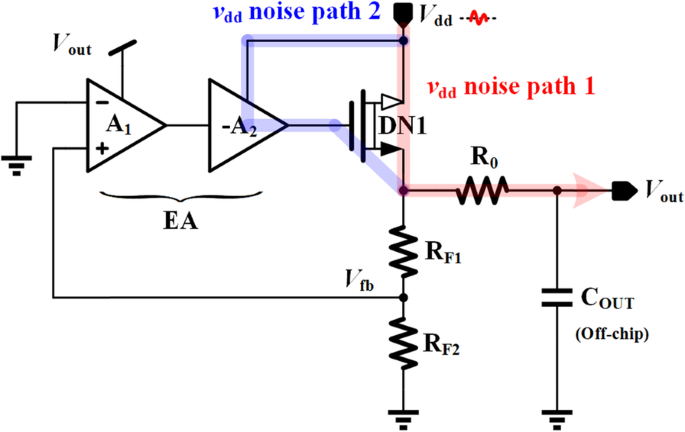

Análise PSR da RV proposta

PSR é um dos parâmetros críticos para medir o desempenho de reguladores de tensão, e se refere à capacidade de rejeição contra ondulações de alta frequência e ruídos oriundos da tensão de alimentação. O método de análise PSR proposto por Gupta 12 é adotado nesta seção, cuja ideia principal é simplificar todo o sistema regulador em um modelo divisor de tensão. Conforme mostrado na Fig. 7, existem dois caminhos de ruído de V dd para V fora :o caminho 1 transfere diretamente o ruído do dreno do transistor de potência DN1 para V fora ; o caminho 2 é do segundo estágio do EA até a porta do transistor de potência DN1. O efeito do caminho 2 pode ser expresso como

$$ {A} _ {\ mathrm {caminho} 2} \ approx \ frac {r_ {o \ _M7}} {g_ {m \ _ \ mathrm {HV} 10} {r} _ {o \ _ \ mathrm { HV} 10} {r} _ {o \ _M10}} $$ (15)

Análise PSR do VR proposto

Conforme mostrado em (15), A caminho2 é bem pequeno com a ajuda da estrutura de espelho atual proposta do SPT e do cascode. Isso torna a influência do caminho 1 dominante na análise PSR.

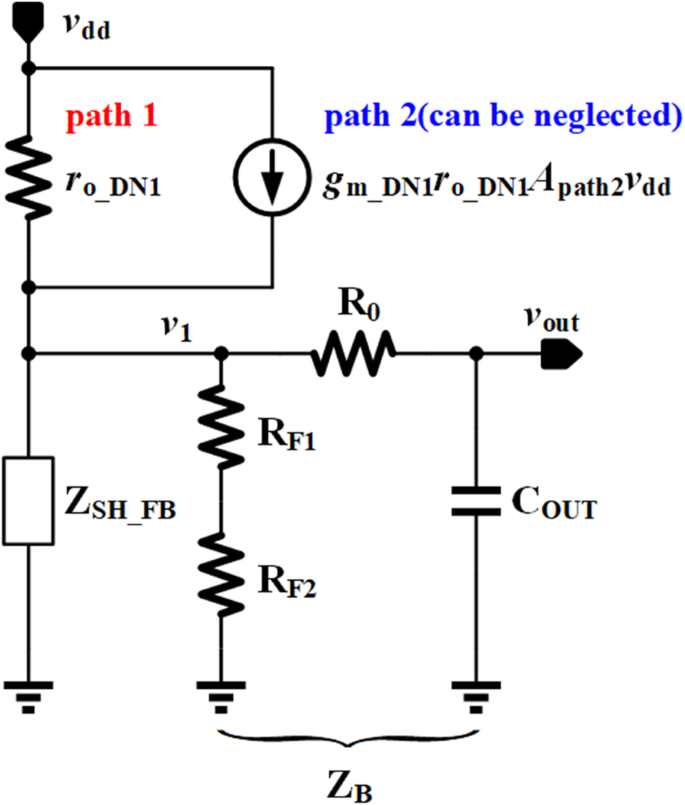

O modelo PSR simplificado do VR proposto é mostrado na Fig. 8, onde r o_DN1 é a resistência de saída do transistor de potência DN1 responsável pelo caminho de ruído 1, a fonte de corrente controlada se origina do caminho de ruído 2, Z B consiste em R F1 , R F2 , R 0 e C SAÍDA atuando como um filtro em alta frequência, e Z SH_FB é a impedância equivalente, incluindo a função de loop de feedback negativo. Z SH_FB pode ser dado por

$$ {Z} _ {SH \ _ FB} =\ frac {1} {g_ {m \ _ DN1} \ left (1+ \ beta {A} _E \ right)} $$ (16)

O modelo simplificado de PSR

onde g m_DN1 é a transcondutância do transistor de potência DN1. Portanto, a função de transferência PSR pode ser expressa como

$$ \ mathrm {PSR} =\ frac {V _ {\ mathrm {out}}} {V _ {\ mathrm {dd}}} =\ frac {\ left (1+ {g} _ {m \ _ \ mathrm { DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} {A} _ {\ mathrm {caminho} 2} \ direita) \ left ({Z} _B \ Big \ Vert {Z} _ { \ mathrm {SH} \ _ \ mathrm {FB}} \ right)} {r_ {o \ _ \ mathrm {DN} 1} + {Z} _B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} $$ (17)

Definindo deliberadamente o ganho intrínseco de HV10 muito maior do que o transistor de potência DN1, g m_DN1 r o_DN1 A caminho2 <<1 pode ser alcançado e, portanto, a fonte de corrente controlada pode ser desprezada. A expressão de PSR pode ser ainda mais simplificada como

$$ \ mathrm {PSR} \ approx \ frac {Z_B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} {r_ {o \ _ \ mathrm {DN} 1} + {Z} _B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} $$ (18)

Desde Z B e Z SH_FB mudará com a variação de frequência, é necessário analisar a característica de frequência do PSR.

A baixa frequência

Em baixa frequência, o ganho de EA é muito alto, e C SAÍDA pode ser tratado como circuito aberto. Assim, Z B >> Z SH_FB e o PSR pode ser escrito como

$$ {\ mathrm {PSR}} _ {\ mathrm {LF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} \ left (1+ \ beta {A} _ {E0} \ right)} $$ (19)

A frequência média

A impedância de Z SH_FB aumentará porque o ganho do loop diminui na frequência média. Nesta fase, o Z SH_FB ainda é pequeno e o PSR é afetado principalmente pelo ganho do loop. Com relação a (7), o PSR pode ser expresso como

$$ {\ mathrm {PSR}} _ {\ mathrm {MF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} \ left (1+ \ beta {A} _ {E0} \ right)} \ frac {1 + s / {\ omega} _p} {1 + s / \ left [{\ omega} _p \ left (1 + \ beta {A} _ {E0} \ right) \ right]} $$ (20)

Conforme mostrado em (20), o PSR está piorando, e o ruído da tensão de saída é mais sério enquanto a frequência aumenta dentro da frequência de ganho unitário.

A alta frequência

Devido ao aumento da frequência, Z SH_FB torna-se grande e finalmente fecha para 1 / g m_DN1 . A impedância de C SAÍDA torna-se menor, mas ainda é muito maior do que R 0 . Então R 0 pode ser omitido como antes. O PSR de alta frequência depende da divisão de tensão entre r o_DN1 e 1 / g m_DN1 em paralelo com C SAÍDA , que pode ser representado por

$$ {\ mathrm {PSR}} _ {\ mathrm {HF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1}} \ frac {1} {1 + s {C} _ {\ mathrm {OUT}} / {g} _ {m \ _ \ mathrm {DN} 1}} $$ (21)

Em alta frequência, o ruído na tensão de saída pode ser bastante suprimido devido ao efeito de C SAÍDA .

Conforme analisado anteriormente, a boa capacidade anti-ruído em toda a faixa de frequência do VR proposto é garantida por três aspectos. Em primeiro lugar, é adotado alto ganho de loop; Em segundo lugar, o SPT faz com que o ruído da fonte de alimentação tenha pouco impacto na porta do transistor de potência; Em terceiro lugar, o capacitor de saída C SAÍDA pode melhorar o PSR na alta frequência com propriedade de filtragem.

Resultados e discussão

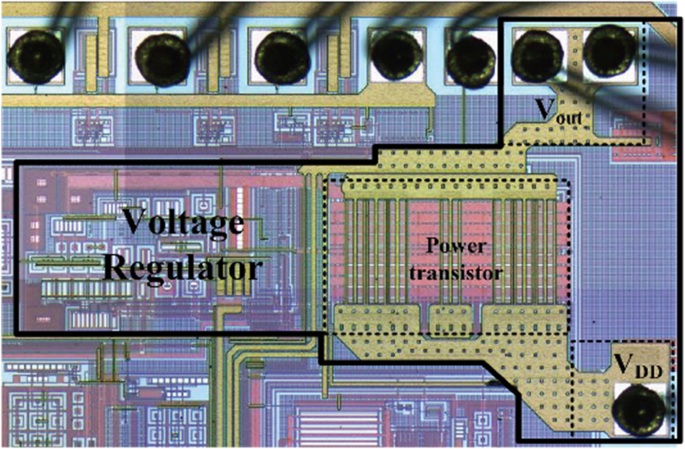

O VR proposto foi implementado em uma tecnologia BCD padrão de 0,35 μm. A foto do chip do regulador fabricado é mostrada na Fig. 9, cuja área do núcleo ativo do VR é 290 μm × 900 μm.

A foto do chip de VR proposto

A tensão de saída regulada do VR proposto é de 5 V com a tensão de alimentação variando de 5,5 a 30 V. O capacitor de saída é um capacitor de cerâmica de baixo custo. A capacitância do capacitor de saída pode ser definida de 100 nF a 3,3 μF.

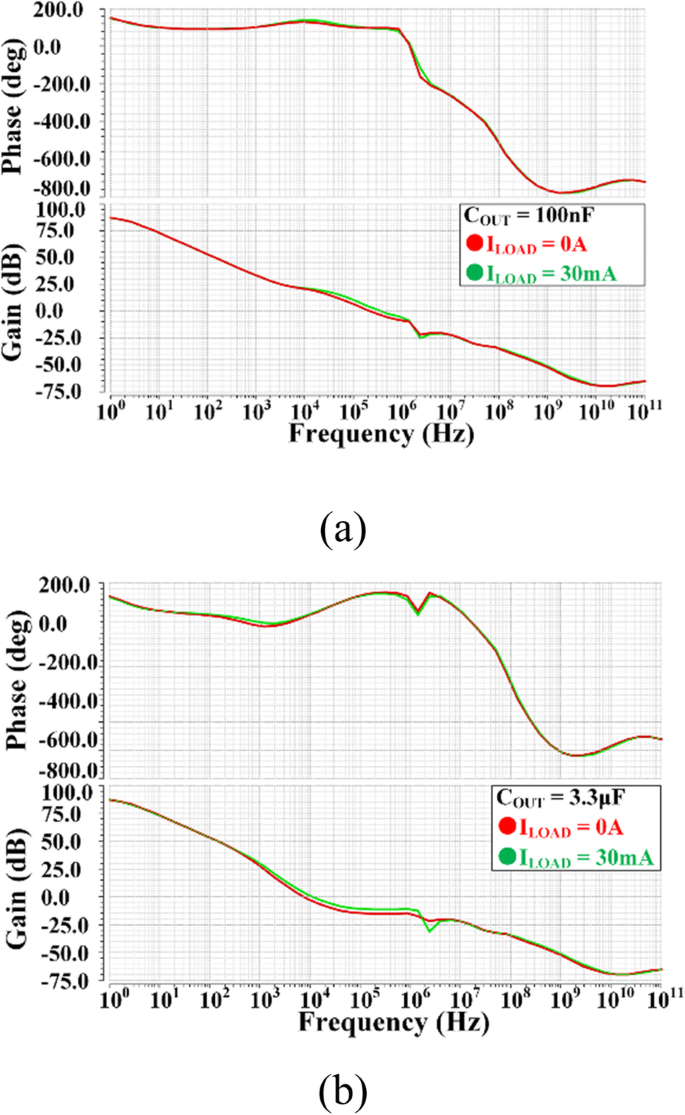

A Figura 10 demonstra a resposta de frequência do VR proposto em diferentes condições de carga com capacitor de saída de 100 nF e 3,3 μF. O LDO proposto pode se manter estável em uma ampla faixa de valor do capacitor de saída, e a forma de onda da resposta de frequência do loop tem uma diferença muito pequena entre a corrente de carga de 0 e 30 mA, que se beneficia do DLT proposto analisado anteriormente.

Respostas de frequência de loop do VR proposto sob diferentes valores de I Carregar e C SAÍDA condições. a C SAÍDA =100 nF, b C SAÍDA =3,3 훍 F. A linha vermelha e verde representa I Carregar de 0 A e 30 mA, respectivamente

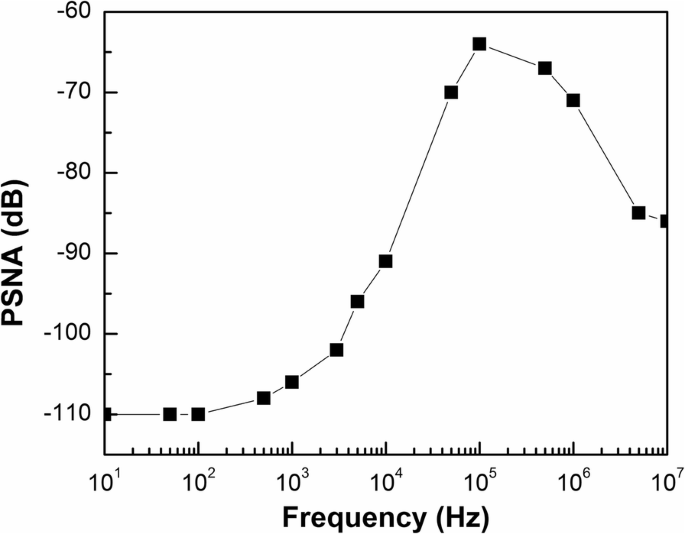

O resultado da verificação do PSR com capacitor de saída de 0,1 μF é mostrado na Fig. 11, onde a - 110 dB em baixa frequência e melhor que - 64 dB até 10 MHz é obtido. Na baixa frequência, o VR proposto tem bom PSR devido ao alto ganho da malha. O PSR torna-se pobre dentro da frequência de ganho unitário por causa do pólo dominado ω p . O capacitor de saída C SAÍDA melhora a característica PSR na alta frequência. Esses resultados mostram que está de acordo com a análise anterior, e o VR proposto obtém melhor PSR em toda a faixa de frequência.

PSR de VR proposto

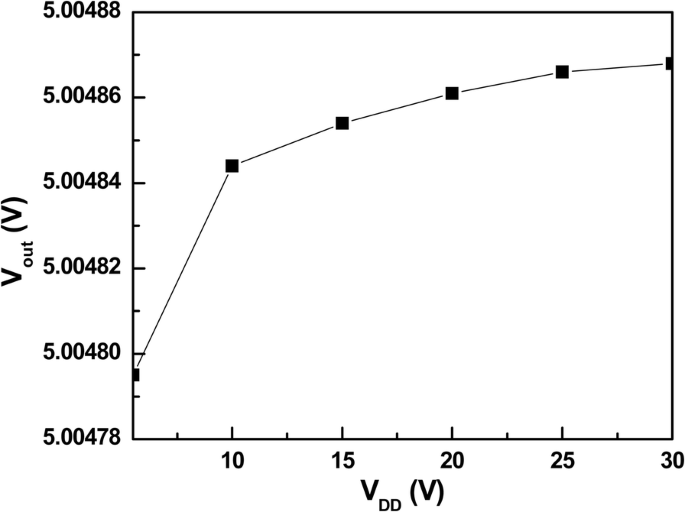

O resultado da regulação da linha do VR proposto é mostrado na Fig. 12. Na faixa de tensão de entrada de 5,5 a 30 V, a tensão de saída varia apenas 73,53 μV, o que resulta em uma regulação da linha de apenas 2,98 μV / V. Isso confirma a eficácia do SPT proposto.

Regulação da linha de VR proposto

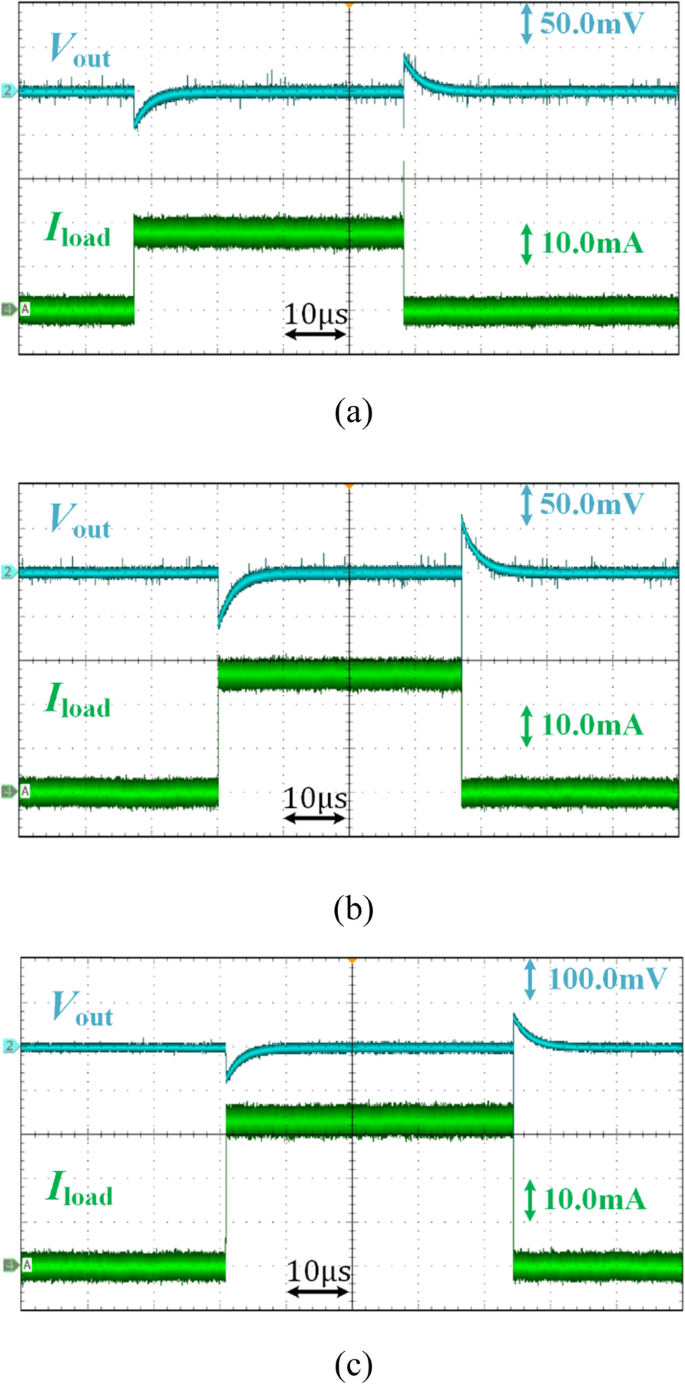

A Figura 13 mostra a resposta transitória da tensão de saída devido a diferentes correntes de carga. O pico e a queda da tensão de saída regulada é de cerca de 43 mV, 65 mV, 83 mV quando a corrente de carga muda de 0 para 18 mA, 28 mA e 32 mA, respectivamente. Isso resulta em uma regulação de carga de 0,233 mV / mA, que é causada principalmente por R 0 para a estabilidade com uma ampla faixa de capacitância de saída.

Forma de onda de resposta transiente do VR proposto devido à etapa de corrente de carga diferente. a 0 a 18 mA; b 0 a 28 mA; c 0 a 32 mA

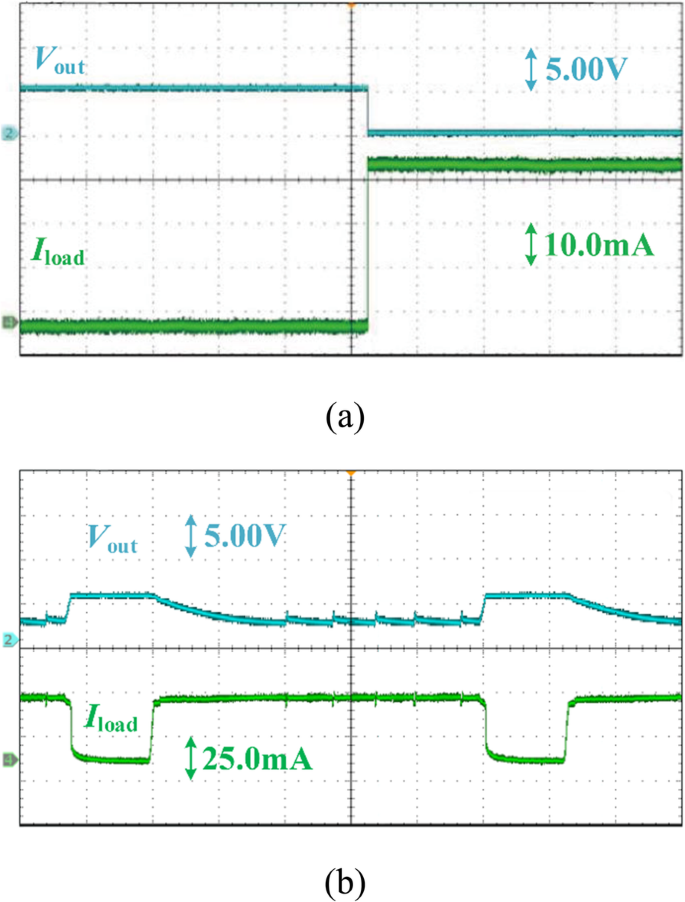

O OCP medido é mostrado na Fig. 14. Para verificar a eficácia do OCP, o curto-circuito é adotado na Fig. 14a. Conforme mostrado na Fig. 14a, quando a sobrecorrente ocorre com a tensão de saída sendo puxada para o solo, a corrente de saída do VR proposto é mantida em cerca de 40 mA. A Figura 14b ilustra uma resposta transitória entre sobrecorrente e carga normal, o que indica que o VR proposto tem capacidade de autorrecuperação quando sai da sobrecarga.

A medição OCP do VR proposto. a curto-circuito de saída; b transitório entre sobrecorrente e carga normal

A Tabela 1 fornece uma comparação de desempenho da LDO proposta e algumas outras LDOs publicadas anteriormente. Em comparação, este LDO possui a melhor regulação de linha e PSR, que se beneficia do SPT proposto. A área ativa será reduzida ainda mais se for fabricada em um processo mais avançado.

A Tabela 2 fornece outra comparação de desempenho com foco nos LDOs que também possuem ampla faixa de fonte de alimentação. Com a ajuda dos DLT e SPT propostos, este trabalho tem a melhor regulação de linha e a mais ampla faixa de fonte de alimentação em comparação com outros LDOs. A função OCP adicional torna este trabalho mais competitivo e confiável.

Conclusão

Um SPT VR de alta estabilidade com DLT e OCP é implementado em um processo BCD padrão de 0,35 μm. Com a ajuda do SPT, a maior parte do circuito de regulação é fornecida por uma tensão de saída regulada, o que é benéfico para a estabilidade e melhoria do PSR. O DLT proposto é útil para resposta transitória e estabilidade. Além disso, o circuito OCP embutido pode evitar que o VR apresentado seja danificado por sobrecarga ou curto-circuito. A regulação linear do VR proposto é de 2,98 μV / V com VDD de 5,5 a 30 V, enquanto a tensão de saída regulada é de 5 V, e a regulação de carga é de 0,233 mV / mA com corrente de carga de 0 A a 30 mA. A tensão de overshoot e undershoot durante a mudança da corrente de carga também é pequena usando o circuito de intensificação de transiente apresentado. O PSR em baixa frequência é - 110 dB, e é melhor do que - 64 dB até 10 MHz. Alta estabilidade de loop pode ser alcançada em uma ampla faixa de capacitor de saída e corrente de carga e, portanto, o VR proposto é adequado para aplicações que requerem alto desempenho e confiabilidade sob variações de capacitor de saída e corrente de carga.

Disponibilidade de dados e materiais

All data generated or analysed during this study are included in this published article.

Abreviações

- VR:

-

Voltage regulator

- OCP:

-

Proteção de sobrecorrente

- SPT:

-

Self-power technique

- PSR:

-

Power supply rejection

- DLT:

-

Dynamic load technique

- EA:

-

Error amplifier

Nanomateriais

- Regulador de tensão

- Equações e leis do circuito CC

- Circuitos Averager e de verão

- Tensão e corrente

- Capacitores e cálculo

- Tensão complexa e cálculos de corrente

- Maxim:transceptor IO-Link duplo com regulador DC-DC e proteção contra surtos

- ST:regulador de comutação com amplas faixas de tensão

- Liderando com Persistência e Perseverança

- 5 etapas para reimaginar a arquitetura operacional e impulsionar os resultados com IoT