Um modulador delta-Sigma de intervalo dinâmico de 80 dB com largura de banda de 100 Mhz e taxa de clock de 2,4 Ghz

Resumo

A largura de banda de um Δ Σ o modulador é limitado pela taxa de clock devido ao requisito de taxa de sobreamostragem. Como os processos CMOS em nanoescala estão se desenvolvendo rapidamente, é possível projetar largura de banda ampla e alta faixa dinâmica de tempo contínuo Δ Σ moduladores para aplicações de alta frequência. Este artigo propõe um tempo contínuo de 4 bits de 3ª ordem Δ Σ modulador com uma topologia feedforward de loop único. Este modulador é projetado em um processo CMOS de 40 nm e atinge faixa dinâmica de 80 dB e largura de banda de 100 MHz a uma taxa de clock de 2,4 GHz. O modulador consome 69,7 mW da fonte de alimentação de 1,2 V.

Introdução

Impulsionados pelas demandas crescentes em aplicativos de comunicação sem fio, como padrões de celular, os conversores analógico-digital (ADCs) evoluem rapidamente para oferecer suporte a uma largura de banda de sinal mais alta (BW) e faixa dinâmica (DR). O requisito de BW no padrão de comunicação Long-Term-Evolution Advanced (LTE-A) aumentou para 100 MHz. Nyquist ADCs, tipicamente pipeline ADCs [1, 2], têm sido usados em macro estações base para seu alto BW. No entanto, os buffers de entrada indispensáveis para a condução de capacitores de entrada chaveada com ruído térmico limitado e filtro anti-aliasing causam consumo de energia significativo e complexidade de design. Além disso, o fato de que os ADCs de pipeline dependem de um ganho preciso entre os estágios, o que determina o amplificador de resíduo de banda larga de alto ganho e a tecnologia de calibração, leva à complexidade e à dissipação de energia. Δ Σ Os ADCs são conhecidos por seu alto desempenho e eficiência energética, empregando tecnologia de sobreamostragem e modelagem de ruído. No entanto, o requisito de taxas de sobreamostragem (OSRs), que normalmente é superior a 16 [3–6], determina a frequência de amostragem além de GHz. Recentemente, Δ Σ ADCs que excedem 50 MHz BW foram propostos usando processos CMOS em nanoescala, que permitem uma taxa de clock multi-GHz. Anteriormente, alta frequência Δ Σ ADCs geralmente adotam realizações de tempo contínuo (CT) [3-9] em vez de realizações de tempo discreto (DT). O último é implementado por circuito de capacitor chaveado, e sua precisão depende do casamento de capacitor, o que significa que uma operação robusta sob variação de processo é oferecida. Além disso, é fornecida imunidade superior ao jitter do clock, uma vez que as constantes de tempo dos capacitores e interruptores são suficientemente pequenas. No entanto, como a operação de amostragem é executada antes do modulador, o filtro anti-aliasing é necessário. Por outro lado, devido ao requisito de estabilização para garantir a estabilidade nos estágios, os amplificadores operacionais em moduladores DT são implementados com largura de banda de ganho unitário (UGBW) mais ampla do que os moduladores CT. Em resumo, os moduladores DT podem fornecer alta precisão, mas sinal estreito [10, 11] e são amplamente usados para implementar aplicações de medição, como sensores inteligentes e imagens biomédicas. Em contraste, tem havido um esforço mais amplo para projetar moduladores CT para aplicações de alta frequência do que os DT com complexidade e consumo de energia comparáveis.

O exigente destino do projeto de maior BW em um determinado processo determina um OSR mais baixo devido à taxa de clock limitada pelo processo. Para atingir um DR suficiente, é necessária uma modelagem de ruído agressiva implementada por ordem de função de transferência de alto ruído, que é convencionalmente realizada por cascata de filtro de loop e geralmente igual ou maior que 3 em trabalhos anteriores. No entanto, os pedidos de filtro de loop aumentados causam consumo de energia, instabilidade e complexidade de design. A arquitetura de modelagem de ruído de múltiplos estágios (MASH) [6, 8], implementada por local em cascata de ordem inferior Δ Σ moduladores sem caminho de feedback entre si, foram empregados para aliviar problemas de estabilidade, mas com sensibilidade de incompatibilidade. Além disso, um modulador com um quantizador de vários bits obtém um DR condicionalmente alto com uma quantidade de comparador crescente exponencial.

Este artigo descreve um modulador CT em CMOS de 40 nm que atinge 80 DR em 100 MHz BW com consumo de 69,7 mW usando processo CMOS de 40 nm. Este artigo está organizado da seguinte forma. A seção “Método” descreve a topologia do modulador e a implementação do circuito. A seção “Resultados e Discussão” mostra os resultados simulados, e a seção “Conclusão” fornece um resumo deste trabalho.

Método

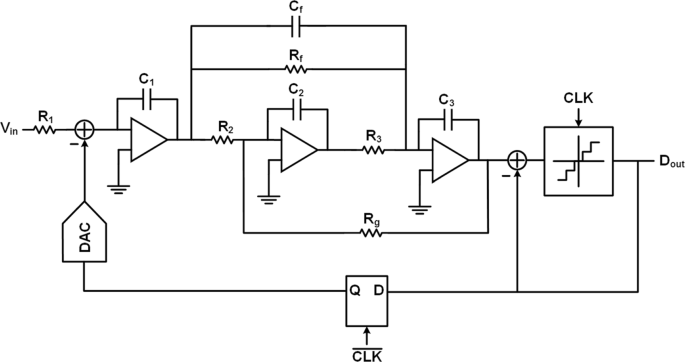

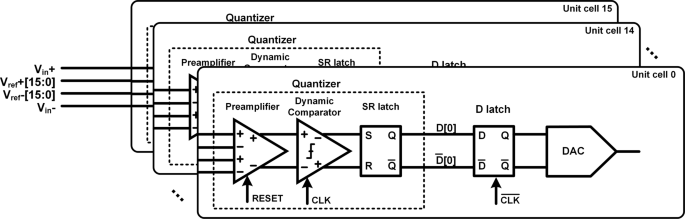

A Figura 1 ilustra o esquema geral do TC de 3ª ordem proposto Δ Σ modulador com a estrutura single-ended para simplificação. A modelagem de ruído de 3ª ordem obtém um grande compromisso entre o DR e a estabilidade do loop. O modulador proposto tem uma taxa de amostragem de 2,4 GHz com 12 OSR. O OSR relativamente alto em Δ Σ moduladores excedidos 100 MHz BW garantem um alto DR. O modulador contém três integradores RC, um quantizador de 4 bits e um DAC direcionador de corrente de 4 bits. Os integradores são implementados por amplificadores feedforward de dissipação de baixa potência inovadores para alta eficiência energética. O DAC de feedback tem um retardo extra de meio período de amostragem para relaxar o requisito de metaestabilidade do quantizador. Um caminho de feedback rápido implementado por um somador passivo e conduzido diretamente pelo quantizador realiza a compensação de excesso de loop-delay (ELD). Uma topologia feedforward é empregada para eficiência de energia em detrimento da função de transferência de sinal fora da banda.

Esquema geral do CT de 4 bits de 3ª ordem de loop único proposto Δ Σ modulador com topologia feedforward

Design do amplificador

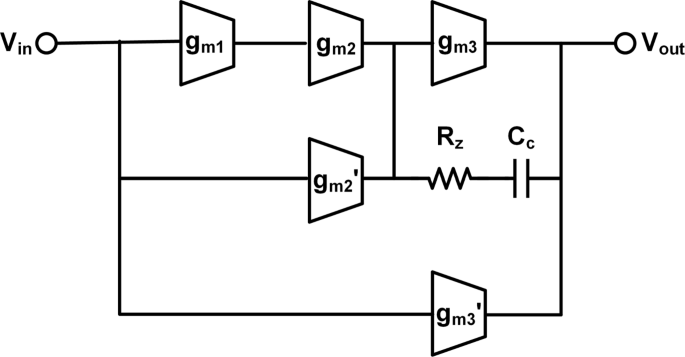

O alto ganho do amplificador é necessário em Δ Σ moduladores para garantir a função de transformação de ruído desejada. No entanto, as tecnologias em nanoescala usadas para atingir a taxa de clock de vários GHz sofrem com o baixo ganho intrínseco. Portanto, um amplificador de três estágios é adotado para implementar ganho DC suficiente, como mostrado na Fig. 2. A topologia feedforward e a compensação de Miller são combinadas para melhorar a margem de fase sem redução da largura de banda do ganho da unidade. Os amplificadores feedforward têm sido uma solução popular para obter alto ganho com UGBW e margem de fase (PM) adequados. Supõe-se que o zero da metade esquerda do plano causado pelo caminho de alimentação cancela efetivamente a mudança de fase negativa dos pólos. Requer alta transcondutância dos amplificadores no caminho de alimentação e consome energia significativa. O esquema vantajoso de reutilizar a corrente de polarização economiza energia enquanto limita g m valores. g insuficiente m normalmente causa o zero além do UGBW e não pode fornecer uma margem de fase adequada. Um zero otimizado localizado abaixo do UGBW geral é fornecido pela adição de um capacitor de compensação Miller e um resistor de anulação.

Topologia do amplificador feedforward de três estágios proposto com compensação Miller

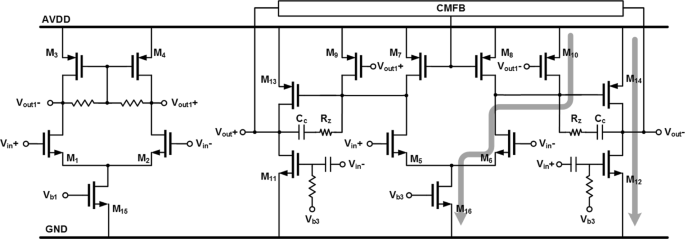

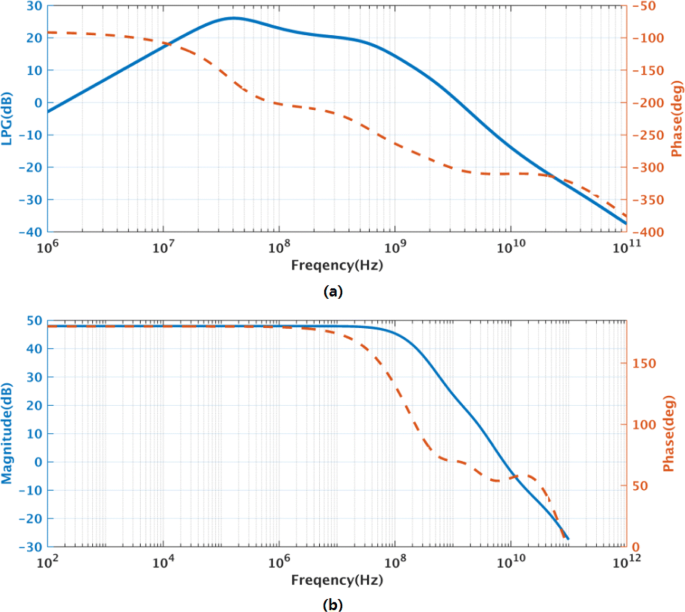

A Figura 3 mostra o esquema em nível de transistor do amplificador usado no primeiro integrador. Transistores M 1-4 formam o estágio de entrada do amplificador, enquanto os transistores M 9,10 e M 13,14 formar o segundo e terceiro estágios, respectivamente. Transistores M 5−8 e M 11,12 crie dois caminhos feedforward de alta velocidade entre a entrada e a saída enquanto compartilha as correntes de polarização com os amplificadores de segundo e terceiro estágios. O modo comum de saída de primeiro estágio (CM) é fixado localmente. O CM de saída de segundo estágio e terceiro estágio é fixado por um caminho de feedback de segundo estágio através de um amplificador CMFB, M 7,8 e M 13,14 . A Figura 4a mostra a resposta de loop aberto pós-layout simulada do amplificador do primeiro integrador com todo o carregamento, enquanto a Fig. 4b mostra a resposta de loop fechado. O primeiro integrador atinge 3,6 GHz de UGBW e 57,8 ∘ de PM com todo o efeito de carregamento enquanto consome 10,5 mW de uma fonte de 1,2 V. O segundo e o terceiro integradores adotam a mesma topologia, mas com correntes de polarização escalonadas, alcançando UGBW de 4,7 e 3,3 GHz e PM de 58,0 e 57,8 ∘ enquanto consome 4,3 e 17,3 mW, respectivamente.

Esquema de amplificador em nível de transistor

O pós-layout simulou os resultados do amplificador no 1º integrador. a Resposta CA em malha aberta; b Resposta CA de circuito fechado

Quantizador e DAC

Conforme o esquema do quantizador e DAC mostrado na Fig. 5, cada um consiste em 16 células unitárias. O quantizador é realizado como um ADCs flash de 4 bits com codificador de 16 níveis gerado a partir de uma escada resistiva de 17 derivações. O quantizador, cuja duração da operação é exigida pelo ELD para menos da metade de um período de amostragem para garantir a estabilidade do loop, é um bloco-chave como uma limitação do BW máximo.

O esquema simplificado dos quantizadores e dos DACs

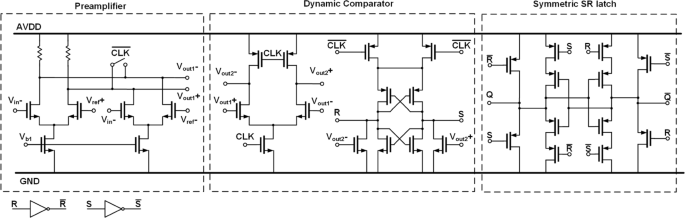

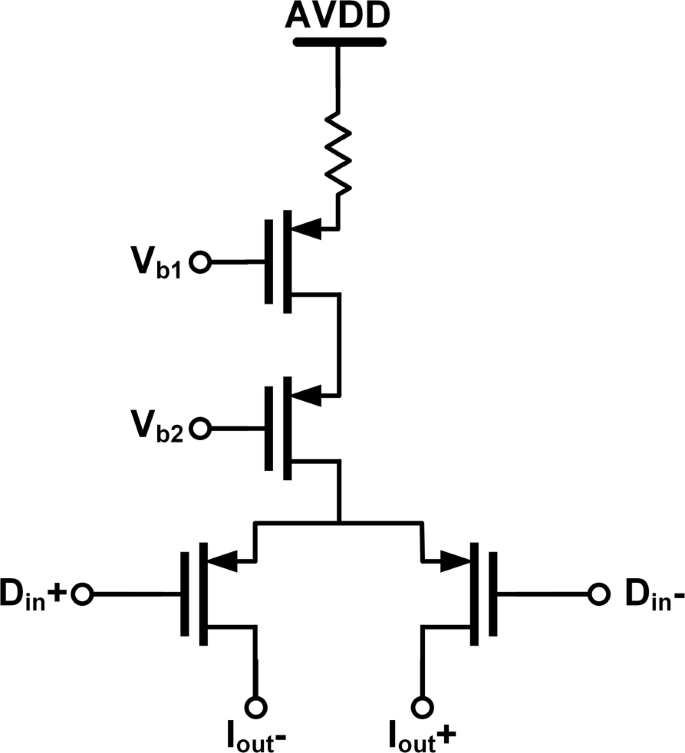

Para implementar ADCs de flash de alta velocidade, uma arquitetura de comparador de três estágios consistindo em um estágio de pré-amplificador, um estágio de comparador dinâmico e uma trava simétrica set-and-reset (SR) [12], ilustrada na Fig. 6, é empregada. O pré-amplificador para a redução de deslocamento referida pela entrada é composto por dois pares diferenciais de carga resistiva com uma chave de reinicialização conectada às saídas para permitir uma recuperação rápida. Ao contrário dos comparadores dinâmicos convencionais, o par diferencial e os inversores de acoplamento cruzado são divididos em duas partes para minimizar a quantidade de transistor em cada caminho de corrente para fontes de baixa tensão. Quando o relógio muda para o nível alto, os comparadores dinâmicos começam a tomar a decisão de comparação dependente de entrada. Em seguida, as duas saídas de cada comparador dinâmico são restauradas para 0 conforme o retorno do relógio vai de alto para baixo, disparando a regeneração e travamento do latch SR simétrico. Visto que apenas um transistor em cada ramificação está ativo, a estrutura de trava SR simétrica leva a uma forte capacidade de condução de carga. Ele permite um transistor pequeno com velocidade de desligamento significativa e baixo consumo de energia. Além disso, resulta em atrasos iguais de ambos os sinais de saída. As travas D antes das unidades DAC são sensíveis ao nível baixo em relação ao nível do sinal de clock, garantindo a metade da duração ELD. O circuito de nível de transistor da unidade DAC de direção de corrente é mostrado na Fig. 7.

Circuito de nível de transistor de um elemento de unidade do quantizador proposto

O elemento da unidade DAC de direção atual do PMOS

Resultados e discussão

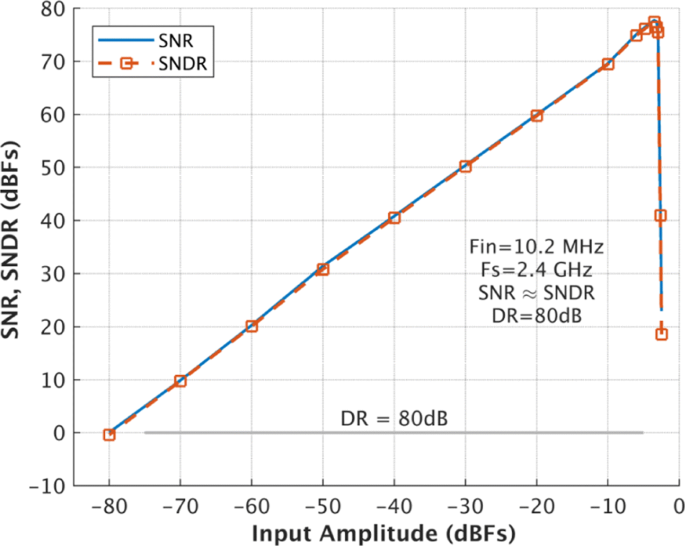

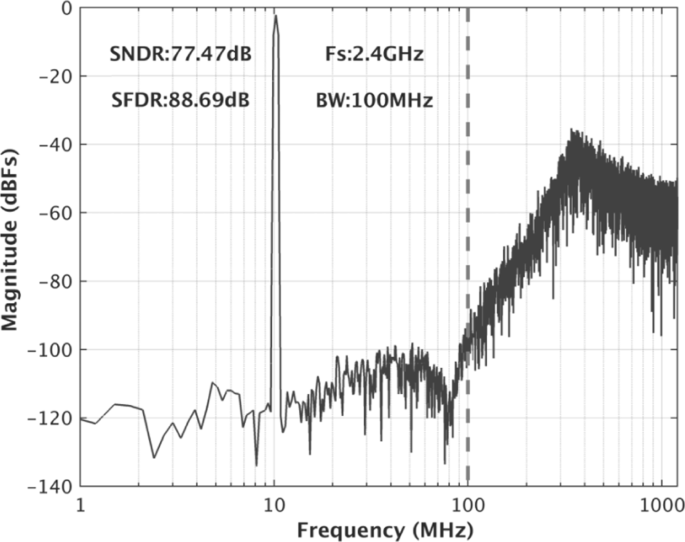

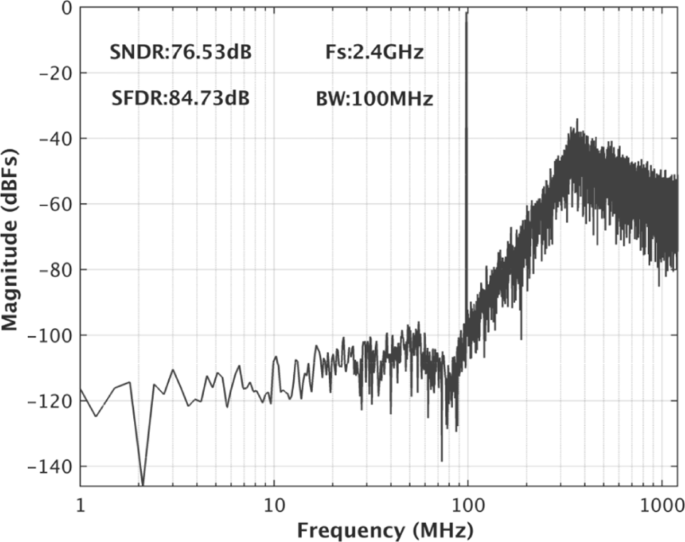

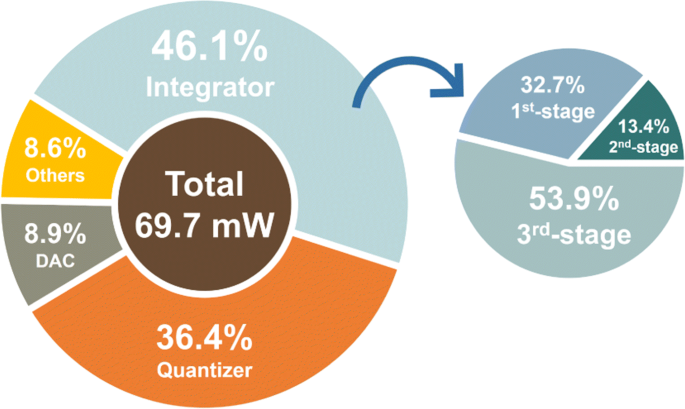

O protótipo Δ Σ modulador é construído em um processo CMOS de 40 nm. Como os resultados pós-simulados do SNR e SDNR vs. amplitude de entrada em 10,2 MHz mostrado na Fig. 8, um DR de 80 dB é alcançado. As Figuras 9 e 10 mostram os espectros simulados com uma entrada de tom único - 3,52-dBF a 10,2 MHz e 97 MHz, respectivamente, uma vez que 0 dBF corresponde ao modulador de escala completa de 2,4 Vpp. O SNDR é 77,47 dB e 76,53 dB, respectivamente. Conforme o breakdown consumo mostrado na Fig. 11, o modulador custa 69,7 mW de consumo de energia. O integrador, o quantizador e o DAC consomem respectivamente 32,1 mW, 25,4 mW e 6,2 mW. A potência de 6,0 mW é consumida por outras correntes, incluindo buffers de clock, polarizações de corrente e referências de tensão. O modulador atinge um Schreier FOM de 171,6 dB com base no DR. A Tabela 1 compara este trabalho com vários trabalhos publicados anteriormente. O modulador proposto atinge BW amplo com o FOM mais alto.

SNR pós-simulado e SNDR vs. amplitude do sinal de entrada com uma entrada de 10,2 MHz

Os espectros pós-simulados com uma entrada de tom único a 10,2 MHz

Os espectros pós-simulados com uma entrada de tom único a 97 MHz

O colapso do consumo de energia pós-simulado

Conclusão

Neste trabalho, propomos um TC de 4 bits de 3ª ordem Δ Σ modulador com uma topologia feedforward de loop único. Este modulador é projetado em um processo CMOS de 40 nm e atinge 80 dB DR em um BW de 100 MHz a uma taxa de clock de 2,4 GHz. A construção do amplificador de dissipação de baixa potência leva a uma alta eficiência energética e o modulador consome 69,7 mw da fonte de alimentação de 1,2 V e atinge um FOM Schreier de 171,6 dB.

Disponibilidade de dados e materiais

Todos os dados gerados ou analisados durante este estudo estão incluídos neste artigo publicado.

Abreviações

- ADC:

-

Conversores analógico para digital

- BW:

-

Largura de banda

- CT:

-

Tempo contínuo

- DR:

-

Gama dinâmica

- DT:

-

Tempo discreto

- ELD:

-

Excesso de atraso de loop

- LTE-A:

-

Evolução de longo prazo avançada

- OSR:

-

Razões de sobreamostragem

- PM:

-

Margem de fase

- UGBW:

-

Largura de banda de ganho de unidade

Nanomateriais

- DIY mais simples relógio IV9 Numitron com Arduino

- Impressão 3D de alta velocidade com AION500MK3

- Controle de Polarização Terahertz Completo com Largura de Banda Ampliada via Metasurfaces Dielétricos

- Fabricação de fossos em nanoescala com alto rendimento em filme fino de polímero usando litografia de aragem dinâmica baseada em ponta de AFM

- RGO e redes de grafeno tridimensionais TIMs co-modificados com alto desempenho

- Aerogel de Grafeno / Polianilina com Superelasticidade e Alta Capacitância como Eletrodo de Supercapacitor Altamente Tolerante à Compressão

- Conversor de polarização com birrefringência controlável baseado em metassuperfície híbrida totalmente dielétrica-grafeno

- Célula solar híbrida de silício orgânico nanoestruturado de alto desempenho com estrutura de superfície modificada

- A resposta fotocorrente extremamente aprimorada em nanofolhas isolantes topológicas com alta condutância

- Dispositivo multifuncional com funções selecionáveis de absorção e conversão de polarização na faixa Terahertz