Ge N-Channel MOSFETs com ZrO2 Dielectric Alcançando Mobilidade Melhorada

Resumo

Ge nMOSFETs de alta mobilidade com ZrO 2 gate dielétrico são demonstrados e comparados com transistores com diferentes propriedades interfaciais de ozônio (O 3 ) tratamento, O 3 pós-tratamento e sem O 3 tratamento. Verifica-se que com O 3 tratamento, os Ge nMOSFETs com ZrO 2 dielétrico com um EOT de 0,83 nm obtém um pico de mobilidade efetiva de elétrons ( μ eff ) de 682 cm 2 / Vs, que é maior do que a mobilidade universal Si na densidade de carga de inversão média ( Q inv ) Por outro lado, o O 3 pós-tratamento com Al 2 O 3 camada interfacial pode fornecer dramaticamente melhorado- μ eff , alcançando cerca de 50% μ eff melhoria em comparação com a mobilidade universal Si em médio Q inv de 5 × 10 12 cm −2 . Estes resultados indicam a utilização potencial de ZrO 2 dielétrico em Ge nMOSFETs de alto desempenho.

Histórico

GERMANIUM (Ge) exibiu vantagens de maior mobilidade de portadores e menor temperatura de processamento em comparação com dispositivos de Si. Isso faz com que Ge seja uma alternativa para aplicações de dispositivos lógicos CMOS ultraescalonados e transistores de filme fino (TFTs) como camada superior em circuitos integrados tridimensionais [1,2,3]. Nos últimos anos, grandes esforços têm sido focados na passivação de superfície, dielétrico de porta e engenharia de canal para transistores de efeito de campo de óxido metálico de canal p Ge (MOSFETs), que contribuíram para uma melhoria significativa no desempenho elétrico para o dispositivos de canal p.

Mas para MOSFETs de canais Ge, baixa mobilidade efetiva da portadora ( μ eff ) causado por uma camada de interface pobre da pilha de portas limita fortemente o desempenho dos dispositivos. Várias técnicas de passivação de superfície, incluindo a passivação de Si [1], pós-oxidação de plasma [4] e passivação de InAlP [5] e vários dielétricos de alto κ, incluindo HfO 2 , ZrO 2 [6,7,8], Y 2 O 3 [9] e La 2 O 3 [10] foram explorados em Ge nMOSFETs para impulsionar o elétron μ eff . Foi demonstrado que ZrO 2 dielétrico integrado com canal Ge pode fornecer uma interface robusta devido a que um GeO 2 camada interfacial pode reagir e se misturar com o ZrO 2 camada [7]. Um buraco decente μ eff foi relatado em transistores de canal p Ge [6,7,8], embora ainda haja muito espaço para melhorias no elétron μ eff para suas contrapartes.

Neste trabalho, Ge nMOSFETs com ZrO 2 os dielétricos da porta são fabricados para alcançar μ melhorados eff sobre Si em toda a gama de densidade de carga de inversão ( Q inv ) Transistores Ge obtêm uma melhoria de 50% no elétron μ eff em comparação com a mobilidade universal Si em um meio Q inv de 5,0 × 10 12 cm −2 .

Experimental

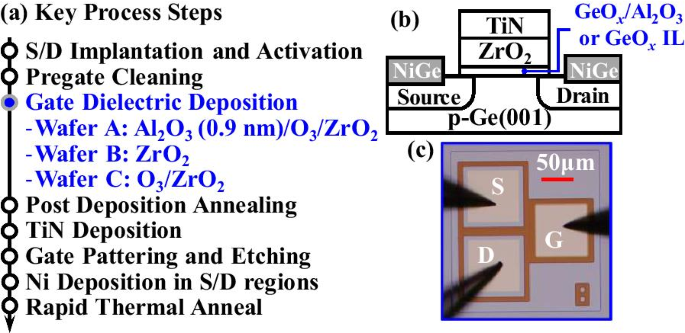

As principais etapas do processo para a fabricação de Ge nMOSFETs em wafers p-Ge (001) de 4 polegadas com resistividade de 0,136–0,182 Ω cm são mostradas na Fig. 1a. As regiões de fonte / drenagem (S / D) foram implantadas com íon fósforo na dose de 1 × 10 15 cm −2 e uma energia de 30 keV seguida por recozimento de ativação dopante a 600 ° C. Após a limpeza do pré-portão, wafers de Ge foram carregados em uma câmara de deposição de camada atômica para a formação da (s) camada (s) dielétrica (s):Al 2 O 3 / O 3 oxidação / ZrO 2 , ZrO 2 , ou O 3 oxidação / ZrO 2 para as bolachas A, B ou C, respectivamente. Para wafer A, 0,9 nm Al 2 O 3 foi usado para proteger a superfície do canal durante O 3 oxidação. O 3 a oxidação foi realizada a 300 ° C por 15 min para ambas as bolachas A e C. Para todas as bolachas, a espessura de ZrO 2 era ~ 3,3 nm. Posteriormente, o metal da porta TiN (100 nm) foi depositado por meio de pulverização reativa física e a padronização litográfica e o ataque de íon reativo foram usados para formar o eletrodo da porta. Depois disso, uma camada de Ni de 25 nm de espessura foi depositada nas regiões S / D. Finalmente, o recozimento pós-metalização (PMA) a 350 ° C por 30 s foi realizado para formar o germanide de Ni e melhorar a qualidade da interface. Imagens esquemáticas e microscópicas do transistor fabricado são mostradas na Fig. 1b, c, respectivamente.

a Principais etapas do processo para a fabricação de Ge nMOSFETs. b Esquemático transversal e c imagem microscópica dos dispositivos fabricados

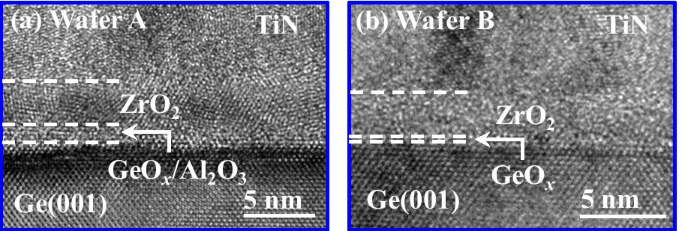

A Figura 2a, b mostra as imagens do microscópio eletrônico de transmissão de alta resolução (HRTEM) das pilhas de portas nas bolachas A e B, respectivamente. A espessura unificada do Al 2 O 3 / GeO x camada interfacial (IL) para o wafer A é de ~ 1,2 nm, indicando o GeO de 0,2–0,3 nm x . Para o dispositivo em wafer B, um GeO ultrafino x IL foi demonstrado experimentalmente [7].

Imagens HRTEM de a TiN // ZrO 2 / Al 2 O 3 / GeO x / Ge, b TiN / ZrO 2 / GeO x / Pilhas Ge para os dispositivos nos wafers A e B, respectivamente

Resultados e discussão

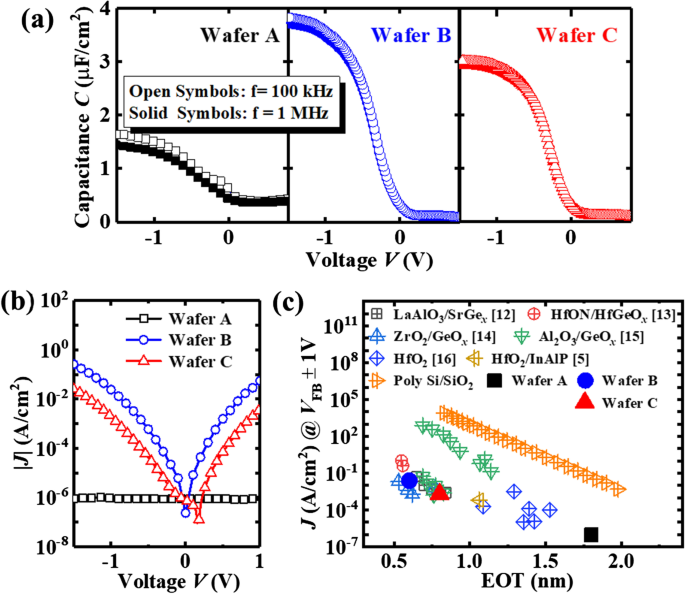

A capacitância medida ( C ) e a corrente de fuga ( J ) características para capacitores Ge MOS nas bolachas A, B e C são medidas e mostradas na Fig. 3a, b, respectivamente. A espessura de óxido equivalente (EOT) dos dispositivos nas bolachas A, B e C é extraída para ser 1,79, 0,59 e 0,83 nm, respectivamente. Assumindo o GeO x IL fornece um EOT extra de ~ 0,25 nm para as bolachas A e C comparando as bolachas B e C, o ZrO de 3,3 nm 2 contribui com um EOT de ~ 0,6 nm com valor κ de ~ 21,8, que é consistente com o valor relatado anteriormente de ZrO amorfo 2 [11]. Esses resultados derivados também confirmam que a espessura em GeO x IL no wafer B é insignificante.

a Medido C em função da tensão V características para capacitores Ge pMOS nos wafers A, B e C. b J versus V curvas para os dispositivos. c Comparativo de mercado de J (extraído em V FB ± 1 V) dos capacitores Ge MOS neste trabalho contra dados obtidos para condições de polarização semelhantes da literatura

O GeO x / Al 2 O 3 IL para wafer A e GeO x IL para wafer C produz o EOT de ~ 1,2 e ~ 0,25 nm, respectivamente. O EOT dos dispositivos pode ser ainda mais reduzido diminuindo a espessura de IL ou melhorando a qualidade da interface e aumentando a permissividade de ZrO 2 com alguma passivação de superfície, por exemplo, NH 3 / H 2 tratamento com plasma [6]. A Figura 3c compara J versus características EOT para os Ge nMOSFETs neste trabalho contra valores para outros dispositivos Ge relatados [5, 12,13,14,15,16,17]. Também é observado que os resultados são consistentes com o Ge MOS relatado com EOT ultrafino seguindo as mesmas tendências, indicando que a diferença de corrente de fuga mostrada na Fig. 3b deve ser atribuída principalmente à diferença de EOT.

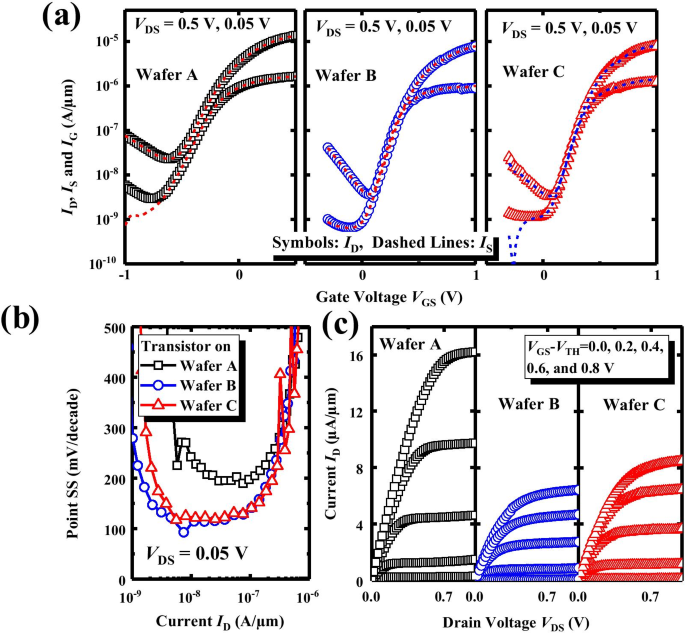

A Figura 4a mostra a corrente de drenagem medida ( I D ) e corrente de origem ( I S ) versus tensão da porta ( V G ) curvas de Ge nMOSFETs dos wafers A, B e C. Todos os transistores têm um comprimento de porta L G de 4 μm e uma largura de portão W de 100 μm. O ponto de oscilação do sublimiar (SS), definido como d V G / d (log I D ), em função de I D curvas para os transistores na Fig. 4a é calculado e mostrado na Fig. 4b. É esclarecido que o transistor no wafer A exibe o degradado I D piso de vazamento e SS em comparação com os dispositivos nas bolachas B e C. Além do aumento na EOT nos dispositivos na bolacha A traria no incremento de SS, este fenômeno deve ser parcialmente atribuído ao fato de que o dispositivo com o Al 2 O 3 camada inserida tem uma densidade maior de armadilhas de interface ( D it ) dentro do bandgap do canal Ge em comparação com os wafers B e C.

a Medido I D e eu S versus V GS curvas de Ge nMOSFETs nas bolachas A, B e C. b Ponto SS como uma função de I D para os transistores. c eu D - V D características mostram que o Ge nMOSFET no wafer A tem uma corrente de acionamento maior em comparação com os dispositivos nos wafers B e C

A Figura 4c mostra as características de saída medidas, ou seja, I D - V D curvas para vários valores de overdrive de portão | V G - V TH | dos dispositivos que demonstram que o transistor Ge no wafer A atinge uma corrente de acionamento significativamente melhorada em comparação com os dispositivos nos wafers B e C. Aqui, V TH é definido como V GS correspondendo a um I D de 10 −7 A / μm. Considerando as condições idênticas para a formação S / D, o impulsionado I DS para transistores no wafer A indica o maior μ eff [18,19,20,21]. O Al 2 O 3 camada não levou à degradação de D it desempenho próximo à banda de condução do canal Ge.

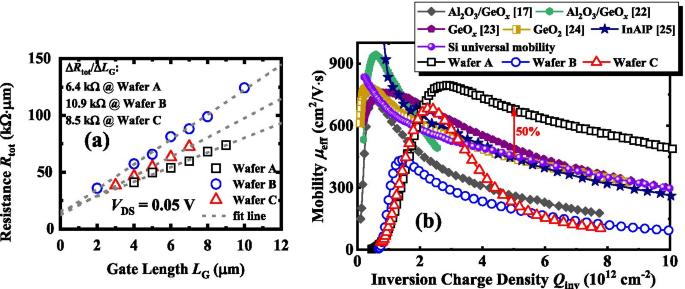

A Figura 5a mostra a resistência total R tot como uma função de L G para os Ge nMOSFETs com ZrO 2 dielétrico com um L G variando de 2 a 10 µm. Os valores de R tot são extraídos em um overdrive de porta de 0. 6 V e um V D de 0,05 V. A resistência S / D R SD dos transistores é extraído para ser ~ 13,5 kΩ μm, utilizando as linhas ajustadas que se cruzam no y -eixo. O semelhante R SD é consistente com o processo idêntico de formação de PMA e S / D. A resistência do canal R CH os valores dos dispositivos são obtidos pela inclinação das linhas ajustadas, ou seja, Δ R tot / Δ L G , que pode ser usado para calcular o μ eff características dos Ge nMOSFETs. Para avaliar a qualidade da interface, as densidades de interceptação da interface ( D it ) foram extraídos pela seguinte equação de acordo com o método de Hill [17]:

$$ D _ {{{\ text {it}}}} =\ frac {{2G _ {{{\ text {m}} \ max}} / \ omega}} {{qA \ left [{\ left ({\ frac {{G _ {{{\ text {mmax}}}}}} {{\ omega C _ {{{\ text {ox}}}}}}} \ right) + \ left ({1 - C _ {{\ text {m}}} / C _ {{{\ text {ox}}}}} \ right) ^ {2}} \ right]}} $$

onde q é a cobrança eletrônica, A é a área do capacitor, G m, máx é o valor máximo da condutância medida, com sua capacitância correspondente C m , ω é a frequência angular e C boi é a capacitância do óxido de porta. O D it os valores são calculados como 3,7, 3,2 e 2,3 × 10 12 eV −1 cm −2 para os dispositivos nos wafers A, B e C, respectivamente.

Sabe-se que os valores calculados correspondem ao midgap D it . O dispositivo com Al 2 O 3 IL no wafer A tem um midgap maior D it em comparação com os dispositivos nas bolachas B e C. Isto é consistente com os resultados nas Figs. 3a e 4a, e o midgap superior D it dá origem a uma maior dispersão da capacitância de depleção na bolacha A, causando uma maior corrente de fuga de I DS em comparação com as outras duas bolachas. Observe que o wafer A deve ter o D inferior it próximo ao bandgap de condução devido ao seu maior μ eff sobre as bolachas B e C.

a R tot versus L G curvas para Ge nMOSFETs nas bolachas A, B e C. A linha ajustada que se cruza no eixo y e a inclinação das linhas de ajuste linear são utilizadas para extrair o R SD e R CH , respectivamente. b μ eff para os Ge nMOSFETs neste trabalho versus resultados publicados anteriormente para transistores Ge não tensionados. Os dispositivos no wafer A mostram o μ melhorado eff do que a mobilidade universal Si em toda a gama de Q inv

É bem sabido que μ eff é o gargalo para alta corrente de acionamento e transcondutância em Ge nMOSFETs. Aqui, μ eff pode ser calculado por \ (\ mu _ {{{\ text {eff}}}} =1 / [WQ _ {{{\ text {inv}}}} (\ Delta R _ {{{\ text {tot}}}} / \ Delta L _ {{\ text {G}}})] \), onde Δ R tot / Δ L G é a inclinação do R tot versus L G como mostrado na Fig. 5a. Q inv pode ser obtido integrando o C medido inv - V G curvas. Na Fig. 5b, comparamos o μ eff versus Q inv dos Ge nMOSFETs nas bolachas A, B e C com aqueles relatados anteriormente em [18, 22,23,24,25]. O pico extraído μ eff os valores dos transistores nas bolachas A e C são 795 e 682 cm 2 / V s, respectivamente, e o de Ge nMOSFETs no wafer B é 433 cm 2 / V s. Ge nMOSFETs com Al 2 O 3 IL consegue uma melhoria significativa de μ eff em comparação com os transistores no wafer B ou C, os dispositivos em [18, 22,23,24,25] em um campo alto e mobilidade universal de Si em todo o Q inv alcance. Em um Q inv de 5 × 10 12 cm −2 , 50% μ eff o aprimoramento é obtido em dispositivos no wafer A em comparação com a mobilidade universal Si. Isso demonstra que, protegendo a superfície do canal para evitar a mistura de ZrO 2 e GeO x usando Al 2 O 3 , uma interface de alta qualidade entre o isolador de porta e Ge é realizada para aumentar as características de mobilidade, o que também é relatado em estudos anteriores de MOSFETs Ge com EOT ultrafino [26]. μ eff em transistores no wafer C é maior do que o Si universal em um Q inv de 2,5 × 10 12 cm −2 , embora decaia rapidamente com o aumento de Q inv alcance. Isso indica que o O 3 usado oxidação antes de ZrO 2 a deposição melhoraria a qualidade interfacial até certo ponto; no entanto, não leva a uma superfície plana de canal suficiente para suprimir efetivamente a dispersão de rugosidade da superfície do portador em alto Q inv devido à mistura de ZrO 2 e GeO x , uma vez que é relatado que a geração de vacâncias de oxigênio durante a mistura aumentaria a rugosidade da ordem de curto alcance (SRO) [27]. Otimizando o O 3 processo de oxidação ou redução do Al 2 O 3 A espessura de IL pode fazer com que o transistor Ge atinja um EOT reduzido, enquanto mantém um μ mais alto eff no alto Q inv .

Conclusões

Os impactos da estrutura dielétrica da porta e morfologia nas características elétricas do Ge nMOSFET são investigados. An Al 2 O 3 / ZrO 2 o dielétrico de porta fornece μ significativamente melhorado eff em comparação com a mobilidade universal Si. μ eff pode ser melhorado inserindo um Al 2 O 3 camada entre o ZrO 2 e o canal Ge, que, no entanto, inevitavelmente leva a um EOT maior. Al 2 O 3 - Ge nMOSFETs grátis com O 3 oxidação da superfície Ge antes de ZrO 2 deposição atingir um pico μ eff de 682 cm 2 / V s que é maior do que o de Si no semelhante Q inv .

Disponibilidade de dados e materiais

Os conjuntos de dados que suportam as conclusões deste artigo estão incluídos no artigo.

Abreviações

- Ge:

-

Germânio

- ZrO 2 :

-

Dióxido de zircônio

- Al 2 O 3 :

-

Óxido de aluminio

- O 3 :

-

Ozônio

- Si:

-

Silício

- PMA:

-

Recozimento pós-metal

- PDA:

-

Recozimento pós-deposição

- IL:

-

Camada interfacial

- TiN:

-

Nitreto de titânio

- MOSFETs:

-

Transistores de efeito de campo de metal-óxido-semicondutor

- ALD:

-

Deposição de camada atômica

- HF:

-

Acido hidrosulfurico

- µ eff :

-

Mobilidade efetiva da operadora

- PPO:

-

Pós-oxidação do plasma

- SS:

-

Balanço de sublimiar

- CET:

-

Espessura equivalente de capacitância

- EOT:

-

Espessura de óxido equivalente

- Qinv:

-

Densidade de carga de inversão

- HRTEM:

-

Microscópio eletrônico de transmissão de alta resolução

- Ni:

-

Níquel

- GeO x :

-

Óxido de germânio

- I DS :

-

Corrente de drenagem

- V GS :

-

Tensão do portão

- V TH :

-

Tensão de limiar

Nanomateriais

- Como Alcançar a Sustentabilidade com Corantes e Pigmentos

- KUHMUTE redesenha mobilidade com impressão 3D SLS

- Controle de Polarização Terahertz Completo com Largura de Banda Ampliada via Metasurfaces Dielétricos

- Memória resistiva ZrO2 / ZrO2 - x / ZrO2 sem conformidade com comportamento de comutação multiestado interfacial controlável

- Mecanismo de condução e resistência aprimorada em RRAM baseado em HfO2 com tratamento de nitridação

- Aprimoramento dielétrico de capacitores de Al2O3 / ZrO2 / Al2O3 MIM depositados na camada atômica por recozimento por micro-ondas

- Ge pMOSFETs de alta mobilidade com passivação de Si amorfo:impacto da orientação da superfície

- 6 maneiras de aprimorar o Protocase Designer com a versão 4.6

- Alcançar um acabamento fenomenal com metalização

- Melhor resistência ao desgaste com eletrodos de cobre de tungstênio