Projeto de PCB e pesquisa sobre cartão de senha de alta velocidade baseado em PCIE

Atualmente, o rápido desenvolvimento da tecnologia da Internet testemunha a aplicação massiva de e-mail, pagamento online e comunicação pessoal. Sob esse pano de fundo, a segurança da informação tem sido um tema crítico de pesquisa em todo o mundo. A tecnologia PKI (Public Key Infrastructure) fornece serviço de segurança usando teoria e tecnologia de chave pública. A tecnologia PCIE (Peripheral Component Interface Express) recebeu amplas aplicações em dispositivos de alta velocidade como o padrão de barramento de E/S de terceira geração que aplica a transmissão de dados seriais e a tecnologia de interconexão ponto a ponto. No campo do projeto de sistema digital, a frequência de clock relativamente alta leva a alguns problemas nas perspectivas de integridade do sinal, integridade de energia e diafonia e o projeto de PCB tradicional não atende aos requisitos de estabilidade do sistema.

Este artigo oferece um esquema de design de PCB em cartão de senha de alta velocidade baseado em PCIE de acordo com os benefícios da transmissão serial de alta velocidade PCIE.

Esquema de design geral

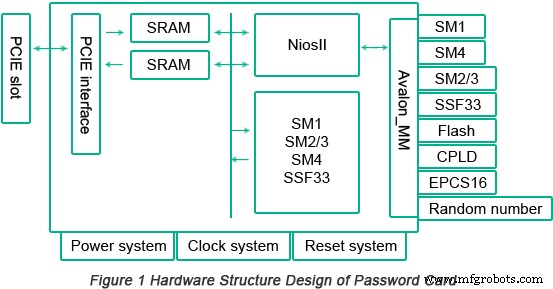

O chip FPGA EP4CGX50CF23C6N pertencente ao Cyclone IV GX projetado pela Altera é aplicado neste design, integrando o módulo PCIE IP hardcore e implementando 4 design de cartão de senha de transmissão de dados de alta velocidade. Quatro tipos de chips, chip 1, chip 2, chip 3 e chip 4, são capazes de implementar respectivamente algoritmos de SM1, SM2/SM3, SM4 e SSF33 e implementar funcionalidades de inicialização de cartão de senha, administração de chave secreta, backup e recuperação e autoridade gestão. Os cartões de senha são aplicados nos PCs, conectados à placa principal nos PCs através do slot PCIE e controlados pelos PCs. O IP hardcore no FPGA é aplicado para implementar o PCIE, levando à comunicação entre o núcleo PCIE e o cache SRAM e o módulo de controle. Como centro de controle, o NiosII implementa a função de software de cartão de senha. Enquanto isso, chip de senha adicional implementa a comunicação entre cada módulo de interface e cartão de senha. O design da estrutura de hardware do cartão de senha é ilustrado na Figura 1 abaixo.

Design de PCB de alta velocidade

• Empilhamento e layout

O design de empilhamento é o problema mais significativo que deve ser levado em consideração e o design de empilhamento razoável pode inibir a radiação EMI (interferência eletromagnética), tornando a tensão transitória no plano de energia ou na camada de terra o menor possível e protegendo o campo eletromagnético de sinal e energia. Geralmente, placas multicamadas e múltiplas potências são aplicadas no projeto de circuitos digitais de alta velocidade. O design de empilhamento de PCB é implementado com base em elementos abrangentes, incluindo frequência de clock do circuito, custo de fabricação de PCB, densidade de pinos, período de fabricação e confiabilidade. Além disso, as camadas de placas multicamadas devem ser mantidas simétricas e o número de placas deve ser um número par, pois o design de empilhamento assimétrico causará empenamento das placas. O cartão de senha projetado neste artigo é conectado ao PC através do slot PCIE e o tamanho e formato da placa de circuito são fixados com altura de aproximadamente 67mm e comprimento de aproximadamente 174mm, configurando o pino de interface PCIE X4 na parte inferior. Como resultado da alta densidade de componentes e do roteamento espesso, o número de camadas de PCB é selecionado como 6 camadas com distribuição de camada de sinal, camada de potência, camada de sinal, camada de potência, camada de solo, camada de sinal. Este projeto contém 3 camadas de sinal, 1 camada de terra e 2 camadas de energia, fornecendo o ambiente exigido pela integridade do sinal.

Após a determinação do empilhamento de PCB, os grupos de componentes e o layout devem ser implementados. Primeiro, a posição dos componentes deve ser programada de acordo com a dimensão e o padrão do PCB, levando em consideração a conexão de linha, o particionamento funcional e o acabamento e a beleza entre os componentes. Então, os componentes devem ser razoavelmente distribuídos de acordo com diferentes graus de tensão do componente para tornar os fios de tensão o mais curtos possível, o que é capaz de reduzir a interferência do ruído de energia e aumentar a estabilidade da energia. A colocação do chip deve prestar atenção à relação entre seu circuito auxiliar e seu chip e à colocação do oscilador de cristal atrás dos pinos do relógio. Componentes de alto ruído devem ser evitados ao redor do oscilador de cristal e devem estar próximos de seus componentes de acionamento. Além disso, a colocação de cada chip de potência e pinos de sinal deve ser considerada com suas posições e direção ajustadas com base nas linhas conectadas. Como a proporção de comprimento e largura do cartão de senha é maior que 2:1 com as posições do slot PCIE, orifícios de carregamento e LED indicador fixos, o layout do componente para componentes fixos deve ser considerado primeiro no layout do componente. Além disso, como resultado do grande número de linhas de conexão entre o componente e o FPGA, o layout do componente deve ser implementado com o FPGA como um centro antes das posições de outros componentes para que a parte superior e inferior do PCB possa ser efetivamente usada para para deixar espaço suficiente entre componentes e componentes e furos de posicionamento.

• Projeto de energia

No projeto da placa de circuito de alta velocidade, o projeto do sistema de energia está diretamente relacionado com o sucesso de todo o sistema. O ruído gerado pela energia e pelo aterramento deve ser reduzido ao mínimo para garantir a confiabilidade dos produtos. A aplicação do esquema de distribuição de energia no método de camadas refere-se ao fato de que a energia é distribuída através do metal em toda a camada, diminuindo a impedância de energia e o ruído e aumentando a confiabilidade. Como as múltiplas potências estão relacionadas ao PCB, o design da camada de várias potências deve ser aplicado, capaz de eliminar a interferência de acoplamento de impedância pública como um loop de ruído. A aplicação de capacitância de desacoplamento é capaz de resolver o problema de integridade de energia, pois o capacitor só pode ser colocado na camada inferior ou na camada superior da PCB, com base em quais fios que conectam os capacitores de desacoplamento devem ser curtos e largos. De acordo com o material do chip, a corrente que passa pelas linhas de energia pode ser calculada e a largura dos fios pode ser determinada. Quanto mais largos forem os cabos, mais corrente eles podem transportar. A fórmula experimental é ilustrada como:W(largura da linha:mm) ≥ L(mm/A) x I(corrente:A)

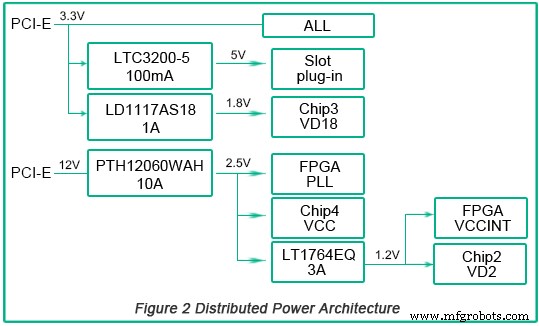

Múltiplas potências no PCB obtêm um ou dois tipos de energia da placa de alimentação usando a placa traseira e a energia é então convertida em outra energia exigida pelos componentes. A conversão de energia é dividida em duas arquiteturas:arquitetura de energia centralizada e arquitetura de energia distribuída. O primeiro refere-se à energia fornecida por uma energia independente e depois convertida em todos os tipos de energia necessária, enquanto o último refere-se à conversão de energia multi-grau. Como a arquitetura de energia centralizada apresenta desvantagens de alto custo e grande área de PCB, a arquitetura de energia distribuída é aplicada neste projeto. O cartão criptográfico diz respeito a 6 potências, incluindo 12V, 3.3V, 5V, 2.5V, 1.2V e 1.8V. Este projeto começa com a participação de 3,3V e 12V de energia no slot PCIE e, em seguida, a energia de 3,3V é capaz de gerar energia de 5V e energia de 1,8V através do chip de conversão de tensão, fornecendo energia para plug-in e chip 3. Em seguida, a energia de 12V é convertida em energia de 2,5V para fornecer energia para FPGA e chip 4. Finalmente, a energia de 2,5V é convertida em energia de 1,2V para fornecer energia para FPGA e chip 2. A arquitetura de energia distribuída da placa criptográfica é mostrada na Figura 2 abaixo.

• Projeto de furo passante

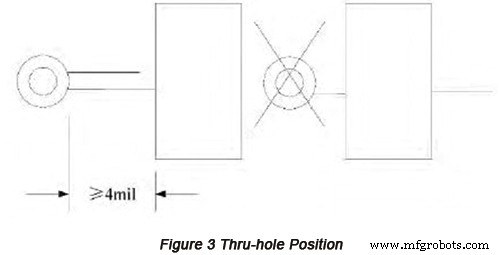

No processo de layout de projeto para PCBs multicamadas com alta densidade, devem ser aplicados furos passantes, transmitindo sinal de uma camada para outra camada para fornecer comunicação elétrica entre as camadas. O design da posição dos furos passantes deve ser implementado com muito cuidado. Furos passantes não devem ser colocados no bloco e uma linha impressa pode ser aplicada para conexão, caso contrário, levando a problemas como lápide e solda insuficiente. A máscara de solda deve ser revestida no bloco de furos passantes com distância definida para ser 4 mil e os furos passantes não devem ser colocados no centro do bloco para componentes de chip no lado da solda. A posição dos orifícios passantes é ilustrada na Figura 3 abaixo.

Além disso, a posição do thru-hole não deve estar muito próxima do goldfinger cujo lado do plug-in deve conter chanfro. Para fazer placas de circuito conectadas no slot PCIE, um chanfro de (1~1,5)x45° pode ser projetado em duas bordas laterais da placa plug-in.

• Roteamento de sinal de alta velocidade

No processo de roteamento, a distribuição deve ser ajustada razoavelmente para tornar as linhas de conexão o mínimo para que a diafonia possa ser reduzida. No processo de roteamento de sinal digital de alta velocidade, a camada de sinal próxima ao roteamento da camada de múltiplas potências deve estar longe da superfície de referência de potência para evitar a geração de caminho de retorno pela corrente do sinal.

Como a frequência do sinal do relógio do circuito de alta velocidade é relativamente alta, o jitter, a deriva e a deformação influenciam muito o sistema, de modo que o projeto de PCB de alta velocidade requer uma pequena interferência de onda de sinal. Portanto, o problema de distribuição de clock e roteamento deve ser considerado em primeiro lugar. O roteamento deve ser implementado em sinais de clock de alta velocidade e o roteamento das linhas de sinal de clock principal deve ser o mais curto possível, reto e livre de thru-holes e partes de energia para evitar a interferência entre clock e energia. Quando vários clocks com diferentes frequências são aplicados no mesmo PCB, duas linhas de clock com diferentes frequências não devem ser mantidas paralelas. No entanto, para vários componentes usando sinais de clock com a mesma frequência, a rede pode ser distribuída por tipo de aranha, tipo de árvore e tipo de ramo.

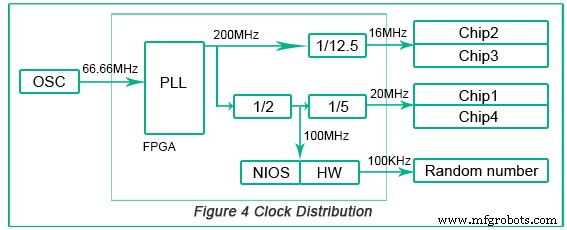

No cartão criptográfico de alta velocidade, o FPGA obtém clock de 66,66 MHz através do oscilador de cristal no PCB. Após o loop com bloqueios intrínsecos dentro do FPGA, o clock básico de 200MHz é gerado como interface para o chip 2 e o chip 3 operarem o clock. Então o clock de 100MHz é fornecido após o circuito de divisão de frequência intrínseca como NiosII softcore e o clock de trabalho do circuito de hardware dentro do FPGA. A frequência dividida de 16 MHz é o clock de trabalho para o chip 2 e o chip 3, enquanto a frequência dividida de 20 MHz é o clock de trabalho para o chip 1 e o chip 4. A distribuição do clock é exibida na Figura 4 abaixo.

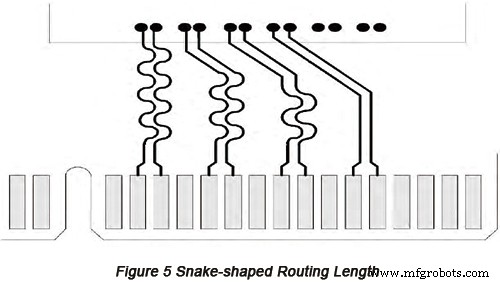

A transmissão de sinal de alta velocidade entre o slot PCIE e o PC é implementada por cartão criptográfico de alta velocidade na forma de roteamento de par diferencial para evitar problemas relacionados à integridade do sinal. De um modo geral, os fios de aterramento não são colocados entre os sinais de pares diferenciais, caso contrário, o efeito de acoplamento entre os sinais de pares diferenciais será destruído. Após o roteamento de sinais de pares diferenciais, o cobre é colocado em torno dos sinais de alta velocidade da placa de circuito impresso com espaço livre totalmente preenchido com fios de aterramento para aumentar a capacidade de EMI do circuito. A chave do roteamento de PCB é manter a simetria dos pares diferenciais. Se o comprimento dos pares diferenciais não for compatível, a precisão da leitura e escrita de dados será afetada com a diminuição da taxa de transmissão de dados. Para garantir a validade da leitura de dados do sistema dentro do mesmo período, a diferença de atraso entre os sinais diferenciais deve ser mantida dentro de uma categoria permitida e o comprimento de roteamento deve ser estritamente o mesmo. Portanto, o roteamento em forma de cobra pode ser aplicado para resolver esse problema ajustando o atraso de tempo. Neste projeto, a comunicação é implementada por PC através de PCIE e cartão criptográfico e a transmissão e recepção de sinais de alta velocidade são implementadas por sinais de pares diferenciais com o comprimento de roteamento PCB controlado dentro de 25mil. O diagrama correspondente do comprimento de roteamento em forma de cobra é ilustrado na Figura 5.

Recursos úteis

• Como projetar PCBs de alta qualidade

• Elementos de design de PCB que influenciam a fabricação de SMT

• Pesquisa sobre design de PCB de alta velocidade em sistemas de aplicativos incorporados

• Processamento isométrico diferencial e Verificação de simulação de projeto de PCB de alta velocidade

• Serviço completo de fabricação de PCB da PCBCart - Várias opções de valor agregado

• Serviço de montagem de PCB avançado da PCBCart - Comece a partir de 1 peça

Tecnologia industrial

- Materiais e design de PCB para alta tensão

- Capacidades de dobra flexível e rígida-flexível no projeto de PCB

- Etapas e processo Aprenda a proteger seu projeto de PCB

- Uma Diretriz do Projeto Esquemático para o PCB Baseado no Altium Designer

- Retrocessos e soluções no projeto de PCB de RF

- 3 técnicas de roteamento no projeto de circuito de sinal de alta velocidade PCB

- Dicas de layout de alta velocidade

- Projeto de dissipação térmica interna do PCB com base no modelo térmico

- Discussão sobre potência e aterramento em compatibilidade eletromagnética de PCB

- Processamento isométrico diferencial e verificação de simulação de projeto de PCB de alta velocidade