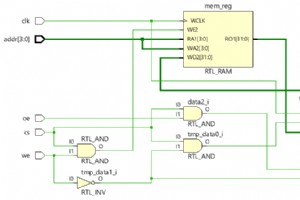

Projeto module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); r

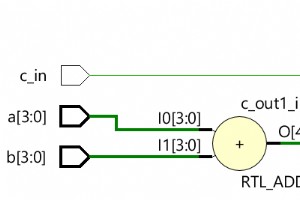

Um somador é um componente digital que realiza a adição de dois números. É o principal componente dentro de uma ALU de um processador e é usado para incrementar endereços, índices de tabela, ponteiros de buffer e em muitos outros lugares onde a adição é necessária. Um somador completo adiciona uma

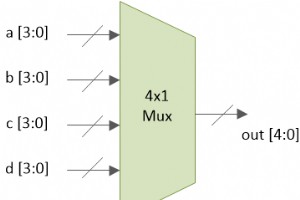

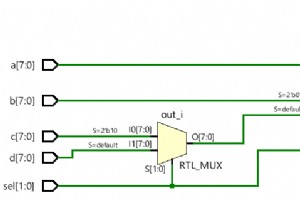

O que é um mux ou multiplexador? Um multiplexador ou mux em suma, é um elemento digital que transfere dados de uma das N entradas para a saída com base no sinal selecionado. O caso mostrado abaixo é quando N é igual a 4. Por exemplo, um multiplexador de 4 bits teria N entradas de 4 bits cada, onde

Projeto module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else

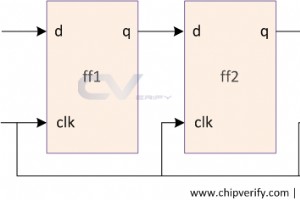

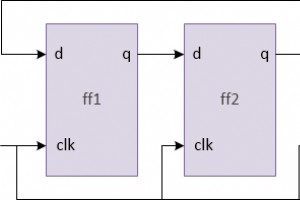

Em eletrônica digital, um registrador de deslocamento é uma cascata de flip-flops onde o pino de saída q de um flop é conectado ao pino de entrada de dados (d) do próximo. Como todos os flops funcionam no mesmo clock, a matriz de bits armazenada no registrador de deslocamento será deslocada em uma p

Projeto module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (int

Projeto module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else o

Projeto module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+

Projeto module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1)

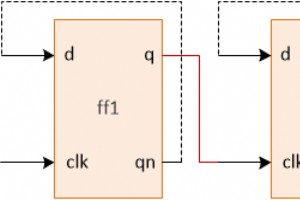

Uma ondulação counter é um contador assíncrono no qual todos os flops, exceto o primeiro, são cronometrados pela saída do flop anterior. Projeto module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (p

O contador de 4 bits começa a aumentar de 4b0000 para 4h1111 e depois volta para 4b0000. Ele continuará contando enquanto estiver equipado com um relógio em execução e a reinicialização for mantida alta. O rollover acontece quando o bit mais significativo da adição final é descartado. Quando o con

Um flip-flop captura dados em sua entrada na borda positiva ou negativa de um clock. O importante a ser observado é que o que quer que aconteça com os dados após a transição do clock até a próxima transição do clock não será refletido na saída. Uma trava por outro lado, não captura na borda de um cl

Projeto module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule Banco de teste module tb; reg clk;

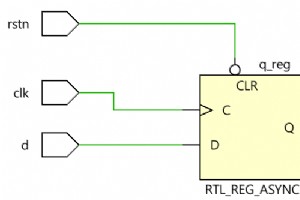

Um D flip-flop é um elemento sequencial que segue o pino de entrada d na borda dada de um relógio. Design nº 1:com reset ativo-baixo assíncrono module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or negedge rstn)

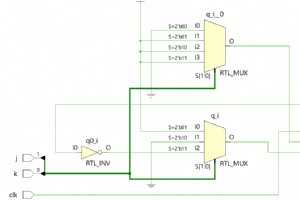

Projeto module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule Es

É sempre melhor começar usando um exemplo muito simples, e nenhum serve melhor ao propósito do que Hello World!. // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital block with some functionality modul

O Verilog possui tarefas e funções do sistema que podem abrir arquivos, gerar valores em arquivos, ler valores de arquivos e carregar em outras variáveis e fechar arquivos. Abrindo e fechando arquivos module tb; // Declare a variable to store the file handler integer fd; initial begin

Prazo padrão Embora se espere que os módulos Verilog tenham uma escala de tempo definida antes do módulo, os simuladores podem inserir uma escala de tempo padrão. A escala de tempo real que é aplicada em qualquer escopo em uma hierarquia elaborada em Verilog pode ser impressa usando a tarefa do sis

A diretiva de escala de tempo Verilog especifica a unidade de tempo e a precisão para simulações. Verilog $timeformat função do sistema especifica %t estilo de relatório do especificador de formato em instruções de exibição como $display e $strobe . Sintaxe $timeformat(<unit_number>, &

As funções matemáticas Verilog podem ser usadas no lugar de expressões constantes e suportam integer e real Matemáticas. Funções matemáticas inteiras A função $clog2 retorna o teto de log2 do argumento dado. Isso normalmente é usado para calcular a largura mínima necessária para endereçar uma mem

Verilog