Estendendo a arquitetura RISC-V com aceleradores específicos de domínio

Quando o mercado de RISC-V começou, a corrida inicial foi para reduzir os custos de projetos que, de outra forma, usariam arquiteturas de conjunto de instruções de CPU (ISAs) proprietárias em aplicativos profundamente incorporados. Quando esses sistemas em chips (SoCs) começaram a ser fabricados na tecnologia de processo de semicondutor FinFET, os custos da máscara ficaram tão caros que muitas máquinas de estado finito foram substituídas por micro sequenciadores programáveis baseados no conjunto de instruções RISC-V. Isso criou o entusiasmo inicial e, posteriormente, a comoditização de núcleos RISC-V simples de 2014 a 2018.

Conforme a arquitetura RISC-V se tornou mais madura e os designers de SoC se familiarizaram com o ISA, ela encontrou adoção em aplicativos em tempo real que exigiam alto desempenho:em particular, servindo como um front-end para motores de aceleração altamente especializados para aplicativos como inteligência artificial . Um dos principais motivos para essa adoção é que o RISC-V é uma arquitetura aberta para os usuários adicionarem instruções, de modo que os processadores RISC-V não precisaram tratar os aceleradores como dispositivos de E / S mapeados em memória, como era o caso das arquiteturas tradicionais . Em vez disso, eles podem usar um coprocessador de baixa latência.

A disponibilidade de processadores RISC-V com extensão vetorial permitiu que aceleradores especializados processassem as camadas entre os loops internos do kernel para aplicativos como inteligência artificial (AI), realidade aumentada / virtual (AR / VR) e visão computacional. Mas isso não é possível sem extensões específicas, como uma instrução de carregamento personalizada para trazer dados de um acelerador externo para os registradores vetoriais internos.

O que impulsiona essa mudança é o modelo de programação exigido por esses aplicativos. O acelerador de propósito especial - que é um grande conjunto de multiplicadores - é altamente eficiente, embora bastante inflexível, tanto nas operações que realiza quanto na movimentação de dados. Compare isso com um processador de uso geral como o x86, que permite ao programador a máxima flexibilidade para programar sem levar em conta as restrições do mecanismo de computação - se apenas o design tiver 100W de potência para queimar, o que a maioria não tem.

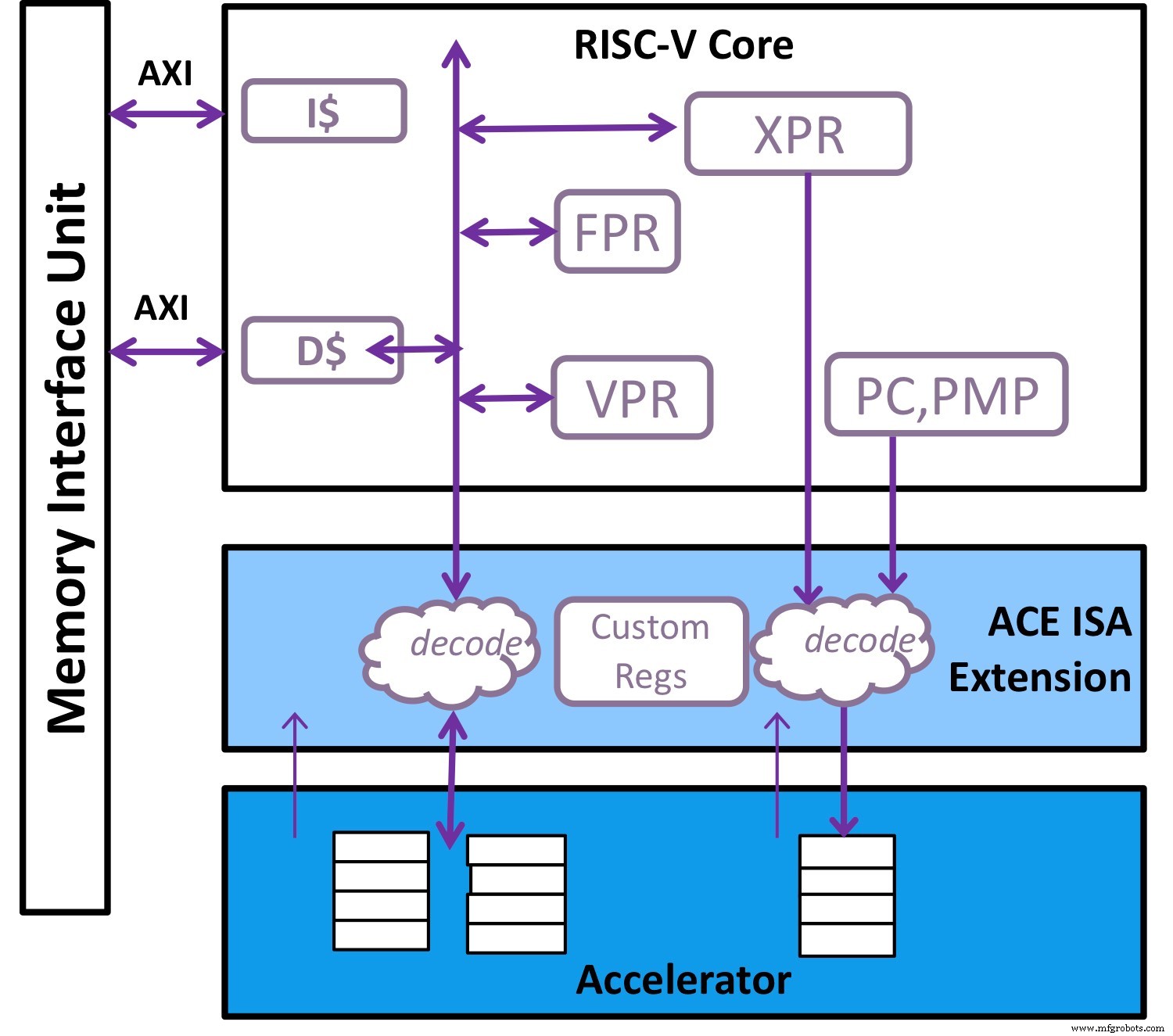

A extensão vetorial padrão em RISC-V aumentada com instruções personalizadas especializadas é um companheiro ideal para o acelerador (Imagem:Tecnologia Andes)

A solução óbvia é combinar a flexibilidade de uma CPU de uso geral com um acelerador que pode lidar com uma tarefa muito específica (veja a figura acima). No RISC-V, a extensão de vetor padrão em amadurecimento aumentada com instruções personalizadas especializadas é um companheiro ideal para o acelerador, e essa adoção tornou-se aparente nos últimos 18 meses à medida que as soluções de aceleração específica de domínio (DSA) convergem para as plataformas RISC-V.

Para tornar essa visão possível, observamos que o acelerador deve ser capaz de executar seu próprio conjunto de comandos usando seus próprios recursos, incluindo memória. Para agilizar a execução do acelerador, o RISC-V também deve ser capaz de nivelar o microcódigo para a largura necessária e empacotar todas as informações de controle necessárias para o acelerador em um comando. Além disso, este conjunto de comandos do acelerador deve estar ciente dos registros escalares e registros vetoriais do processador RISC-V, bem como seus próprios recursos, como arquivos de registro de controle e memória.

Quando o acelerador precisa de ajuda para reordenar ou manipular dados de maneiras especiais, a arquitetura Andes lida com uma unidade de processamento vetorial (VPU) para lidar com o complicado trabalho de permutações de dados - deslocamento, coleta, compactação e expansão. Entre as camadas, existem alguns grãos que envolvem complicações. Aqui, a VPU oferece flexibilidade para ajudar a atender a essa necessidade. Nesses soquetes, o acelerador e o VPU executam uma grande quantidade de cálculos paralelos; portanto, adicionamos hardware para aumentar significativamente a largura de banda do subsistema de memória para corresponder à demanda de computação, incluindo, mas não se limitando a transações de pré-busca e sem bloqueio com retorno fora de ordem.

O primeiro processador de vetor RISC-V da Andes Technology com suporte para a versão 0.8 da extensão V mais recente, o NX27V, executa cada cálculo na unidade de inteiros de 8 bits, 16 bits e 32 bits para pontos flutuantes de 16 bits e 32 bits. Ele também oferece suporte aos formatos Bfloat16 e Int4 para reduzir o armazenamento e transferir largura de banda para valores de peso dos algoritmos de aprendizado de máquina. A especificação do vetor RISC-V é altamente flexível ao permitir que os projetistas configurem os principais parâmetros do projeto, como o comprimento do vetor, o número de bits em cada registro do vetor e a largura do SIMD, o número de bits processados pelo mecanismo do vetor a cada ciclo.

O NX27V tem o comprimento do vetor de até 512 bits e pode ser expandido para 4096 bits pela combinação de até oito registradores de vetor. Com a adição de várias unidades funcionais operando em pipelines paralelos, ele pode sustentar os rendimentos de computação necessários em aplicativos diversificados. Em uma implementação configurada com comprimento de vetor de 512 bits e a mesma largura SIMD, atinge a velocidade de 1 GHz em 7 nm no pior caso de condição dentro de uma área de 0,3 mm

2

. Para suporte ao desenvolvimento de software, além do compilador, do depurador, das bibliotecas vetoriais e do simulador de ciclo, uma ferramenta de visualização do pipeline do NX27V, o Clarity, ajuda a analisar e otimizar o desempenho de loops críticos. Esta solução já começou a ser enviada em nosso programa de acesso antecipado.

Nos últimos 15 meses, vimos uma grande demanda por alto desempenho com a adição de uma poderosa extensão vetorial RISC-V, combinando-a com um subsistema de memória de alta largura de banda e aproximando o acelerador da CPU. Este é o tipo de requisito de computação que acreditamos que irá impulsionar a demanda por RISC-V e processamento vetorial.

>> Este artigo foi publicado originalmente em nosso site irmão, EE Times.

Integrado

- Apresentando o IIC, agora com OpenFog!

- 2ª versão da Arquitetura de Referência Industrial da Internet foi lançada com Layered Databus

- Combatendo incêndios florestais com a IoT

- Alcançando o inacessível com o satélite IoT

- Um guia para acelerar aplicativos com instruções personalizadas RISC-V certas

- Impressão do fusível 1 com o fusível 1

- O que eu faço com os dados ?!

- Computação de borda:A arquitetura do futuro

- Protegendo o vetor de ameaça IoT

- Na estrada com IoT