Projeto de padrão de teste para dano induzido por plasma em dielétrico intermetal em processos FinFET Cu BEOL

Resumo

As interconexões de alta densidade, habilitadas por tecnologias CMOS Cu BEOL avançadas, levam a camadas de metais próximas. Linhas de metal de alta relação de aspecto requerem extensos processos de corrosão de plasma, o que pode causar problemas de confiabilidade em camadas dielétricas intermetálicas (IMD). Este estudo apresenta padrões de teste recentemente propostos para avaliar o efeito do efeito de carga induzido por plasma na integridade do DIM entre linhas de metal próximas. Fortes correlações entre as intensidades de carga de plasma e os danos encontrados nas camadas de IMD são encontradas e analisadas de forma abrangente.

Introdução

Os processos de back-end de linha (BEOL) baseados em Cu têm sido usados extensivamente à medida que as tecnologias migram para o regime de sub-100 nm. As interconexões fortemente compactadas consistem em vias de alta razão de aspecto e linhas de metal que são possíveis por uma série de processos de corrosão intensificados por plasma [1,2,3]. É bem conhecido que os tratamentos de plasma de alta energia podem levar à degradação significativa e danos latentes nas pilhas dielétricas de porta dos transistores, que se acredita ser o principal caminho de descarga durante eventos de carregamento induzidos por processo. Para evitar problemas de confiabilidade na qualidade do dielétrico da porta, os fabricantes de ICs normalmente fornecem regras e diretrizes para projetistas que limitam o tamanho e o comprimento das camadas de metal interconectadas [4, 5]. Com o aumento do número de camadas de metal nos sistemas de fiação complexos, é difícil evitar o caminho de descarga através do filme dielétrico intermetal durante o carregamento induzido pelo processo. Com a introdução de material low-k nos processos BEOL [6, 7], problemas de atraso RC atenuados e os filmes de isolamento podem ser mais suscetíveis a tensões de carga [8, 9]. Os danos resultantes de tensões induzidas por carregamento de plasma em estruturas de interconexão compactas responsáveis por realizar as intrincadas fiações BEOL podem afetar significativamente o rendimento e a confiabilidade de ICs CMOS avançados. Neste estudo, incorporamos os gravadores PID in situ relatados anteriormente [10,11,12], com padrões de teste diferenciais recentemente propostos para monitorar seu possível dano de IMD quando o caminho de descarga adicional se torna possível em processos avançados de Cu BEOL. Os níveis de carga de plasma relatados no gravador em diferentes locais através do wafer podem ser correlacionados com danos de carga de plasma em filmes de IMD por meio dos novos padrões de teste. Comportamentos de falha induzida por estresse nas estruturas do IMD podem então ser facilmente revelados por meio desses padrões de teste, que podem ser usados na estrutura de teste padrão para monitoramento de rotina de novos modos de falha e possíveis problemas de confiabilidade do IMD.

Estrutura e metodologia do dispositivo

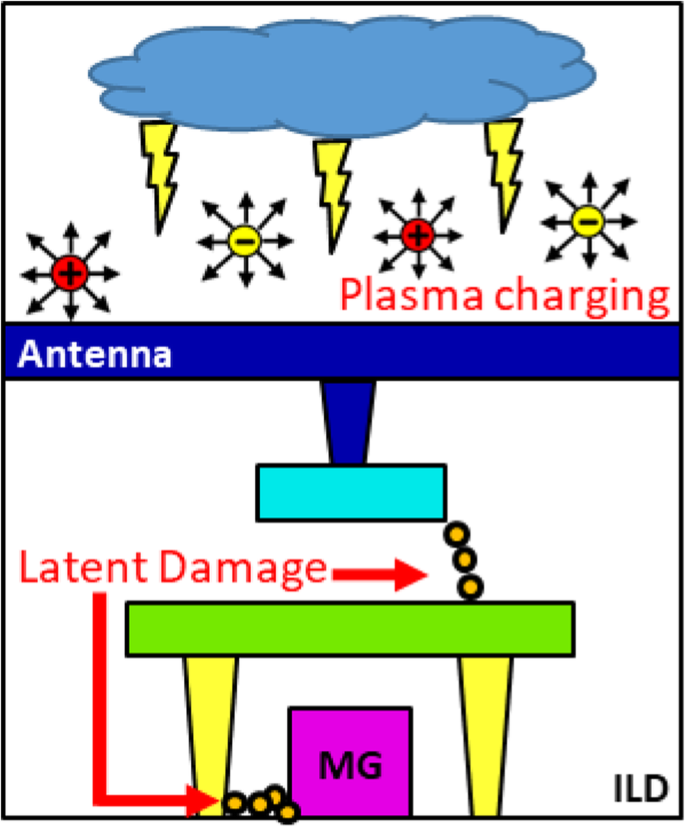

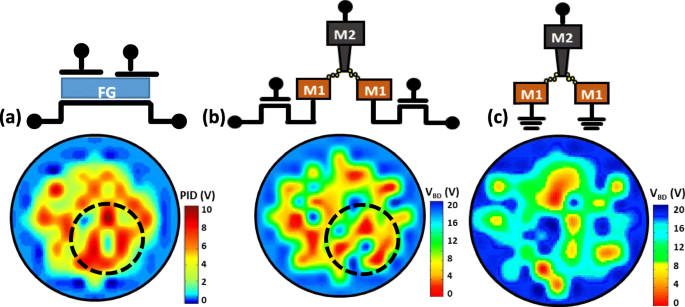

Os resultados da análise de falha em circuitos integrados FinFET sugerem que danos latentes de aumento de estados de armadilha dentro de camadas dielétricas intermetálicas entre duas estruturas de interconexão isoladas próximas podem ocorrer, conforme ilustrado na Fig. 1. Como a largura da linha e o espaçamento entre as interconexões de via e de metal reduzir agressivamente antecipadamente os processos CMOS BEOL, cargas coletadas em grandes fios de metal, servem como antenas, podem descarregar através do IMD através de metais e vias / portas e fios de metal, resultando em tensões de alto campo e / ou alta corrente nesses filmes dielétricos. Ao colocar o gravador PID in situ [10,11,12] ao lado dos dois padrões de teste diferenciais em cada matriz, os níveis de carga de plasma de referência através de um wafer de 12 polegadas podem primeiro ser estabelecidos.

Danos induzidos por plasma em camadas dielétricas intermetálicas entre padrões de interconexão fortemente compactados podem se vincular à degradação latente em sua integridade de isolamento

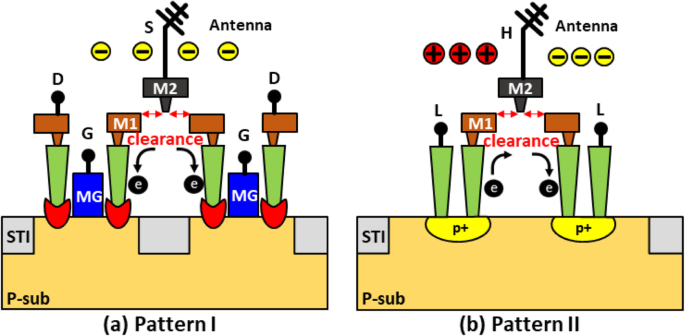

Para garantir que para a corrente de carga de plasma que passa através da camada dielétrica entre as camadas de metal, o nó M2 no padrão de teste na Fig. 2 é isolado antes da construção da estrutura da antena. Dois novos projetos de padrão de teste diferencial com o objetivo de aumentar a possibilidade de causar o dano latente durante as tensões de carregamento de plasma são propostos e ilustrados nas Fig. 2a, b. O dispositivo com padrão tipo I só experimentará alta tensão de corrente quando os elétrons são coletados em sua antena correspondente. Isso ocorre porque a corrente de descarga é retificada pela junção n + / p em série na via condutiva. Já o dispositivo com padrão tipo II está sujeito a tensões I em ambas as direções [13]. Ou seja, o carregamento de íons e o carregamento de elétrons serão registrados neste dispositivo de monitoramento. Consequentemente, as amostras neste estudo são feitas pelo processo padrão FinFET / Cu BEOL em um nó de tecnologia de 16 nm. As estruturas de antena em um gravador PID, bem como os dispositivos com padrões tipo I e II colocados em cada matriz, são todos projetados com uma grande estrutura de metal 3. Ambos os tipos de dispositivos de monitoramento são projetados com configuração diferencial, o que pode acentuar e, posteriormente, minimizar o ruído de desalinhamento que pode levar a leituras de falha nos efeitos do PID.

Ilustrações de padrões de teste diferencial recentemente propostos projetados para acentuar o efeito do dano latente causado por a induzido por plasma negativo e b tensões bidirecionais, onde a folga entre a camada de metal é definida como 14 nm

Resultados experimentais e discussão

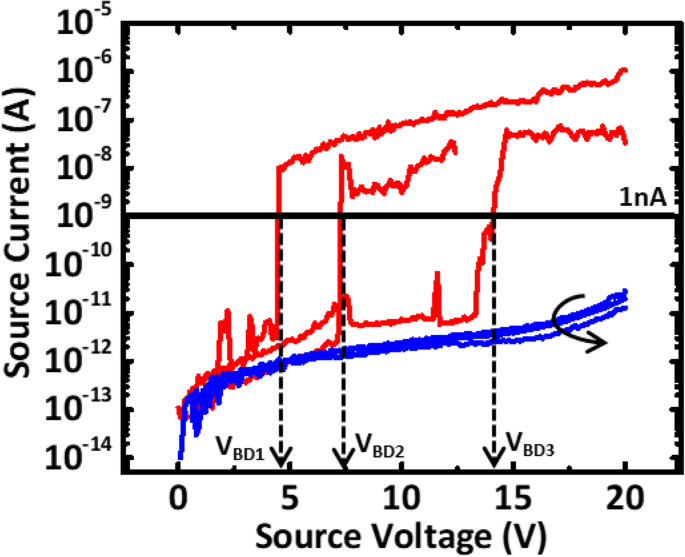

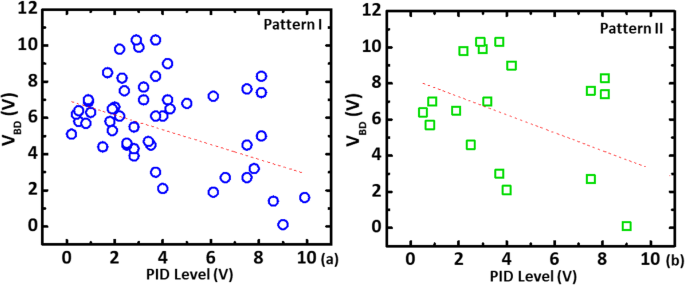

Os dados na Fig. 3 são obtidos aplicando uma varredura de tensão no metal 2 de 0–20 V na taxa de varredura de 0,7 V / seg, enquanto a tensão de ruptura e a corrente de fuga do IMD em ambos os lados de alguns dispositivos diferentes com padrão de teste Posso então ser obtido e comparado. Durante a fabricação da grande antena M3 de 82.000 μm 2 , espera-se que o processo de plasma induza o carregamento da antena. Espera-se que a carga acumulada seja descarregada pelo caminho com a resistência mais baixa. Os dados revelam que algumas amostras apresentam quebra dielétrica precoce, enquanto o IMD em outros dispositivos permanece relativamente intacto com baixo vazamento.

Corrente de fuga medida em dispositivos com padrões de teste diferenciais conectados à antena de metal-3 de 82.000 μm 2 . V BD é definido como a tensão quando a corrente atinge 1 nA para um comprimento de via de 32 nm

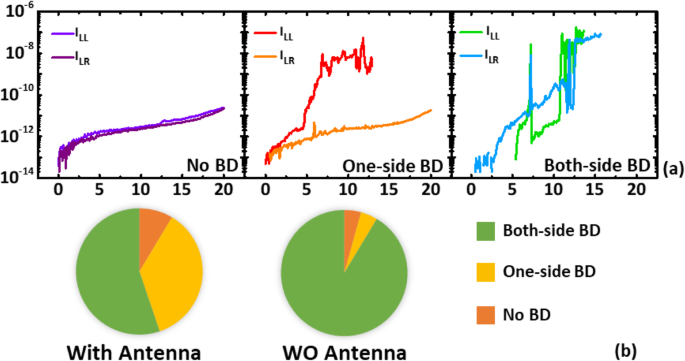

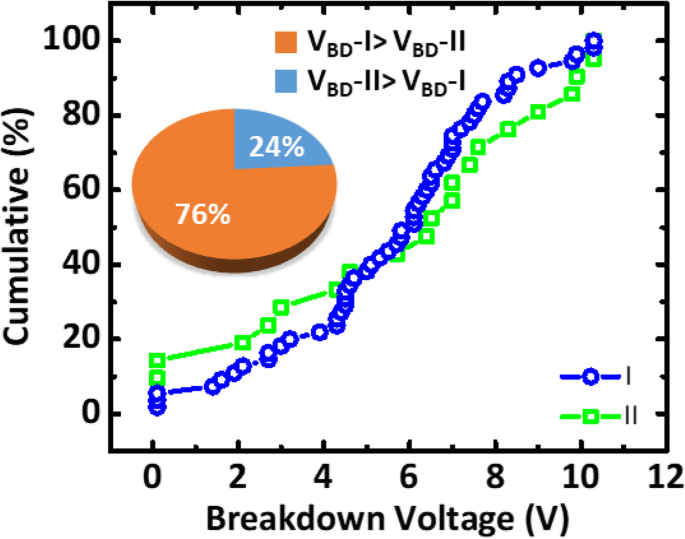

Em um evento de carga, espera-se que o lado mais fraco sirva ao caminho de descarga dominante, levando a um desequilíbrio mais proeminente no nível de danos entre a esquerda e a direita. Portanto, apenas os dispositivos com grande V BD a diferença entre os lados esquerdo e direito é mais provável de ser resultante da carga do plasma. Portanto, quanto menor V BD na divisão do IMD em um par é registrada como o nível correlacionado ao nível de estresse do PID. A Figura 4a mostra três tipos típicos de características que são encontrados em amostras em diferentes matrizes em um wafer. Essas amostras podem ser categorizadas como sem desagregação em qualquer um dos lados, desdobramento de um lado ou grupos de desdobramento de ambos os lados. A porção de dispositivos que mostra as características particulares de cada grupo é mostrada no gráfico de pizza da Fig. 4b. Descobrimos que em amostras sem antena há muito menos alteração de ter características de quebra de um lado. Comportamentos simétricos em ambos os lados são encontrados na maioria dos dispositivos que não experimentaram estresse de carregamento de plasma. Isso sugere ainda que a maioria das características assimétricas em um par diferencial vêm de tensões de carga quando a estrutura da antena está conectada.

a Diferentes tipos de características de decomposição nos pares de teste em um wafer e b comparar a porcentagem de amostras exibindo tipos distintos de características de degradação em pares de dispositivos com mais de 60 matrizes

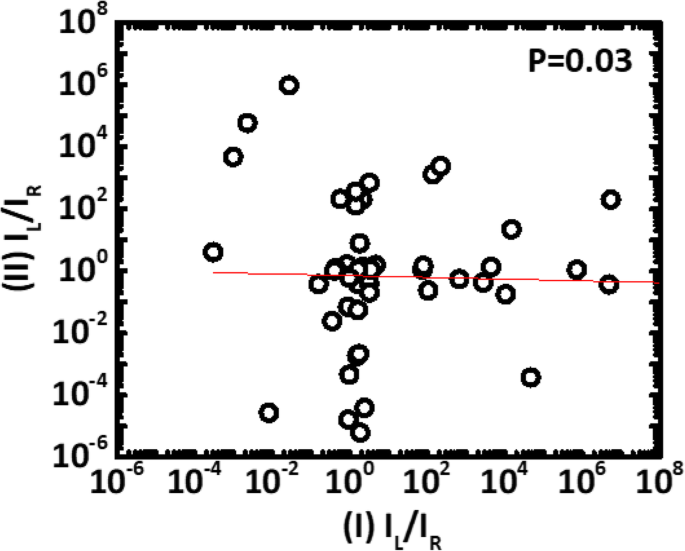

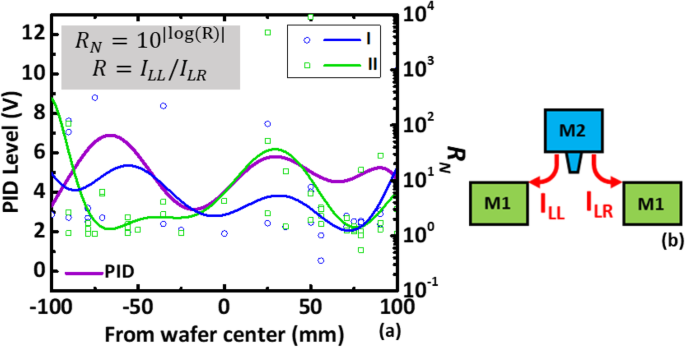

Usando o V BD obtidos pelo método acima, os mapas de wafer do nível PID e V BD de dispositivos de padrões de tipo I e II são comparados na Fig. 5. Alta similaridade entre mapas de wafer do V BD de ambos os tipos de dispositivos de monitoramento e os níveis de carga de referência correspondentes são obtidos do gravador PID, consulte a Fig. 5a. Acredita-se que a tensão do PID registre eventos de carga de elétrons e íons durante processos de metal [14]. No entanto, as amostras em um wafer são consideradas predominantemente sujeitas a mais cargas de elétrons do que de íons [14]. Acreditamos que algum correlacionado regional pode ser visto entre o wafer na Fig. 5a, b. Enquanto o mapa wafer na Fig. 5c do padrão II, sem semelhança óbvia com aquele na Fig. 5a, sugere que a tensão bidirecional [15] pode levar a um efeito secundário nas camadas dielétricas, que precisam de investigação adicional. As tensões de ruptura medidas dos novos padrões de teste vs. os níveis de PID de referência comparados na Fig. 6 revelam ainda que quanto maior o nível de PID em uma matriz, menor será seu V BD os novos padrões de teste. Além disso, correlações negativas significativas entre V BD e os níveis de carga de plasma podem ser estabelecidos. Para investigar o efeito de tensões unidirecionais e bidirecionais nos danos do IMD, V BD medido com base nos padrões do tipo I e tipo II é resumido e comparado na Fig. 7. O V BD a distribuição obtida de dispositivos em 60 matrizes entre wafers indica que os dispositivos que experimentaram tensões de carga bidirecional são mais propensos a mostrar quebra do IMD em uma voltagem mais baixa. Isso pode ser explicado pelo nível de estresse assimétrico conforme a polaridade muda em um IMD [16]. Além disso, a corrente de fuga induzida por estresse (SILC) medida com 10 V através da camada dielétrica é outro indicador para o aumento dos estados de armadilha [17] dentro do filme de IMD. Para minimizar ainda mais o efeito de variação molde a molde causado pela variação do processo, a taxa de vazamento de cada par é usada como o índice para avaliar melhor os danos do IMD. A Figura 8 mostra que essencialmente não há correlação entre a taxa de fuga de corrente nos dois tipos de dispositivos na mesma matriz. Isso quer dizer que o desalinhamento entre as camadas de metal 1 e via2 tem efeitos mínimos em ambos os padrões. Observou a proporção atual, R , definido como I LR / eu LL , é um índice melhor para remover o ruído da variação de molde a molde nesses padrões. Em dispositivos totalmente imparciais, o estresse de carga principal ocorre à direita ou à esquerda, que deve ser completamente aleatório. Aqui, alguns efeitos de polarização são encontrados nas taxas de corrente, onde seu meio de distribuição não está em 1. Para garantir que apenas os resultados dos danos dos efeitos de carregamento do plasma sejam contabilizados, R é a razão de corrente normalizada, conforme descrito na Fig. 9. No gráfico de distribuição no centro da bolacha, R N de dispositivos de padrão tipo I segue com o nível de estresse de plasma de gravadores PID bastante próximo. Por outro lado, R N de dispositivos suscetíveis a estresse bidirecional não podem ser totalmente explicados pelos níveis de PID registrados. Isso pode ser causado por um R significativamente mais alto N nível em dispositivos de padrão II, como resultado de eventos de carga de íons de adição no wafer.

Esquemas e mapas de wafer mostrando as distribuições de ( a ) a tensão PID e VBD de ( b ) padrão de teste I e ( c ) II, mostrando o efeito regional dentro da área circulada de dano induzido por plasma na camada dielétrica de back-end que pode ser atribuído aos níveis de carga de plasma regionais

Correlações entre VBD e níveis de PID para a padrão I e b amostras padrão II, respectivamente [10,11,12]

Comparação da distribuição cumulativa de V BD de 60 matrizes através do wafer e a porção das amostras mostrando tensões de ruptura mais altas do padrão I vs. do padrão II

Taxa de corrente de fuga do lado esquerdo e direito do padrão I e II, mostrando que não há efeito de desalinhamento sistemático dessas amostras

a Razões de corrente normalizadas de amostras de padrão I e II em todo o centro da bolacha em comparação com os níveis PID correspondentes e b a definição de corrente de fuga à esquerda ( I LL ) e certo ( eu LR )

Conclusões

O efeito de carga induzido por plasma na integridade dos filmes de IMD é investigado por meio de padrões de teste diferenciais recentemente propostos em plataformas FinFET Cu BEOL avançadas. Danos na forma de quebra precoce e aumento de SILC nas camadas de IMD estão diretamente correlacionados aos níveis de carga de plasma em wafers de 12 polegadas.

Disponibilidade de dados e materiais

Não aplicável.

Nanomateriais

- Uma introdução à fabricação de metal

- 6 Considerações importantes de projeto para impressão 3D em metal

- Diretrizes de design para manufatura – Parte 1

- 5 dicas para design de chapas metálicas

- 6 dicas para otimizar seu projeto para um projeto de fabricação de metal

- O que é identificação de metal? - Testes e dicas para identificar

- Como otimizar projetos para projetos de fabricação de metal

- Considerações de projeto de impedância para PCB flexível

- Dicas de projeto para dobrar chapas metálicas

- Dicas de design para impressão 3D de sinterização direta de metal a laser