Memória de acesso aleatório resistiva (RRAM):uma visão geral dos materiais, mecanismo de comutação, desempenho, armazenamento de célula multinível (mlc), modelagem e aplicações

Resumo

Neste manuscrito, o progresso recente na área de tecnologia de memória de acesso aleatório resistivo (RRAM), que é considerada uma das tecnologias de memória emergentes mais destacadas devido à sua alta velocidade, baixo custo, densidade de armazenamento aprimorada, aplicações potenciais em vários campos e excelente a escalabilidade é revista de forma abrangente. Em primeiro lugar, é fornecida uma breve visão geral do campo das tecnologias de memória emergentes. As propriedades do material, mecanismo de comutação de resistência e características elétricas de RRAM são discutidos. Além disso, várias questões como resistência, retenção, uniformidade e o efeito da temperatura de operação e ruído telegráfico aleatório (RTN) são elaboradas. É apresentada uma discussão sobre a capacidade de armazenamento de célula multinível (MLC) do RRAM, que é atraente para atingir maior densidade de armazenamento e baixo custo. Diferentes esquemas de operação para obter uma operação confiável do MLC, juntamente com seus mecanismos físicos, foram fornecidos. Além disso, uma descrição elaborada de metodologias de chaveamento e relações de tensão de corrente para vários modelos RRAM populares é abordada neste trabalho. As aplicações prospectivas de RRAM para vários campos, como segurança, computação neuromórfica e sistemas lógicos não voláteis são abordadas brevemente. O presente artigo de revisão termina com a discussão sobre os desafios e perspectivas futuras da RRAM.

Introdução

A memória de acesso aleatório referida como RAM pode ser volátil ou não volátil. Uma memória volátil perde seus dados armazenados anteriores ao remover a fonte de alimentação, como é o caso da memória de acesso aleatório dinâmica (DRAM) e da memória de acesso aleatório estática (SRAM). Para memória não volátil, o conteúdo que foi armazenado anteriormente continuará a ser retido mesmo após a remoção do suprimento. A memória flash é um exemplo típico de memória não volátil. As tecnologias de memória combinam as vantagens e desvantagens para alcançar um desempenho mais alto, por exemplo, As DRAMs empregadas em um sistema de computador têm alta capacidade e densidade, mas são voláteis, o que significa que é necessário atualizar a cada poucos milissegundos. Devido a esta atualização, o consumo de energia do dispositivo aumenta, o que não é desejável. A SRAM, por outro lado, é rápida, mas também é volátil, assim como a DRAM; além disso, as células SRAM são de tamanho maior, o que dificulta sua implementação em grande escala. A memória flash, que consiste essencialmente em um transistor de efeito de campo semicondutor de óxido metálico (MOSFET), além de uma porta flutuante em cada célula de memória, está sendo usada extensivamente, particularmente para as aplicações incorporadas devido ao seu baixo custo e alta densidade . Dependendo de como as células de memória são organizadas, a memória Flash é classificada como Flash NOR e Flash NAND [1]. No NOR Flash, as células são lidas e programadas individualmente à medida que são conectadas em paralelo às linhas de bits. Isso se assemelha à conexão paralela de transistores em uma arquitetura de porta CMOS NOR. Para o caso do NAND Flash, a arquitetura se assemelha à de uma porta CMOS NAND, pois as células são conectadas em série às linhas de bits. Deve-se notar que menos espaço é consumido pela conexão em série em comparação com a paralela, o que resulta em um custo reduzido de NAND Flash. No entanto, ambos os tipos de memórias Flash sofrem de várias desvantagens, como baixa velocidade de operação (tempo de gravação / apagamento:1 ms / 0,1 ms), durabilidade limitada (10 6 ciclos de gravação / exclusão) e alta tensão de gravação (> 10 V) [2].

As tecnologias de memória mencionadas acima, ou seja, DRAM, SRAM e Flash, são memórias baseadas em armazenamento de carga. A DRAM armazena as informações na forma de carga no capacitor, e a SRAM é baseada no armazenamento de carga nos nós dos inversores de acoplamento cruzado, enquanto a tecnologia de memória Flash usa a porta flutuante do transistor para armazenar a carga. Todas essas tecnologias de memória baseadas em armazenamento de carga existentes estão enfrentando desafios para escalar para um nó de 10 nm ou mais. Isso é atribuído à perda de carga armazenada em nanoescala, o que resulta na degradação do desempenho, confiabilidade e margem de ruído. Além disso, os requisitos de grande poder dinâmico de atualização para DRAM e poder de fuga para SRAM e DRAM representam sérios desafios para o design da futura hierarquia de memória.

Portanto, uma nova classe de memórias geralmente referida como tecnologias de memória emergentes está atualmente em desenvolvimento e está sendo ativamente pesquisada principalmente na indústria com o objetivo de revolucionar a hierarquia de memória existente [3]. Essas tecnologias de memória emergentes visam integrar a velocidade de comutação da SRAM, densidade de armazenamento comparável à da DRAM e a não-volatilidade da memória Flash, tornando-se, assim, alternativas muito atraentes para a futura hierarquia de memória.

Para classificar um dispositivo de memória como ideal, ele deve ter as seguintes características:baixa tensão de operação (<1 V), longa resistência ao ciclo (> 10 17 ciclos), tempo de retenção de dados aprimorado (> 10 anos), baixo consumo de energia (fJ / bit) e escalabilidade superior (<10 nm) [4]. No entanto, nenhuma memória única até hoje que satisfaça essas características ideais. Várias tecnologias de memória emergentes estão sendo ativamente investigadas para atender a uma parte dessas características de memória ideais. Essas tecnologias de memória que dependem da mudança de resistência ao invés de carga para armazenar as informações são as seguintes:(i) memória de mudança de fase (PCM), (ii) memória de acesso aleatório magnetorresistiva de torque de transferência de spin (STT-MRAM), e ( iii) memória de acesso aleatório resistiva (RRAM). Na memória de mudança de fase, o meio de comutação consiste em um material calcogeneto (comumente Ge 2 -Sb 2 -Te 5 , GST) [5-7]. O PCM depende da diferença de resistência entre a fase cristalina e a fase amorfa para capacidade de armazenamento de dados eficiente. A fase cristalina denota o estado de baixa resistência (LRS) ou estado ON do dispositivo, enquanto a fase amorfa denota o estado de alta resistência (HRS) ou estado OFF. A operação SET corresponde ao LRS geralmente referido para armazenar o valor lógico '1', enquanto a operação RESET corresponde ao HRS armazenar o valor lógico '0' no dispositivo. Para a operação SET, o PCM é aquecido acima de sua temperatura de cristalização na aplicação do pulso de tensão, enquanto para a operação RESET, uma corrente elétrica maior é passada através da célula e, em seguida, cortada abruptamente de modo a derreter e, em seguida, resfriar o material a fim de atingir o estado amorfo.

Na memória de acesso aleatório magnetorresistiva de torque de transferência de spin, a capacidade de armazenamento é devida à junção de tunelamento magnético (MJT) [8–10], que consiste em duas camadas ferromagnéticas e um dielétrico de tunelamento imprensado entre elas. A direção magnética da camada de referência é fixa, enquanto a aplicação de campo eletromagnético externo pode alterar a direção magnética da camada ferromagnética livre. Se a camada de referência e a camada livre têm a mesma direção de magnetização, o MTJ é referido como no LRS. Para MTJ, por estar no HRS, a direção da magnetização de duas camadas ferromagnéticas é antiparalela. RRAM consiste em uma camada isolante (I) ensanduichada entre os dois eletrodos de metal (M) [11, 12]. RRAM depende da formação e da ruptura de filamentos condutores correspondentes a LRS e HRS, respectivamente, no isolador entre dois eletrodos [13-15].

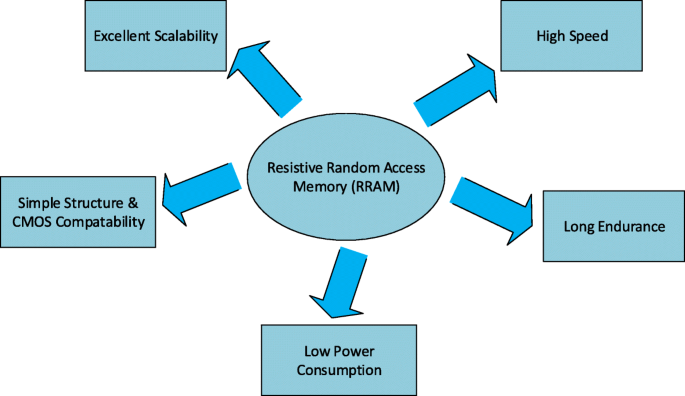

Uma comparação detalhada das tecnologias de memória existentes e emergentes é mostrada na Tabela 1. Como fica evidente na tabela, STT-MRAM e PCM têm vantagens de uma área menor em comparação com a SRAM. Enquanto o STT-MRAM oferece velocidade de gravação / leitura rápida, longa durabilidade e baixa voltagem de programação, por outro lado, o PCM tem a desvantagem de extensa latência de gravação. RRAM tem uma tensão de programação mais baixa e velocidade de gravação / leitura mais rápida em comparação com o Flash e é visto como um substituto potencial da memória Flash. Entre todos os candidatos à tecnologia de memória emergente, RRAM tem vantagens significativas, como fácil fabricação, estrutura simples de metal isolante (MIM), excelente escalabilidade, velocidade de nanossegundos, longa retenção de dados e compatibilidade com a tecnologia CMOS atual, oferecendo assim uma capacidade competitiva solução para a futura memória digital [16]. As vantagens mais significativas do RRAM estão representadas na Fig. 1.

Vantagens do RRAM

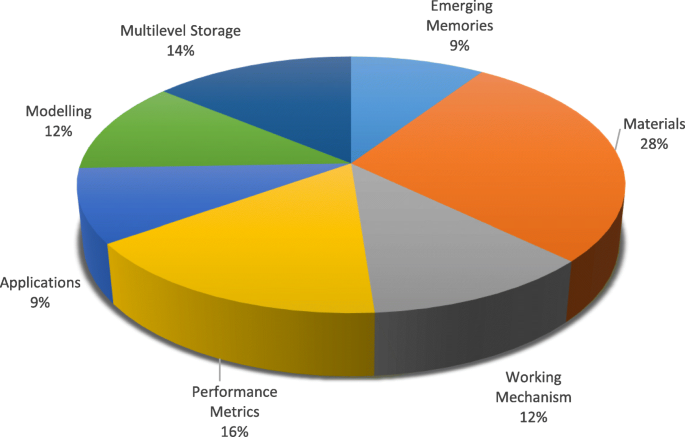

Neste trabalho, o progresso recente e uma visão geral detalhada da tecnologia RRAM são apresentados. Uma revisão dos materiais de comutação junto com a classificação dos modos de comutação e detalhes do mecanismo de comutação é discutida na seção “Memória de acesso aleatório resistiva (RRAM)”. A seção “Métricas de desempenho da memória de acesso aleatório resistiva (RRAM)” destaca várias métricas de desempenho de RRAM. As características da célula multinível (MLC) do RRAM junto com vários esquemas de operação do MLC e seus mecanismos físicos são analisados na seção “Memória de acesso aleatório resistiva multinível (RRAM)”. Uma discussão detalhada sobre a modelagem do dispositivo RRAM é apresentada na seção “Modelagem de Dispositivos RRAM”. Na seção “Aplicações de RRAM”, várias aplicações de RRAM são discutidas. Finalmente, os desafios e perspectivas futuras da RRAM são apresentados na seção “Desafios e Perspectivas Futuras”. A distribuição por categorias dos artigos consultados na preparação deste manuscrito de revisão é apresentada na Fig. 2.

Distribuição por categoria dos artigos consultados para a preparação da revisão no RRAM

Memória de acesso aleatório resistiva (RRAM)

Materiais de comutação de resistência

Observou-se que em alguns isoladores a alteração da resistência ocorre com a aplicação do campo elétrico aplicado. Esta propriedade de mudança de resistência foi recentemente investigada para o desenvolvimento de futuras memórias não voláteis [17]. O fenômeno de troca de resistência foi observado em uma variedade de óxidos, mas os óxidos de metal binários foram extensivamente estudados como um material de comutação preferido para futuras aplicações de memória não volátil principalmente devido à sua compatibilidade com o processamento CMOS BEOL. Vários materiais à base de óxido de metal exibindo a comutação de resistência não volátil, como óxido de háfnio (HfO x ) [18-23], óxido de titânio (TiO x ) [24-31], óxido de tântalo (TaO x ) [32-36], óxido de níquel (NiO) [37-40], óxido de zinco (ZnO) [41-46], titanato de zinco (Zn 2 TiO 4 ) [47], óxido de manganês (MnO x ) [48, 49], óxido de magnésio (MgO) [50], óxido de alumínio (AlO x ) [51-53] e dióxido de zircônio (ZrO 2 ) [54–58] chamaram mais a atenção e foram estudados extensivamente durante os últimos anos. Esses óxidos de metal são depositados geralmente por deposição de laser de pulso (PLD), deposição de camada atômica (ALD) e pulverização catódica reativa. No entanto, ALD é um método amplamente preferido devido à sua capacidade de controlar com precisão a espessura e uniformidade do filme fino [59].

Em dispositivos eletrônicos convencionais, a escolha do material do eletrodo é importante, pois eles atuam como caminhos de transporte para os portadores. Para RRAM, a escolha do material do eletrodo afeta muito o comportamento de comutação do dispositivo. Por exemplo, na estrutura de cobre / poli (3-hexiltiofeno):[6,6] -fenil-C61-butírico éster metílico / óxido de índio-estanho (Cu / P3HT:PCBM / ITO), foi observado um comportamento de comutação resistiva estável; no entanto, ele desapareceu depois que o eletrodo de Cu foi substituído pelo eletrodo de Pt [60]. Uma grande variedade de materiais tem sido utilizada como eletrodos para RRAM. Os materiais do eletrodo podem ser agrupados em cinco categorias com base em sua composição, incluindo eletrodos de substância elementar, eletrodos à base de silício, eletrodos de liga, eletrodos de óxido e eletrodos à base de nitrito. Os eletrodos mais abundantes e comumente usados são eletrodos de substância elementar que incluem Al [51], Ti [49], Cu [30], grafeno [61], nanotubos de carbono [62], Ag [41], W [36], e Pt [44]. Para eletrodos à base de silício, Si tipo p e Si tipo n [63] são os únicos tipos de eletrodos usados. Eletrodos de liga geralmente estabilizam o comportamento de chaveamento resistivo e incluem principalmente Cu-Ti [64], Cu-Te [65] e Pt-Al [66]. Os eletrodos à base de nitreto mais comuns são TiN e TaN [67, 68]. Os eletrodos à base de óxido são relativamente abundantes, incluindo ZnO dopado com Al [69], ZnO dopado com Ga [70] e ITO [71].

A lista de materiais de óxido de metal que foram usados recentemente na fabricação do dispositivo RRAM junto com várias combinações de materiais usados para o eletrodo superior e eletrodo inferior são mostradas na Tabela 2. Uma comparação detalhada dos vários parâmetros também é apresentada. A partir da grande variedade de materiais utilizados, pode-se prever que a troca de resistência não volátil é amplamente observada em vários tipos de óxidos. A escolha do material para a fabricação de RRAM confere-lhe uma vantagem, visto que as estruturas de óxido metálico (MOM) podem ser facilmente fabricadas com o uso de óxidos usados atualmente na tecnologia de semicondutores. O material do eletrodo inferior em RRAM geralmente é platina, que é um pouco difícil de condicionar. Para estrutura de dispositivo único, RRAM pode compartilhar o mesmo eletrodo inferior, enquanto, para a arquitetura de barra transversal, os eletrodos inferiores separados são usados para cada dispositivo. Eles podem ser obtidos por deposição física de vapor e decolagem sucessivamente. O eletrodo superior e a camada de comutação resistiva são depositados usando deposição de camada atômica (ALD) ou deposição física de vapor (PVD).

Modos de comutação de resistência

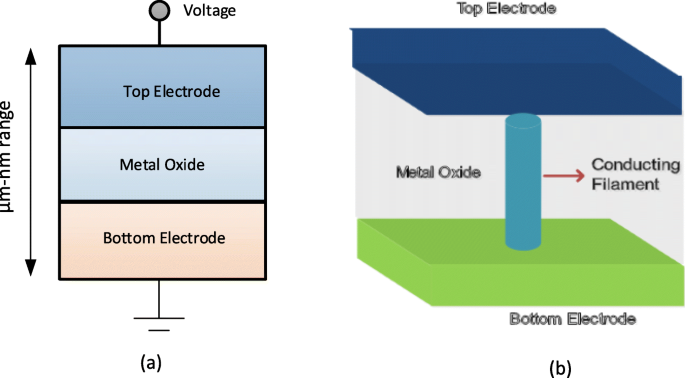

Uma memória de acesso aleatório resistiva (RRAM) consiste em uma célula de memória de comutação resistiva tendo uma estrutura de metal isolante geralmente referida como estrutura MIM. A estrutura compreende uma camada isolante (I) ensanduichada entre os dois eletrodos de metal (M). A vista esquemática e em corte transversal de uma célula RRAM é mostrada na Fig. 3a e b, respectivamente.

a Esquema da estrutura metal-isolante-metal para RRAM. b Vista transversal de RRAM

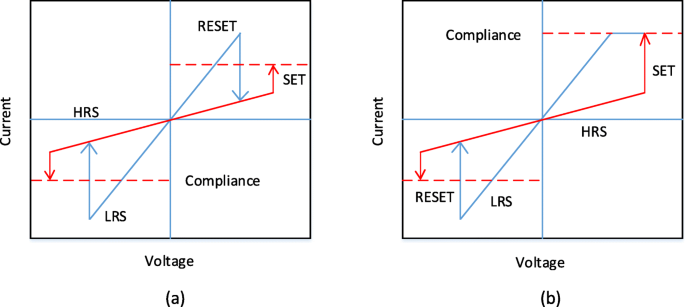

A aplicação do pulso de tensão externa através da célula RRAM permite uma transição do dispositivo de um estado de alta resistência (HRS), ou estado OFF geralmente referido como valor lógico '0' para um estado de baixa resistência (LRS), ou estado ON geralmente referido como valor lógico '1' e vice-versa. O fenômeno de chaveamento resistivo (RS) é considerado a razão por trás dessa mudança nos valores de resistência em uma célula RRAM. Um RRAM preparado está inicialmente no estado de alta resistência (HRS), para alternar o dispositivo do HRS para o LRS, a aplicação do pulso de alta tensão permite a formação de caminhos condutores na camada de comutação e a célula RRAM é comutada em um LRS [72]. Este processo que ocorre devido à quebra suave da estrutura de metal isolante de metal (MIM) é geralmente referido como 'eletroformação' e a voltagem na qual este processo ocorre é referida como voltagem de formação ( V f ) Deve-se notar que a voltagem de formação é considerada dependente da área da célula [73] e da espessura do óxido [74]. Agora, para mudar a célula RRAM de LRS para HRS, o pulso de tensão referido como a tensão de RESET ( V redefinir ) é aplicado, o que permite esta transição de comutação e o processo é referido como o processo de 'RESET' [75-78]. O HRS do RRAM pode ser alterado para LRS na aplicação do pulso de tensão. A tensão na qual ocorre a transição de HRS para LRS é referida como tensão SET ( V conjunto ) e o processo é referido como o processo 'SET' [79]. Para ler dados de forma eficiente da célula RRAM, uma pequena tensão de leitura que não perturbará o estado atual da célula é aplicada para determinar se a célula está no estado lógico 0 (HRS) ou lógico 1 (LRS). Como o LRS e o HRS mantêm seus respectivos valores mesmo após a remoção da tensão aplicada, o RRAM é uma memória não volátil. Dependendo da polaridade da tensão aplicada, o RRAM pode ser classificado em dois tipos de modos de chaveamento:(i) chaveamento unipolar e (ii) chaveamento bipolar [80]. Na comutação unipolar, a comutação (processo de ajuste e reinicialização) do dispositivo entre vários estados de resistência não depende da polaridade da tensão aplicada, ou seja, a comutação pode ocorrer na aplicação de uma tensão de mesma polaridade, mas magnitude diferente, conforme mostrado na Fig. 4a. Na comutação bipolar, por outro lado, a comutação (processo de ajuste e reinicialização) do dispositivo entre vários estados de resistência depende da polaridade da tensão aplicada, ou seja, uma transição de um HRS para LRS ocorre em uma polaridade (positiva ou negativa) e a polaridade oposta muda a célula RRAM de volta para o HRS, conforme ilustrado na Fig. 4b. Na comutação unipolar, o aquecimento Joule é interpretado como o mecanismo físico responsável pela ruptura de um filamento condutor durante a operação de reinicialização. Na comutação bipolar, por outro lado, a migração de espécies carregadas é a principal força motriz para a dissolução do filamento condutor, embora o aquecimento Joule ainda contribua para acelerar a migração. A fim de garantir, não há ruptura permanente da camada de comutação dielétrica durante o processo de formação / configuração de RRAM, uma corrente de conformidade ( I cc ) é obrigatório para o dispositivo RRAM. A conformidade atual ( I cc ) é garantido geralmente por um dispositivo de seleção de células (transistor, diodo, resistor) ou por um analisador de parâmetro de semicondutor durante o teste fora do chip.

Curvas I-V para RRAM. a Troca unipolar e b comutação bipolar [4]

Mecanismo de Comutação Resistiva

A comutação da célula RRAM é baseada no crescimento do filamento condutor (CF) dentro de um dielétrico. O CF é um canal com um diâmetro muito menor da ordem dos nanômetros que conecta os eletrodos superior e inferior da célula de memória. Um estado de baixa resistência (LRS) com alta condutividade é obtido quando o filamento é conectado e a alta resistência (HRS) ocorre quando o filamento é desconectado com uma lacuna entre os eletrodos [91]. Com base na composição do filamento condutor, RRAM pode ser classificado nos seguintes dois tipos:(i) RRAM à base de íons metálicos também referido como memória de acesso aleatório de ponte condutiva (CBRAM) e (ii) vacâncias de oxigênio baseadas em filamento RRAM referido como 'OxRRAM'. Deve-se notar aqui que CBRAM às vezes é referido como a memória de metalização eletroquímica (ECM), enquanto 'OxRRAM' às vezes também é conhecido como memória de alteração de valência (VCM).

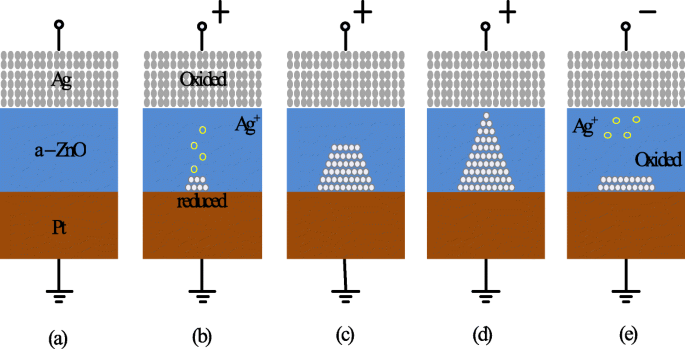

Em RRAM à base de íons de metal, também conhecido como "CBRAM", o mecanismo físico que é responsável pela comutação resistiva é baseado na migração de íons de metal e subsequentes reações de redução / oxidação (redox) [92, 93]. A estrutura CBRAM consiste em um eletrodo superior oxidável (ânodo), tal como Ag, Cu e Ni, um eletrodo inferior relativamente inerte (cátodo), por exemplo, W, Pt e uma camada de óxido de metal intercalada entre os dois eletrodos. A formação de filamentos em tais células de memória ocorre devido à dissolução dos eletrodos metálicos ativos (mais comumente Ag ou Cu), o transporte de cátions (Cu + ou Ag + ), e sua deposição ou redução subsequente no eletrodo de fundo inerte [94]. Assim, o comportamento de chaveamento resistivo deste tipo de RRAM é dominado pela formação e dissolução dos filamentos de metal.

Para obter um melhor entendimento do mecanismo de chaveamento de CBRAM baseado em íons metálicos, vamos considerar um exemplo de células Ag / a-ZnO / Pt RRAM [41]. Uma ilustração esquemática geral que descreve o processo de comutação da célula de memória de acesso aleatório de ponte condutora é mostrada na Fig. 5. O estado original da célula de memória CBRAM é mostrado na Fig. 5a. O eletrodo superior Ag (TE) é um componente ativo na formação do filamento, enquanto o eletrodo Pt inferior é inerte. Na aplicação da polarização de tensão positiva ao eletrodo superior Ag, a oxidação (Ag → Ag + + e - ) ocorre no eletrodo superior por causa do qual Ag + cátions são gerados e são depositados na camada dielétrica (a-ZnO) do eletrodo de Ag. A polarização negativa no eletrodo inferior de Pt (BE) atrai o Ag + cátions e, como tal, a reação de redução (Ag + + e - → Ag) ocorre no eletrodo inferior. Assim, o Ag + cátions são reduzidos a átomos de Ag e se acumulam até que a ponte condutora seja formada (Fig. 5b-d) e o dispositivo RRAM exiba LRS. Este processo é conhecido como 'SET'. Quando a polaridade da voltagem aplicada é invertida, o filamento altamente condutor se dissolve quase completamente e diz-se que o dispositivo está no estado de alta resistência (HRS). Este processo é referido como ‘RESET’ e é representado na Fig. 5e.

Esquema do mecanismo de comutação da ponte condutiva RRAM. a Estado original do dispositivo RRAM. b , c Oxidação de Ag e migração de Ag + cátions para cátodo e sua redução. d O acúmulo de átomos de Ag e eletrodo de Pt leva ao crescimento de filamentos altamente condutores. e A dissolução do filamento ocorre na aplicação de tensão de polaridade oposta [41]

Em RRAM baseado em vacâncias de oxigênio (OxRRAM), o mecanismo físico que é responsável pela comutação resistiva está geralmente associado à geração de vacâncias de oxigênio ( V \ (_ {o} ^ {2 +} \)) e realocação subsequente de íons de oxigênio (O 2− ), permitindo assim a formação de filamento condutor entre os eletrodos superior e inferior da célula RRAM [59]. Inicialmente, para a célula RRAM fabricada, o processo de formação, isto é, a quebra suave do dielétrico é essencial. Uma vez que ocorre a quebra do dielétrico suave, os átomos de oxigênio são eliminados da rede na aplicação de alto campo elétrico em direção à interface do ânodo e se tornam íons de oxigênio (O 2− ) enquanto as vagas de oxigênio ( V \ (_ {o} ^ {2 +} \)) são deixados na camada de óxido. Os íons de oxigênio (O 2− ) reagem com os materiais do ânodo ou são descarregados como oxigênio neutro não reticular, se os metais nobres forem usados como materiais para o ânodo formar uma camada de óxido interfacial. Assim, a interface eletrodo / óxido se comporta como um 'reservatório de oxigênio' [85]. Em seguida, o acúmulo das vagas de oxigênio ( V \ (_ {o} ^ {2 +} \)) no óxido bruto muda a célula RRAM para o estado de baixa resistência (LRS) conforme o filamento condutor (CF) é formado e a corrente apreciável flui no dispositivo. Para mudar o dispositivo de volta para o estado de alta resistência (HRS), o processo de reinicialização ocorre durante o qual os íons de oxigênio (O 2− ) migram de volta para o óxido em massa da interface anódica e combinam-se com as lacunas de oxigênio ( V \ (_ {o} ^ {2 +} \)) ou para oxidar os precipitados de CF metálicos e, assim, romper parcialmente o filamento, voltando assim a célula RRAM para HRS. Para células RRAM exibindo mecanismo de comutação unipolar, a difusão de íons de oxigênio (O 2− ) é ativado termicamente pela corrente de aquecimento Joule e, como tal, os íons de oxigênio se difundem da interface ou da região em torno do CF devido ao gradiente de concentração. Além disso, deve-se notar que uma corrente de reinicialização relativamente mais alta é necessária na RRAM de comutação unipolar para aumentar a temperatura local em torno de CF. No RRAM de comutação bipolar, por outro lado, os íons de oxigênio (O 2− ) precisa ser auxiliado pelo campo elétrico reverso, pois a camada interfacial pode apresentar uma barreira de difusão significativa e a difusão térmica pura não é suficiente. Deve-se observar que a ruptura parcial do CF ocorre em ambos os casos, colocando a célula RRAM no estado de alta resistência (HRS). Isso se deve principalmente à formação de vagas de oxigênio ( V \ (_ {o} ^ {2 +} \)) e região pobre resultando no gap de tunelamento para elétrons. Para mudar o dispositivo de volta para o LRS (processo SET), o CF reconecta os eletrodos como resultado da quebra suave na região da lacuna. Um processo de configuração / reinicialização semelhante pode se repetir por muitos ciclos.

Com base na discussão acima, o CBRAM também conhecido como memória de metalização eletroquímica (ECM) depende de um eletrodo de metal eletroquimicamente ativo como Ag, Cu ou Ni para formar CF baseado em cátions de metal [95]. O CF em vacâncias de oxigênio com base em filamento RRAM ‘OxRRAM’, também conhecido como memória de alteração de valência (VCM), é composto de defeitos de vacância de oxigênio, em vez de átomos de metal, devido à migração de ânions dentro do próprio material de armazenamento [96]. Embora o mecanismo de comutação de 'OxRRAM' e 'CBRAM' seja discutido em detalhes, ainda há algum debate sobre os mecanismos de comutação de ambos os tipos RRAM [97]. Por exemplo, onde o CF começa a crescer no processo de definição e onde interromper o processo de reinicialização e como essas lacunas de oxigênio / átomos de metal se reúnem para formar o CF. As características de corrente-tensão (I-V) de 20 ciclos de comutação consecutivos de Ta / TaO x A estrutura RRAM baseada em / Pt [98] foi investigada e a variação clara de ambos LRS e HRS para ciclos de comutação consecutivos foi observada. Como resultado, a janela geral da memória diminui, degradando o desempenho geral do RRAM. Esta variabilidade de resistência ciclo a ciclo é atribuída principalmente à formação aleatória de CF, bem como sua ruptura durante a operação de configuração e reinicialização, respectivamente.

Uma comparação de OxRRAM com CBRAM com base em vários parâmetros operacionais é mostrada na Tabela 3 [81, 84, 86–88, 99, 100]. Esta comparação revela a notável diferença em termos das características de resistência desses tipos de memória RRAM. Essa dissimilaridade ocorre porque os filamentos condutores de CBRAM são compostos principalmente de átomos de metal que são relativamente mais fáceis de derivar e difundir em comparação com as vacâncias de oxigênio, causando assim a degradação das características de tempo de retenção e resistência do CBRAM em comparação com o OxRRAM. Embora o mecanismo de comutação de ambos os tipos de RRAM sejam diferentes, há muitas características comuns entre os dois. A única diferença significativa é que a resistência para OxRRAM é significativamente maior do que para CBRAM.

Métricas de desempenho de memória de acesso aleatório resistiva (RRAM)

Resistência

A memória de acesso aleatório resistiva envolve transições frequentes entre um estado de alta resistência (HRS) e um estado de baixa resistência (LRS). Cada evento de comutação entre os estados resistivos pode introduzir danos permanentes e causar degradação do desempenho RRAM. A resistência é, portanto, definida como o número de vezes que um dispositivo RRAM pode ser alternado entre o HRS e o LRS, garantindo uma relação confiável distinguível entre eles [101]. Assim, um teste de resistência determina o número máximo de ciclos de ajuste / reinicialização que podem ser comutados efetivamente antes que o HRS e o LRS não sejam mais distinguíveis. As características de resistência de RRAM são obtidas realizando uma sequência de varreduras I-V em uma célula de comutação resistiva e a subsequente extração de R HRS e R LRS na aplicação de uma tensão lida (normalmente 0,1 V) [41]. Este método é confiável, pois é possível obter a correta chaveamento do dispositivo a cada ciclo; entretanto, este método é muito lento porque o tempo necessário para obter uma varredura I-V pode ser muito maior, particularmente se as correntes mais baixas estiverem envolvidas.

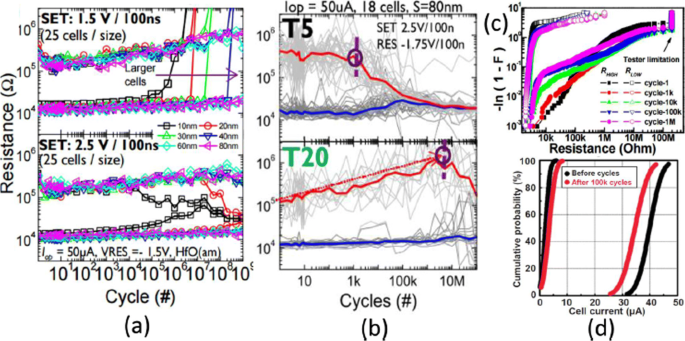

Os ciclos de resistência em um H f O x A célula RRAM mostra uma forte dependência do tamanho da célula, como é representado na Fig. 6a, em que melhor resistência no dispositivo RRAM com tamanho de célula maior é relatada. Além disso, a redução vertical da espessura da camada resulta na degradação do desempenho de resistência para a tensão SET em 2,5 V, conforme mostrado na Fig. 6b [102]. Essa degradação no desempenho de resistência com redução da escala da camada de comutação é resultado do número reduzido de íons na região ativa. H f O x RRAM baseado em apresenta um excelente desempenho de resistência de 10 6 ciclos em uma matriz de 1 kb com tamanho de célula de 30 nm abaixo de 0,18 μ tecnologia m e o mesmo é mostrado na Fig. 6c [103]. Adicionando uma camada extra de A l O x acima do eletrodo inferior (BE), a estabilidade da matriz pode ser melhorada ainda mais conforme a imunidade à perturbação de leitura para HRS é aumentada. Para T a O x baseado em RRAM, uma degradação no desempenho de resistência com o aumento da largura de pulso e amplitude da tensão de RESET foi observada em Ta / Ta 2 O 5 / Estrutura TiN RRAM [105]. Uma comparação do eletrodo inferior TiN e Ru no Ta / Ta 2 O 5 / TiN RRAM mostra que a principal causa da degradação da resistência é devido à reação dos íons de oxigênio com o eletrodo TiN. Além disso, uma resistência aprimorada de 10 9 ciclos de comutação foram obtidos sem verificação em uma estrutura RRAM semelhante, reduzindo o Ta 2 O 5 camada até 3 nm [106] e uso de pulso triangular com largura <5 ns. Para desempenho de matriz em grande escala, uma comparação de Ta 2 de 2 Mb O 5 memória antes e depois de 10 5 ciclos de teste de resistência são mostrados na Fig. 6d [104]. As distribuições de corrente da célula mostram uma pequena variação para os ciclos inicial e final. Além disso, a corrente da célula para LRS cai abaixo de 50 μ A, indicando baixo consumo de energia do array. Os dispositivos de chaveamento resistivo com resistência superior a 10 12 ciclos foram relatados em diferentes tipos de células RRAM envolvendo óxido de tântalo (TaO x ) meios de comutação baseados em [32, 36, 59]. Assim, os dispositivos RRAM baseados em óxido de tântalo parecem estar exibindo a maior resistência.

a Ciclos de resistência de H f O x baseado em RRAM em diferente tensão SET e tamanho de célula b com espessura diferente (T5 =2 nm, T20 =10 nm) em 2,5 V de tensão definida. c Distribuição de resistência de matriz de 1 kb obtida a partir de gráficos de Weibull em diferentes ciclos de resistência. d 100 k ciclos de resistência de 2 Mb-Ta 2 O 5 -based array; Reimpresso de refs [102–104]

Retenção

A retenção de dados de um dispositivo RRAM envolve a investigação da estabilidade ao longo de um período de tempo para o LRS e o HRS após passar por transições de configuração e reinicialização. Em outras palavras, o período de tempo durante o qual uma célula de memória permanecerá em um determinado estado após a operação set / reset determina a capacidade de uma célula de memória reter seu conteúdo [11]. A aplicação do estresse de tensão constante (CVS) ao longo do tempo usando uma tensão de leitura baixa (0,1 V) e a medição da curva de corrente versus tempo (I-t) para ambos LRS e HRS permite a medição de retenção de estado. Devido à natureza de dispersão dos rearranjos atômicos induzidos em RRAM por causa da tensão definida, o longo tempo de retenção em LRS é difícil de obter, ao passo que, em HRS, a retenção não é uma preocupação, pois geralmente é o estado natural do dispositivo e RRAM continuará permanecer neste estado se nenhuma polarização (ou polarização baixa) for aplicada. A retenção no LRS depende do limite de conformidade durante a transição SET, por ex. em RRAMs com base no mecanismo de comutação de filamento condutivo, a maior corrente de conformidade produz um filamento condutor mais forte que é mais estável ao longo do tempo [28, 41], em comparação com uma menor corrente de conformidade. Uma durabilidade projetada de 10 anos em 85 ∘ C foi demonstrado em Ti / HfO 2 / TiN [18]. Um método comumente usado para obter resistência do dispositivo é aplicando pulso de leitura em alta temperatura após certos intervalos de tempo (por exemplo, a cada 1 s) e extrapolar a resistência para um período de 10 anos. Embora este método seja fácil de implementar, ele tem certas limitações principalmente devido ao estresse de tensão de leitura aplicado à célula. Um método alternativo é alterar a temperatura e registrar o tempo até o dispositivo falhar. A energia de ativação é extraída traçando o gráfico de Arrhenius e extrapolando para a temperatura de operação. No entanto, a limitação desse método é que é necessário esperar até que a falha ocorra na célula RRAM e, portanto, esse método é mais demorado e caro.

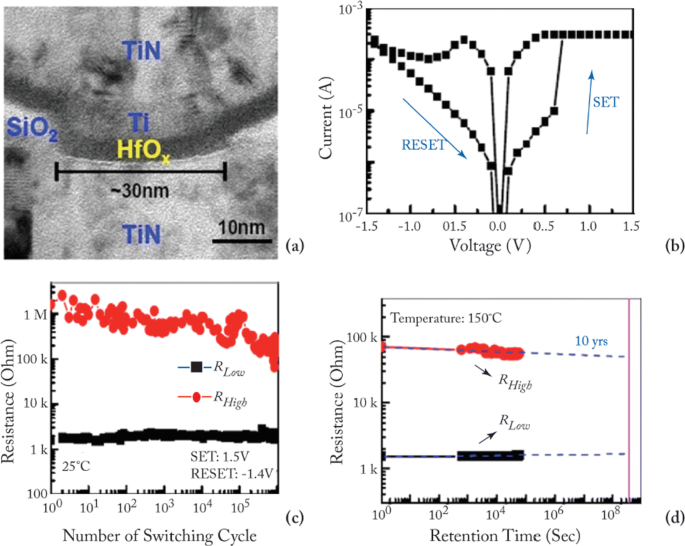

As características do dispositivo de H f O x baseado em RRAM [81, 103] desenvolvido no Instituto de Pesquisa de Tecnologia Industrial, Taiwan, é demonstrado que compreende melhor o funcionamento do dispositivo RRAM. A imagem de microscopia eletrônica de transmissão (TEM) do TiN / Ti / H f O x / TiN dispositivo RRAM com tamanho de célula de 30 nm é mostrado na Fig. 7a. O dispositivo exibe características de comutação bipolar e a curva I-V obtida em 200 μ Um conjunto de corrente de conformidade é mostrado na Fig. 7b. O dispositivo apresenta resistência de 10 6 ciclos de comutação com relação de resistência liga / desliga maior que 100 nas condições de programação definir / redefinir de + 1,5 V / - 1,4 V pulso com 500 μ s largura de pulso e o mesmo é representado na Fig. 7c.

a Imagem de microscopia eletrônica de transmissão (TEM) de TiN / Ti / HfO x / Dispositivo TiN RRAM. b Características típicas de corrente-tensão (I-V) do dispositivo com tamanho de célula de 30 nm. c 10 6 ciclos de comutação de resistência obtidos a partir de 500 μ pulso s. d Espera-se uma vida de retenção de 10 anos testando em 150 ∘ C; reproduzido a partir de refs. [81, 103]

Uniformidade

Na célula RRAM, a baixa uniformidade de várias características do dispositivo é um dos fatores significativos que limitam a fabricação em uma escala mais ampla. As tensões de chaveamento, assim como as resistências HRS e LRS, estão entre os parâmetros que apresentam um alto grau de variação. As variações da troca de resistência incluem flutuações temporais (ciclo a ciclo) e flutuações espaciais (dispositivo a dispositivo). Acredita-se que a natureza estocástica da formação e ruptura do filamento condutor seja a principal razão para essas variações. A variabilidade ciclo a ciclo e dispositivo a dispositivo é um grande obstáculo para o armazenamento de informações em dispositivos RRAM [59]. A observação da variabilidade ciclo a ciclo é influenciada pela mudança no número de defeitos de vacância de oxigênio que surgem no FC devido à sua natureza estocástica de formação e ruptura durante o evento de troca [107]. Devido a esta natureza aleatória do CF, a previsão e o controle preciso da forma do CF tornam-se extremamente desafiadores. Esta variabilidade piora conforme o limite de conformidade (ou seja, conformidade atual ‘ I cc ') É reduzido. Por outro lado, para o valor mais alto de ‘ I cc ’, A razão do desvio padrão ( σ ) e resistência média ( μ ) é baixo, resultando em uma propagação de resistência LRS menor. Isso é atribuído aos defeitos mais elevados no CF, formando assim um caminho bem definido para a condução da corrente.

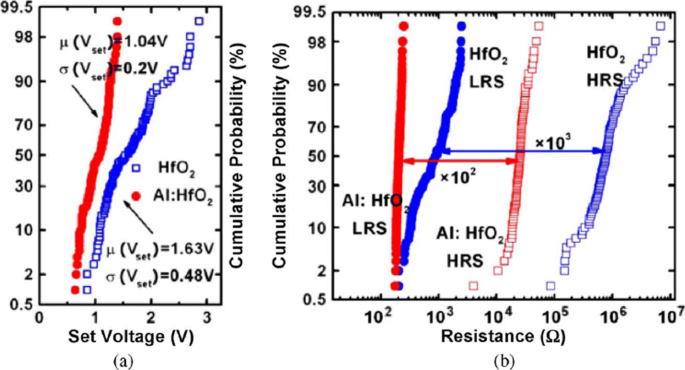

RRAM também exibe não uniformidade dispositivo a dispositivo (célula a célula), o que também degrada o desempenho da memória, reduzindo a margem de memória entre dois estados. A origem desta variabilidade é atribuída às não uniformidades no processo de fabricação, como a espessura do filme de switching, danos por corrosão e rugosidade da superfície dos eletrodos. Muitas pesquisas foram conduzidas para melhorar a uniformidade do RRAM e vários métodos foram explorados para o mesmo. Um dos métodos utiliza o conceito de inserção de sementes de nanocristais que confinam os caminhos do filamento condutor, aumentando o efeito do campo elétrico local [82, 90, 108]. Em Ti / TiO 2− x / RRAM baseado em Au [28], a indução de nano-cristais de platina (Pt) dentro do TiO fino 2− x resulta em uma uniformidade aprimorada da célula RRAM. Os nano-cristais de Pt limitam o efeito de comutação em regiões com alta probabilidade de geração de vacância de oxigênio, o que resulta em uniformidade aprimorada. Em outra abordagem, a engenharia da interface eletrodo / óxido incorporando camadas de buffer apropriadas é muito útil para alcançar uma operação RRAM uniforme. Em HfO x baseado em RRAM [109], uma fina camada tampão de Al é inserida entre o eletrodo TiN e HfO x camada de óxido. Isso resulta em uma melhoria significativa da distribuição de tensão definida, bem como a distribuição de resistência, aumentando assim a uniformidade do dispositivo. A melhoria na tensão SET e a distribuição de resistência do dispositivo RRAM após a inserção de uma fina camada tampão de Al entre o eletrodo TiN e HfO x óxido bruto e o mesmo é representado na Fig. 8 [59]. Presume-se que átomos de Al se difundam em HfO 2 filmes finos, e tendem a localizar vacâncias de oxigênio devido à redução da energia de formação de vacâncias de oxigênio, estabilizando a geração de filamentos condutores, o que ajuda a melhorar a uniformidade de chaveamento da resistência.

Melhoria da uniformidade de HfO tamponado com Al x RRAM em comparação com HfO x com base em matriz RRAM. a Distribuição estatística da tensão SET ( V conjunto ) obtido a partir de 100 ciclos de varredura DC. b Distribuição estatística HRS e LRS para 100 ciclos de varredura de pulso; reimpresso da ref. [59]

Além da abordagem de engenharia de materiais, um novo método de programação também foi sugerido para reduzir as flutuações. Uma técnica de formação de várias etapas foi implementada em W / HfO 2 RRAM baseado em / Zr / TiN [22] para minimizar a corrente excessiva devido aos efeitos parasitários. Uma técnica de formação de várias etapas resulta na formação gradual do filamento; assim, uma corrente de ajuste / reinicialização baixa é alcançada melhorando as características de chaveamento do dispositivo. Vários outros métodos, como formação de tensão constante e formação a quente (geralmente referida como formação a uma temperatura mais alta) também foram investigados para reduzir efetivamente as variações de resistência [110]. Outro método para alcançar alta uniformidade é aplicando um trem de pulso ao invés de um único pulso a uma célula RRAM [23]. Esta abordagem não só resulta em uniformidade melhorada, mas também aumenta a capacidade de vários níveis de uma célula RRAM.

Efeito da temperatura operacional e ruído aleatório do telégrafo

Para obter um desempenho confiável do dispositivo RRAM, o efeito da temperatura operacional e do ruído telegráfico aleatório (RTN) é investigado. Observa-se que a resistência dos estados LRS e HRS sofre variações em função da mudança da temperatura de operação. O estudo de temperatura de TiN / HfO 2 / Ti / TiN [111]. Uma tensão de varredura positiva de magnitude <3 V e corrente de conformidade de 1 μ A foi aplicada para a eletroformação. Uma vez que a formação ocorre, uma tensão de reinicialização ( V redefinir ) <–1 V muda o dispositivo de volta para o HRS (estado OFF). Para mudar o dispositivo de volta para o LRS (estado LIGADO), defina a tensão ( V conjunto ) <1 V é aplicado.

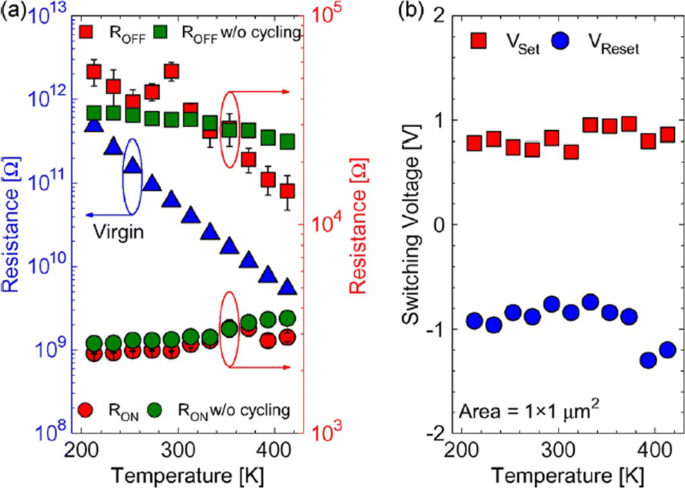

A operação de reinicialização no dispositivo RRAM tende a mostrar a resistência diferencial negativa controlada por tensão (NDR). A operação de reinicialização ocorre abruptamente em baixas temperaturas, enquanto para temperaturas acima da ambiente, o processo de reinicialização ocorre de forma mais gradual. A resistência do dispositivo RRAM no estado original, bem como o estado LIGADO e o estado DESLIGADO em função da temperatura, está representada na Fig. 9a. O comportamento semicondutor é observado para o estado primitivo, bem como para o estado OFF, ou seja, a resistência diminui com o aumento da temperatura. Para o estado ON, uma característica metálica é observada, ou seja, a resistência aumenta com o aumento da temperatura. Devido à variação da resistência com a mudança de temperatura, R OFF / R LIGADO também diminui de um valor de 20 para aproximadamente 5 no intervalo de temperatura de 213–413K. Em Ti / HfO x Dispositivos / Pt, diminuição em R OFF / R LIGADO foi observada com ciclos dependentes da temperatura. Esta diminuição na taxa de resistência foi atribuída ao acúmulo de armadilhas relacionadas à vacância de oxigênio dentro do HfO 2 camada de óxido de metal [112, 113]. Além disso, medições dependentes da temperatura sem operação de ajuste / redefinição foram realizadas para avaliar o impacto do ciclo I-V no R OFF / R LIGADO Razão. A tensão de varredura através do dispositivo RRAM foi interrompida antes de atingir V conjunto e V redefinir valores. Para a resistência do estado OFF (retângulos verdes), uma dependência da temperatura mais fraca foi observada em contraste com a resistência do estado ON (círculos verdes) que exibiu características semelhantes, em comparação com o caso de ciclagem. A partir dessas observações, inferimos que o ciclo I-V induz uma dependência mais forte da temperatura, o que diminui o R DESLIGADO / R LIGADO Razão. O efeito da variação de temperatura nas tensões de comutação V conjunto e V redefinir está representado na Fig. 9b. A ligeira variação em V conjunto com a mudança de temperatura indica que não há diferença significativa de temperatura. Para o caso de V redefinir , a tendência geral é que uma diminuição no valor da tensão de cerca de 0,2 V com aumento de temperatura na faixa de 233–333K seja observada. Além disso, um aumento lento de V redefinir é observado para a faixa de temperatura de 353–413K.

O efeito da variação da temperatura em a resistência virgem (eixo esquerdo) e o estado OFF, bem como as resistências do estado ON (eixo direito) na faixa de temperatura de 213–413K e b voltagens de comutação V conjunto e V redefinir ; reimpresso da ref. [111]

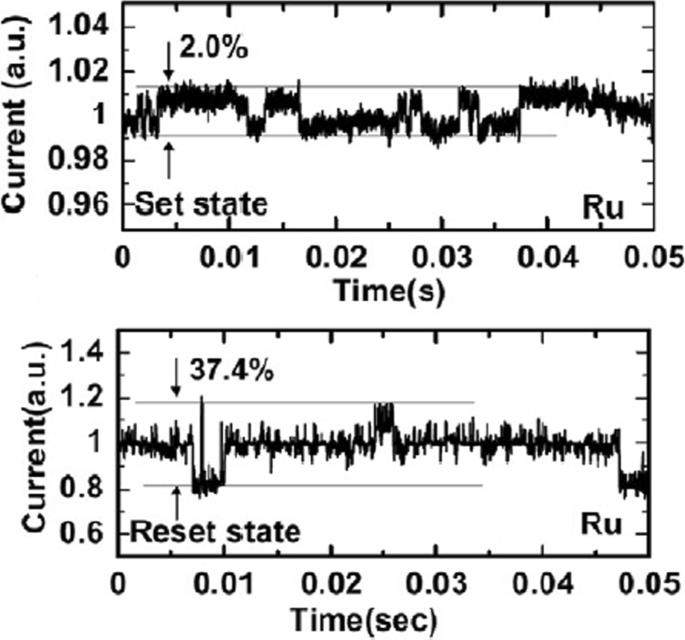

Ruído telegráfico aleatório (RTN) é outro fator que afeta o desempenho do RRAM. O RTN tem sido usado por muito tempo como um indicador de desempenho e confiabilidade do dispositivo. O RTN diminui a margem de memória entre o HRS e o LRS devido às grandes flutuações na corrente de leitura durante a operação de leitura. Devido ao efeito do RTN, a margem de leitura, o potencial de escala e a capacidade da célula multinível de uma célula RRAM são bastante afetados [114]; portanto, ele precisa ser investigado para obter um desempenho confiável. Para investigar o efeito do eletrodo inferior no RTN, uma análise de Ta 2 O 5 / TiO 2 RRAM [115] foi realizado. Os exemplos de sinais RTN complexos em LRS e HRS são representados na Fig. 10. O RTN causa instabilidade de leitura no dispositivo RRAM, reduzindo assim a margem de leitura, implementação de armazenamento multibit e dificultando o dimensionamento do dispositivo. O RTN é atribuído ao aprisionamento e retirada de elétrons nas proximidades do CF em LRS, ao passo que ocorre no gap de tunelamento no estado HRS. Embora a física do RTN ainda não seja clara e esteja sendo altamente debatida, o aprisionamento e retirada de elétrons que temporariamente inibe o transporte de carga é amplamente aceito como o mecanismo responsável pela flutuação devido ao RTN. Observa-se que com a diminuição da corrente de operação, a amplitude do RTN aumenta, afetando fortemente o nível de HRS. Portanto, é necessário garantir a margem de resistência adicional para obter um desempenho confiável. O RTN em RRAM tem sido pesquisado extensivamente, embora o mecanismo físico do RTN ainda não esteja explicitamente definido. O RTN pode ser utilizado como ferramenta para mapear os movimentos das vagas ativas no RRAM devido à sua variação dependente do tempo. Isso pode ser muito útil para entender os mecanismos de falha de outros problemas de confiabilidade.

Sinais RTN complexos em LRS e HRS de Ta 2 O 5 / TiO 2 com base em RRAM que descreve a amplitude de ruído normalizada e a corrente média; reimpresso da ref. [114]

Memória de acesso aleatório resistiva multinível (RRAM)

Armazenamento multinível por célula (mlc)

Devido ao seu pequeno tamanho físico e baixo consumo de energia, os dispositivos RRAM são potenciais para futuras aplicações de memória e lógica. O aumento da densidade de armazenamento está entre os aspectos mais críticos da tecnologia de memória para permitir o projeto de células de memória com capacidade multibit [89]. Os vários estados resistivos podem ser alcançados em células RRAM que fornecem benefícios de soluções de armazenamento de dados não voláteis de baixo custo e alta densidade. Atualmente, muitas pesquisas estão sendo conduzidas na área de RRAM para reduzir as dimensões e aumentar a densidade estrutural dos arranjos de memória. Anteriormente, a densidade de armazenamento de RRAM foi aumentada pela redução do tamanho do dispositivo; no entanto, a complexidade envolvida nos procedimentos experimentais limita sua implementação bem-sucedida. Outro método sugerido é o emprego de arquiteturas de barras transversais tridimensionais (3D). Dois tipos de arquiteturas de RRAM ‘vertical’ e ‘crossbar’ foram propostos [116, 117]; no entanto, esses dois tipos de arquitetura exigem procedimentos de fabricação avançados, o que não é desejável. Uma alternativa muito mais simples para aumentar a densidade de armazenamento em dispositivos RRAM é fazer uso da tecnologia de armazenamento de célula multinível (MLC), que permite armazenar mais de um bit por célula sem reduzir as dimensões físicas do dispositivo. Este MLC é uma das propriedades mais promissoras do RRAM, que pode aumentar significativamente a densidade de armazenamento da memória [83, 118-125]. Assim, em vez de um único estado de alta e baixa resistência (HRS e LRS), podemos alcançar vários HRS e LRS, sem alterar as dimensões do dispositivo. No entanto, para obter uma operação confiável do MLC, o controle preciso sobre a resistência dos diferentes níveis de resistência do RRAM deve ser garantido; caso contrário, o dispositivo sofrerá de variabilidade de resistência e problemas de confiabilidade principalmente devido à natureza aleatória da formação do filamento condutor durante o processo de comutação [126].

Métodos para obter modos multinível por célula (mlc) em RRAM

O comportamento do MLC no RRAM o torna muito útil para aplicações de alta densidade. Para obter o comportamento do MLC no RRAM, os três métodos a seguir são empregados:(i) alteração da corrente de conformidade, (ii) controle da tensão de reinicialização e (iii) variação da largura de pulso da operação de programação / exclusão.

MLC ao alterar a conformidade atual

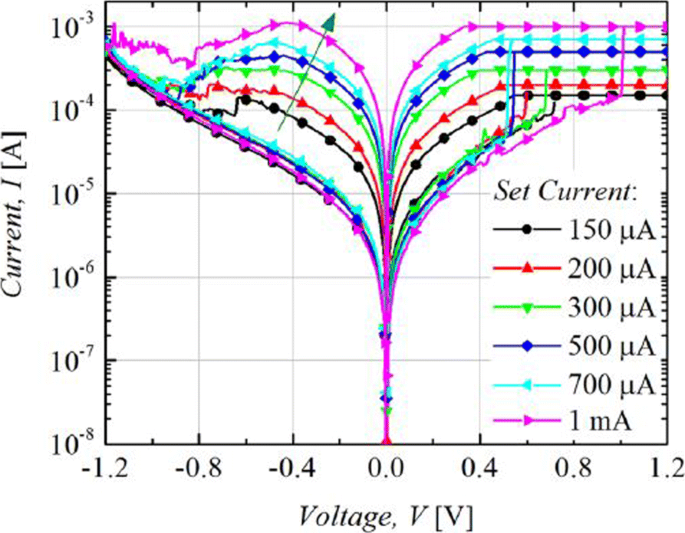

O dispositivo RRAM é normalmente operado com configuração de célula 1-RRAM (1R) [41] ou em configuração de célula 1-Transistor 1-RRAM (1T-1R) [18]. As características do MLC na configuração 1R podem ser obtidas alterando a conformidade atual ( I cc ) durante a operação de 'conjunto', enquanto as características MLC na estrutura de célula 1-Transistor 1-RRAM (1T-1R) são controladas pela variação da tensão na porta do transistor, o que permite o controle da corrente de conformidade (I cc ) durante a operação de configuração de uma célula RRAM. As curvas MLC I-V típicas de Ti / Ta 2 O 5 / Pt [127] com base em células RRAM são mostradas na Fig. 11. Como a corrente de conformidade ( I cc ) é aumentado de 150 μ De A a 1 mA, seis LRS diferentes são obtidos em I cc =150 μ A, eu cc =200 μ A, eu cc =300 μ A, eu cc =500 μ A e eu cc =700 μ A, eu cc =1 mA devido ao aumento na respectiva corrente de LRS (I LRS ) enquanto o HRS é mantido constante e o HRS atual (I HRS ) permanece o mesmo para todos os níveis LRS. Para Ti / Ta 2 O 5 / Pt RRAM, com o aumento em I cc , a corrente de reset máxima (I reset ) também aumenta enquanto a tensão definida é quase mantida constante. Além disso, foi observado que a resistência do LRS (R LRS ) diminui enquanto o (I reset ) aumenta devido à formação de filamentos mais forte com o aumento em I cc .

Características multiníveis de Ti / Ta 2 O 5 / Pt RRAM obtido controlando a corrente de conformidade. ‘Reproduzido de [127], com a permissão da AIP Publishing’

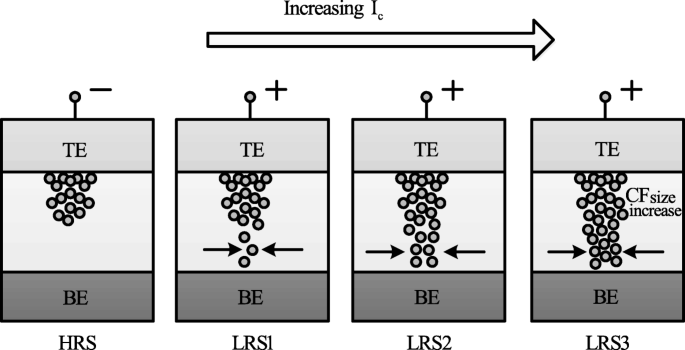

A formação do CF e o seu alargamento correspondente com o aumento de I cc é o mecanismo atribuído de multinível por célula (MLC) em conformidade com a corrente ( I cc ) modo como representado esquematicamente na Fig. 12. Com um aumento no tamanho de CF devido a um aumento de I cc , a resistência do CF diminui e, portanto, resulta em vários níveis de LRS para diferentes valores de I cc . Também é observado que eu reset aumenta com o aumento de I cc como maior potência é necessária para romper o CF com diâmetro maior.

Ilustração esquemática de vários estados de resistência na célula RRAM obtida pela variação da corrente de conformidade ‘ I cc ’[98]

MLC controlando a tensão de reinicialização

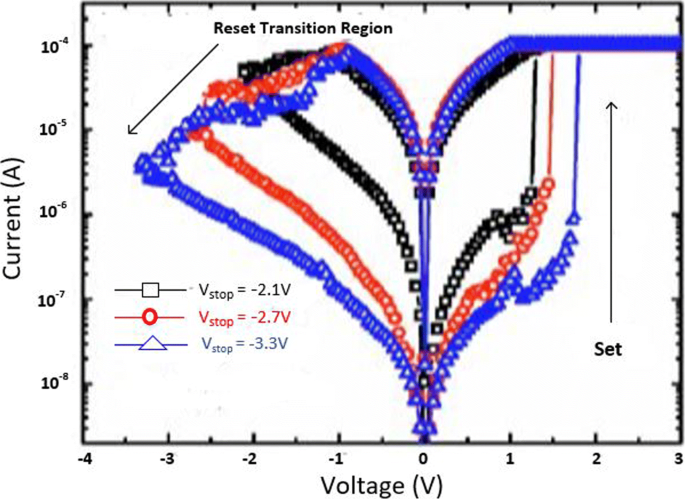

As características MLC em uma célula RRAM também podem ser obtidas controlando a tensão de reinicialização ( V redefinir ) enquanto ( eu cc ) é mantido constante. Neste caso, as curvas MLC I-V típicas de TiN / HfO x / AlO x / Célula RRAM baseada em Pt [128] aplicando diferentes ( V redefinir ) de - 2,1 V, - 2,7 V e - 3,3 V são mostrados na Fig. 13.

Características multiníveis de TiN / HfO x / AlO x / Pt RRAM obtido controlando a tensão de reset. ‘Reproduzido de [128], com a permissão da AIP Publishing’

Observa-se que com um aumento em ( V redefinir ), o HRS atual ( I HRS ) diminui; assim, vários níveis de HRS com a mesma resistência de LRS são obtidos. Além disso, a tensão definida ( V conjunto ) também aumenta à medida que V redefinir é aumentado enquanto o I redefinir permanece quase constante.

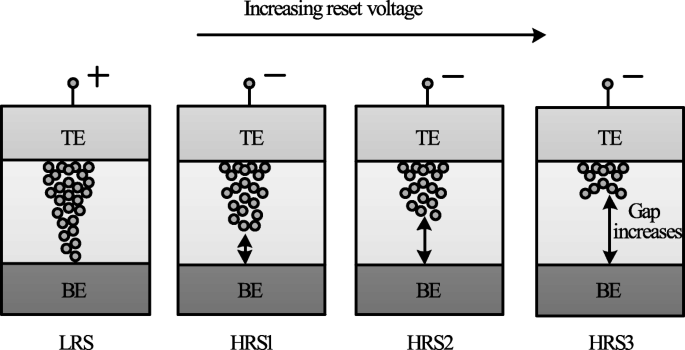

A diminuição em I HRS com o aumento na tensão de reinicialização é principalmente devido ao aumento na lacuna entre o eletrodo de metal e a ponta do CF, conforme ilustrado na Fig. 14. Quanto maior a magnitude do V redefinir , quanto maior a lacuna e, portanto, maior o valor da resistência. Portanto, um aumento na lacuna entre a ponta do CF e o eletrodo inferior (BE) com o aumento da tensão de reinicialização resulta em vários níveis de resistência de HRS. Observa-se que os dispositivos em que o eu redefinir mostra uma mudança gradual na corrente em vez da mudança abrupta durante a operação de "reset", a mudança na resistência HRS em tais dispositivos pode ser devido à diminuição no tamanho do filamento condutor (CF) como V redefinir Está melhorado. Essa abordagem é mais viável praticamente para arquiteturas de ponto cruzado, pois requer circuitos complexos relativamente mais baixos.

Ilustração esquemática de vários estados de resistência na célula RRAM obtida pela variação da tensão de reset ‘V reset ’[98]

MLC por programa variável / apagar largura de pulso

As características do MLC também podem ser obtidas variando a largura do pulso de programar / apagar enquanto a amplitude do pulso é mantida constante [23]. Em HfO x baseado em RRAM [128], três níveis de HRS foram demonstrados variando a largura do pulso de reinicialização de 50 ns a 5 μ s. Este método de obtenção de características MLC em RRAM é relativamente mais fácil; no entanto, este esquema é ineficiente em termos de energia. Esta desvantagem limita a aplicação deste método para obter características confiáveis na célula RRAM. O maior consumo de energia do dispositivo RRAM foi confirmado na comparação das respostas transitórias entre a amplitude de pulso de reset e o controle de largura de pulso. Isto é particularmente devido à dissipação de energia indesejada mais alta como a energia térmica no material de comutação resistivo.

Um resumo dos dispositivos RRAM exibindo múltiplos estados de resistência é mostrado na Tabela 4. Como fica evidente na tabela, vários dispositivos RRAM com múltiplos estados de resistência foram relatados. Até a data, no entanto, apenas 8 estados de resistência foram demonstrados em uma única célula RRAM, variando I cc ou V redefinir . Portanto, há um grande escopo para aumentar o número de estados de resistência na célula RRAM, aumentando assim sua densidade de armazenamento.

Modelagem de dispositivos RRAM

A modelagem desempenha um papel muito crítico no desenvolvimento de dispositivos que utilizam tecnologias de semicondutores. Para compreender totalmente a operação do dispositivo e otimizar o desempenho, um modelo preciso é de grande importância. Uma série de modelos RRAM com características e precisão variadas foram propostos [129]. Esta seção discute as características e atributos dos vários modelos RRAM comumente usados e populares.

Modelo Stanford / ASU

Um dos mais populares modelos RRAM baseados na física é o modelo Stanford / ASU RRAM [130-132], proposto por Guan et al. e Chen et al. Este modelo foi aplicado para validar as características de comutação I-V de HfO 2 RRAM [128] e inclui o efeito de aquecimento Joule e mudança de temperatura na comutação de dispositivos RRAM.

Este modelo é dependente do crescimento de CF dentro de uma camada de comutação dielétrica. A lacuna do filamento, ou seja, a lacuna entre a ponta do CF e o eletrodo superior, é a variável de estado interna para este modelo. O crescimento de CF dentro de um dielétrico é atribuído ao movimento de íons de oxigênio e regeneração e recombinação de vacâncias de oxigênio [133]. Assim, a taxa de variação da lacuna do filamento (g) é dada como [130]:

$$ {\ frac {dg} {dt}} =V _ {\ tiny {0}}. \ exp \ bigg ({{\ frac {-E_ {a}, m} {k_ {b} .T}}} \ bigg). {\ text {Sinh}} \ bigg ({\ frac {qa_ {h} \ gamma V} {L.k_ {b} .T}} \ bigg) $$ (1)

onde E a é a energia de ativação, V é a magnitude da tensão aplicada ao dispositivo, L é a espessura do material de comutação, a h é a distância do salto, γ é o fator de aprimoramento de campo local, V 0 é a velocidade que contém a tentativa de escapar da frequência, K b é a constante de Boltzmann, q é a carga unitária elementar e T é a temperatura do filamento condutor.

A variação espacial no tamanho do gap é contabilizada neste modelo, além das variações que surgem devido à propriedade estocástica do processo iônico. Um sinal de ruído é adicionado à distância do intervalo para contabilizar essas variações como [130]:

$$ g_ {| t + \ Delta t} =F \ Grande [g_ {| t}, {\ frac {dg} {dt}} \ Grande] + \ delta_ {g} \ times \ tilde {X} (n) \ Delta t, n ={\ frac {t} {T_ {GN}}} $$ (2)

onde Δ t é o intervalo de tempo da simulação, a função F representa a evolução temporal do tamanho do intervalo de t para Δ t. \ (\ tilde {X} \) (n) é uma sequência de ruído gaussiano de média zero. T GN é o intervalo de tempo após o qual \ (\ tilde {X} \) ( n ) muda para o próximo valor aleatório.

A variação no tamanho da lacuna δ g depende da energia cinética dos íons e da temperatura do filamento como [130]:

$$ \ delta_ {g} (T) ={\ frac {\ delta ^ {\ tiny {0}} _ {g}} {\ bigg \ {1+ \ exp \ Big ({\ frac {T _ {\ text {crit}} - T} {T _ {\ text {smith}}}} \ Big) \ bigg \}}} $$ (3)

onde \ (\ delta ^ {0} _ {g} \) e T smith são coeficientes de ajuste para coincidir com as curvas de distribuição de resistência para experimentos e T crit é uma temperatura limite acima da qual o tamanho da lacuna muda significativamente.

Este modelo mostra forte dependência da temperatura; assim, há uma necessidade de levar em consideração a mudança de ‘T’ . Com a mudança nas características da célula, a temperatura do domínio interno dinâmico T muda significativamente, enquanto o domínio externo assumido estar em temperatura uniforme e estável (T banho ), está relacionado como [130]:

$$ c_ {p} {\ frac {dT} {dt}} =V (t) .I (t) - k (T-T _ {\ text {banho}}) $$ (4)

onde C p é a capacitância de calor efetiva do domínio interno, V (t) eu (t) representa o aquecimento Joule e k é a condutividade térmica efetiva.

Usando um mecanismo de condução generalizado, a condução de corrente é definida como [130]:

$$ I (g, v) =I _ {\ tiny {0}}. \ Exp \ bigg ({{\ frac {-g} {g _ {\ tiny {0}}}}} \ bigg) {\ text { Sinh}} \ bigg ({\ frac {V} {V _ {\ tiny {0}}}} \ bigg) $$ (5)

onde eu 0 , g 0 e V 0 são os parâmetros de ajuste para coincidir com os resultados experimentais.

Uma das características significativas deste modelo é a sua implementação em aplicações neuromórficas e projeto de dispositivo sináptico RRAM [134], dando ao modelo um grande grau de flexibilidade e maior escopo para implementação em vários sistemas neuromórficos.

Modelo físico eletrotérmico

O modelo físico eletrotérmico foi desenvolvido por Kim et al. [135] e implementado com pentóxido de tântalo (Ta 2 O 5 bicamada baseada em) RRAM [136–138]. Este modelo físico resolve as equações diferenciais com base no método de solução de elementos finitos. Este modelo também faz uso da abordagem do fenômeno da física eletrotérmica para modelagem [139], dando assim vantagem em termos de flexibilidade para incorporar o solver do método dos elementos finitos (FEM) para simular o sistema com muita precisão. No entanto, a desvantagem dessa abordagem é a dificuldade de implementação para resolvedores de circuito SPICE e Verilog.

Este modelo descreve CF como uma região dopada com vacâncias de oxigênio como dopantes com CF se estendendo do topo ao eletrodo inferior do dispositivo. Para descrever a deriva-difusão da migração de vagas, este modelo assume que a mesma equação pode ser usada para descrever os processos de íons de oxigênio e vagas. O modelo de íons de Mott e Gurney [140] é empregado aqui para descrever o processo dado como [135]:

$$ {\frac{dn_{D}}{dt}} =\Delta \times \bigg(D_{s}.\Delta_{n\tiny{D}}- \mu v n_{D} \bigg) + G $$ (6)

onde D s describes the diffusion process, v gives the drift velocity of vacancies and G is the CF growth rate which actually describes the SET process. The parameters are defined as [135]:

$$ D_{s} ={\frac{1}{2}} \times a^{2} \times f_{e} \times \exp \bigg({\frac{- E_{a}}{k_{B}T}} \bigg) $$ (7) $$ v =a_{h} \times f \times \exp \bigg({\frac{- E_{a}}{k_{B}T}} \bigg) \times {\text{Sinh}} \bigg({\frac{q a_{h}E}{k_{B}T}} \bigg) $$ (8) $$ G =A \times \exp \bigg({\frac{- (E_{a}-ql_{m}E)}{k_{B}T}} \bigg) $$ (9)

where l m is the mesh size.

These equations govern the physical transformation of the device during SET and RESET transition, thus essentially controlling the CF growth and rupture.

Huang’s Physical Model

Huang’s physical model developed by Huang et al. [141, 142] is a very comprehensive physical model for RRAM device as it takes into account both the CF width and the gap of filament to electrode as the factors affecting the state variable dynamics. In addition, temperature distribution is also accounted for in this model.

SET/RESET process is considered as a result of generation/recombination process of oxygen ions (O 2− ) and oxygen vacancies (V 0 ) During the SET process, CF starts to evolve from the tip of the top electrode (T.E) and elongates in radius with increase in voltage, resulting in final width ‘W’ of the C.F. This model assumes symmetrical cylindrical shape of the C.F. During RESET process, CF ruptures starting from TE till it dissolves completely with increase in voltage. The filament gap distance ‘x’ is defined as the gap between active electrode layer (T.E) and the tip of the C.F.

Thus, for the SET process, parameter ‘W’ acts as state variable, while for RESET, parameter ‘x’ acts as state variable. Therefore, \(\frac {dx}{dt}\) and \(\frac {dw}{dt}\) define the dynamics of the device during the SET/RESET transition.

During the first reset process, CF reduction rate, i.e. release of O 2− , is by the electrode is expressed as [142]:

$$ {\frac{dx}{dt}} =a \times f\times \exp \bigg({\frac{- E_{i}-\gamma Z_{e}V}{k_{B}T}} \bigg) $$ (10)

For O 2− hopping within the oxide layer, the CF reduction rate with ‘a’ being the distance between two V0 is given as [142]:

$$ {\frac{dx}{dt}} =a \times f\times \exp \bigg({\frac{- E_{h}}{k_{B}T}} \bigg) {\text{Sinh}} \bigg({\frac{ a_{h}Z_{e}E}{k_{B}T}} \bigg) $$ (11)

For the case of RESET process when dominated by recombination between O 2− and V0 is expressed as [142]:

$$ {\frac{dx}{dt}} =a \times f\times \exp \bigg({\frac{- \Delta E_{r}}{k_{B}T}} \bigg) $$ (12)

In the initial step of the SET process dominated by recombination of oxygen vacancies with thin CF initially grown is given by [142]:

$$ {\frac{dx}{dt}} =-a \times f_{e}\times \exp \bigg({\frac{- E_{a}-\alpha_{a} Z_{e}E}{k_{B}T}} \bigg) $$ (13)

Here, Z e α g are the fitting parameters.

For the second step, CF grows along its radial direction and is defined as [142]:

$$ {\frac{dw}{dt}} =\bigg(\Delta w + {\frac{\Delta w^{2}}{2w}} \bigg) \times f_{e}\times \exp \bigg({\frac{- E_{a}-\gamma Z_{e}v}{k_{B}T}} \bigg) $$ (14)

The current flowing through the device is modeled as a correlation of hopping current with voltage and gap distance expressed by [134] as:

$$ i =i_{0}. \exp \bigg({\frac{-x}{x_{T}}} \bigg) {\text{Sinh}} \bigg({\frac{v}{v_{T}}} \bigg) $$ (15)

This model is validated in HfO x /TiO x system [141, 142], and a pretty accurate match between the experimental and simulation results is obtained. Although this model accounts for the significant processes which affect the RRAM operation, however, it has some limitations. The most critical one is being incompatible with the SPICE and Verilog-A.

Filament Dissolution Model

This model was developed exclusively for unipolar RRAM devices by Russo et al. [143–145], however was later modified for bipolar RRAM devices [139, 146] also. Filament dissolution model is based on rupture of CF under the effect of significant temperature change caused due to Joule heating.

One of the significant advantages of this model is that it utilizes the simple partial differential equations to account for the device current and temperature changes due to Joule heating as well as the dissolution velocity. The conduction of current within the device is described by Poisson’s equation [144] as:

$$ \triangledown \times \bigg({\frac{1}{\varphi}\triangledown_{v}} \bigg) =0 $$ (16)

Aqui, φ is the oxide resistivity and v defines the electric potential due to the application of external bias voltage to one of the electrodes while the other electrode is connected to ground.

The CF is divided into a number of mesh grids and at each point of the mesh grid the temperature is calculated to describe the rupture of CF. The Fourier steady-state heat equation describes this effect as [144]:

$$ -\triangledown \times \bigg(k \triangledown T \bigg) =\varphi J^{2} $$ (17)

onde k represents the oxide layer thermal conductivity, J is the current density and T is the device temperature.

The temperature ‘T’ of the device increases to the critical temperature, after which the device is reset and the CF dissolution takes place. The dissolution factor is modeled as [144]:

$$ V_{\text{DIS}} =V_{\text{DIS}-F}. \exp \bigg({\frac{- E_{a}}{k_{B}T}} \bigg) $$ (18)

onde E a is the activation energy, k b is the Boltzmann constant, V DIS−F is a fitting parameter and V DIS is velocity of CF boundary towards symmetry axis.

The resistivity of CF is temperature-dependent and is described as [144]:

$$ \varphi_{\text{CF}} (T) =\varphi_{\mathrm{CF-RT}} \Big[ 1 + C (T-T_{0}) \Big] $$ (19)

onde C is the experimentally calculated temperature coefficient of resistivity and φ C F −R T is the standard CF resistivity at room temperature.

COMSOL Multiphysics Software [147] is used for solving the coupled equations for this RRAM model due to its multiphysics capabities and ability to handle such simulations.

Bocquet Bipolar Model

Bocquet bipolar model [148] describes the bipolar oxide-based resistive switching memories utilizing a physics-based modeling approach. Bocquet bipolar model describes the electroforming process of RRAM device, inaddition to utilizing some of the characteristics from Bocquet unipolar model [149] and modifies them significantly according to the bipolar switching characteristics. In this model, the radius of the CF is the internal state variable which effectively governs the switching rate.

To model the electroforming stage, Bocquet bipolar model utilizes electroforming rate (τ Form ) which details the mechanism of conversion to switchable sub-oxide from pristine oxide. The electroforming stage is modeled as [148]:

$$ \tau_{\text{form}} =\tau_{\text{form}0} \times \exp \bigg({\frac{E_{a\text{Form}}-q \times \alpha_{s} \times V_{\text{cell}}}{k_{B}\times T}} \bigg) $$ (20) $$ {\frac{dr_{\text{CFmax}}}{dx}} ={\frac{r_{\text{work}}-r_{\text{CFmax}}}{\tau_{\text{form}}}} $$ (21)

onde E a Form is the activation energy for electroforming, τ form0 is the nominal forming rate, α s is the charge transfer coefficient, V cell is the voltage applied between the top and bottom electrodes, r CF is the radius of CF which varies from 0 to r CFmax , q is the elementary charge of electron, T is the temperature of the device and k B é a constante de Boltzmann.

The electrochemical redox reaction derived from Butler-Volmer equation [150] is used to describe the SET/RESET operation as [148]:

$$ \tau_{\text{Red}} =\tau_{\text{Redox}} \times \exp \bigg({\frac{E_{a}-q \times \alpha_{s} \times V_{\text{cell}}}{k_{B} \times T}} \bigg) $$ (22) $$ \tau_{Ox} =\tau_{\text{Redox}} \times \exp \bigg({\frac{E_{a}+q \times (1 - \alpha_{s}) \times V_{\text{cell}}}{k_{B} \times T}} \bigg) $$ (23)

Here, τ Red e τ Ox are the reduction and oxidation rates, respectively. τ Redox is the effective reaction rate considering both reduction and oxidation reactions.

The switching rate is obtained by coupling the above two equations as [148]:

$$ {\frac{dr_{CF}}{dt}} ={\frac{r_{\text{CFmax}}-r_{\text{CF}}}{\tau_{\text{red}}}} - {\frac{r_{\text{CF}}}{\tau_{\text{Ox}}}} $$ (24)

Bocquet bipolar model is a quite comprehensive model as it includes the temperature effects as well. The local filament temperature is coupled using heat equation and is given in Eq.(25), the temperature considering a cylindrical-shaped filament is given in Eq. (26). The maximum temperature reached into CF at x =0, the middle of the filament is given in Eq. (27) and the equivalent electrical conductivity in the work area (σ eq ) is given in Eq. (28).

$$ \sigma_{x} \times F(x)^{2} =- k_{th}.{\frac{d^{2}T(x)}{dx^{2}}} $$ (25) $$ T(x) =T_{\text{amb}}+{\frac{V^{2}_{\text{cell}}}{2. L^{2}_{x}.k_{th}}} \bigg({\frac{L^{2}_{x}}{4}- x^{2}} \bigg) \sigma_{eq} $$ (26) $$ T =T_{\text{amb}}+{\frac{V^{2}_{\text{cell}}}{8. k_{th}}} \sigma_{eq} $$ (27) $$ \sigma_{eq} =\sigma_{CF}.{\frac{r^{2}_{\text{CF}}}{r^{2}_{\text{work}}}} - \sigma_{Ox}. {\frac{r^{2}_{\text{CFmax}}-r^{2}_{\text{CF}}}{r^{2}_{\text{work}}}} $$ (28)

where (σ x ) is the local electrical conductivity, F ( x ) is the local electric field, σ CF is the electrical conductivity of the conductive filament, k th is the thermal conductivity and T amb is the ambient temperature.

It must be mentioned here that temperature increases with increase in radius of the CF, resulting in self-accelerated reaction due to a positive feedback loop. The self-limited reaction also referred to as SOFT reset [151], on the other hand, occurs due to the decrease in temperature and radius of the CF during RESET operation.

The total current flowing in OxRRAM is the sum of currents flowing in the conductive area (I CF ), the conduction through switchable sub-oxide (I sub−oxide ) and conduction through unswitched pristine oxide (I pristine ) The total current is as [148]:

$$ I_{\text{cell}} =I_{\mathrm{sub-oxide}} + I_{\text{CF}} + I_{\text{Pristine}} $$ (29) $$ I_{\text{CF}} =F.\pi. \sigma_{CF}.r^{2}_{CF} $$ (30) $$ I_{\mathrm{sub-oxide}} =F.\pi. \sigma_{Ox}. \big(r^{2}_{\text{CFmax}}- r^{2}_{CF}\big) $$ (31) $$ I_{\text{Pristine}} =S_{cell}.A.F^{2}. \exp {\frac{-B}{F}} $$ (32) $$ A ={\frac{m_{e}.q^{3} }{8\pi.h.m^{ox}_{e}.\phi_{b} }} $$ (33)

The parameter B e is the metal-oxide barrier height (ϕ b )-dependent and is given as [148]:

$$ if \phi_{b}\geq qL_{x}F:B_{e} ={\frac{8 \pi \sqrt{2m^{ox}_{e} }}{3\times h\times q}} \Big[ \phi^{{\frac{3}{2}}}_{b}- (\phi_{b}-qL_{x}E)^{{\frac{3}{2}}} \Big] $$ $$ \text{otherwise}, B_{e} ={\frac{8 \pi \sqrt{2m^{ox}_{e} }}{3\times h\times q}} \times \phi^{{\frac{3}{2}}}_{b} $$ (34)

where m e and \(m^{ox}_{e}\) are the effective electron masses into the cathode and oxide respectively, F =\(\frac {V_{\text {cell}} }{L_{x}}\) is the electric field across the active layer, h is the Planck constant and S cell is the section of the RRAM cell.

Discrete solutions are required to implement the model in an electrical simulator. This model accounts well in that aspect, making it suitable for simulation involving electrical circuits. This model implements equations in Eldo circuit simulator [152]. The discrete solutions are given as [148]:

$$ r_{\text{CFmax}_{i+1}} =\big(r_{\text{CFmax}_{i}}- r_{\text{work}} \big) \times e^{ {\frac{-\Delta t}{{\tau}_{\text{form}}}} } + r_{\text{work}} $$ (35) $$ r_{CF_{i+1}} =\bigg(r_{CF_{i}}- r_{\text{CFmax}_{i}} \times {\frac{\tau_{eq}}{\tau_{\text{Red}}}} \bigg) \times e^{ {\frac{-\Delta t}{{\tau}_{eq}}} } + r_{\text{CFmax}_{i}} \times {\frac{\tau_{eq}}{\tau_{\text{Red}}}} $$ (36) $$ \text{where} { \tau_{eq}} =\frac{\tau_{\text{Red}}\times \tau_{\text{Ox}} }{\tau_{\text{Red}}+\tau_{\text{Ox}}} $$ (37)

This model has been verified against electrical characterization from an HfO2 -based system [153]. An important feature of this model is that it can account effectively for device to device variability [154, 155]. One of the major limitations of this model is the lack of current or voltage threshold.

This section presents in detail various characteristics and features of the RRAM models. A comparative analysis of the RRAM models discussed in this work is presented in Table 5.

Applications of RRAM

RRAM is seen as one of the standout candidates among the emerging memory technologies that has the potential for reforming the memory hierarchy primarily due to its high speed, the capability of non-volatile data storage, enhanced storage density and logic computing function. The various novel applications of RRAM are discussed in this section.

>Non-volatile Logic

The instruction codes and the data are transferred by making use of buses between various units in a computer system having von Neumann architecture because of the separate computing and memory unit. This data transferring process results increased energy consumption and time delay, which is commonly referred to as ‘von Neumann bottleneck’. For reducing the impact of von Neumann bottleneck [156], the computing process which utilizes RRAM crossbar array is suggested which alters the memory and computing operations in the same core. In addition, to obtain high integration density and low cost [157], two-terminal compact device structure of RRAM and its 4F 2 array architecture are highly beneficial. For example, to obtain simple Boolean logic functions such as ‘logic NOT’, ‘logic AND’, and ‘logic OR’, we require multiple transistors and each single transistor takes 8−10F 2 área. These logic functions can be realized by making use of two or three RRAM cells, resulting in total approximate area of around 10F 2 only [158].

Till date, several methods have been suggested for realizing Boolean logic functions [159, 160]. Boolean computing is significantly more established compared to existing non-Boolean computing paradigms such as neuromorphic computing and quantum computing. Therefore, energy and cost-efficiency of CPU or MCU can be enhanced without the need to develop new algorithms or software, although there is still a lack of technical solution on how to implement complex computing tasks in a crossbar array. Thus, most of research to date focusses on only basic logic level demonstration as it becomes quite complex to implement a whole computing unit using RRAM array.

Neuromorphic Computing

To overcome ‘von Neumann bottleneck’, one of the effective ways is brain-inspired neuromorphic computing which has shown promising potential in a wide range of complex and cognitive tasks like visual/audio recognition, self-driving, and real-time big-data analytics. Compared to CMOS-based neuromorphic network, neuromorphic computing based on RRAM-array offers advantages in terms of on-chip weight storage, online training, and scaling up to much larger array size [161–163]. In addition, the processing speed of RRAM improves by three orders of magnitude, whereas the power consumption rate is reduced by four orders of magnitude [164].

For realizing hardware-implemented neuromorphic computing paradigms, two methods are suggested:one among the strategies mimics the structure and working mechanism of biological neural networks while the other method works on accelerating the existing artificial neural network (ANN) algorithms. In a neural network, a synapse is used to transfer spikes between different neurons in addition to storing information about the transferring weights. The information regarding weights can be acquired through certain learning rules such as spike-time-dependent plasticity (STDP) and spike-rate-dependent plasticity (SRDP) [165–167]. Although some of the works reported in the literature have tried to emulate such learning rules on RRAM devices, it is however quite complicated to extend such types of bioinspired learning rules to a complex task as the theoretical algorithm is still lacking.

A practically viable approach is to map an ANN to a RRAM-based neuromorphic network directly. Some advanced tasks such as pattern and speech recognition have been demonstrated based on this method [166–169]. Although very promising, RRAM-based synapse is still far from being applied as various issues such as material optimization, variation suppressing, control circuit design, architecture, and algorithms design for analog computing need to be addressed effectively.

Security Application

The security aspect has become more prominent with rapid developments in the field of information technology; thus, there is a need for hardware-based security-integrated circuits. In contrast to security circuits based on CMOS logic which exploits the random nature of the semiconductor manufacturing process, security circuits based on RRAM are more robust to attacks of various types due to its completely random switching mechanisms [170, 171]. It must be noted that for security applications, larger variation of RRAM device parameters such as random telegraph noise (RTN), resistance variations and probabilistic switching is desirable, which is quite different from memory applications that require a smaller degree of variation among numerous parameters.

A novel security feature commonly referred to as physical unclonable function (PUF) [172], based on RRAM is proposed for device authentication (strong PUF) and key generation (weak PUF) applications. Significantly larger number of input-output pairs [also called challenge-response pair (CRP) are required for strong PUF, while only a small amount of CRPs of extremely higher reliability are required for weak PUF [173]. Although, PUFs based on RRAM have demonstrated remarkable performance; however, still more practical demonstrations and further evaluations are required to work out the maturity of this new primitive within the field of hardware security.

Non-volatile SRAM

Volatile memory technologies like SRAM and DRAM may consume over half of the static power within the current mobile SoC chips. Thus, to attain fast parallel memory operations, reduced area and low-energy consumption, RRAM-based non-volatile SRAM (nvSRAM) was proposed [174] in which two RRAM cells are stacked on eight transistors, forming an 8T2R structure. Also, non-volatile ternary content-addressable memory (TCAM) having 4T2R cell structure [175] and non-volatile flip flops having reduced stress time and write power based on RRAM have been demonstrated recently [176].

Challenges and Future Outlook

During the past several years, research in the field of emerging memory technologies has grown significantly and several prototype RRAM products have been developed demonstrating the potential for high-speed and low-power embedded memory applications. RRAM is one of the most promising memory technologies because of the advantages of simple structure, compatibility with the existing CMOS technology, good switching speed and ability to scale to the smallest dimensions. As a matter of fact, currently the Flash memory technology is facing difficulties to reduce to lower dimensions and as such RRAM is emerging as a potential replacement especially for fast operation and medium size storage density memory applications.