A Importância da Verificação de Confiabilidade em Processadores AI / ML

Com a adoção da inteligência artificial e do aprendizado de máquina em uma ampla variedade de aplicativos, a verificação da confiabilidade dos processadores AI / ML é crítica, pois as falhas podem ter consequências importantes para a validade e legitimidade da tecnologia AI / ML.

Nos últimos anos, houve uma rápida expansão no número de empresas implantando inteligência artificial (IA) e aprendizado de máquina (ML) em uma ampla gama de aplicações. Na verdade, estudos mostram que 2019 foi um ano recorde para empresas que adotaram IA e ML, e que essas empresas consideram esses dois recursos como os mais necessários para atingir suas metas e estratégias de negócios. Essa adoção crescente se deve principalmente ao aprimoramento dos algoritmos, aos avanços no design de hardware e ao aumento no volume de dados criado pela digitalização das informações.

No entanto, para apoiar e sustentar o crescimento da AI / ML, as empresas devem continuar a provar ao mercado que os resultados obtidos com as tecnologias de AI / ML são confiáveis. Essa confiança começa com o projeto e verificação dos circuitos integrados (ICs) que fundamentam a funcionalidade AI / ML.

Classificação de AI e ML

O processamento de AI pode ser amplamente classificado em datacenter / baseado em nuvem ou incorporado, dependendo se é realizado em um local de nuvem / datacenter ou no lado do usuário final (incorporando um chip AI dedicado ou um mecanismo de co-processador AI com um sistema em chip (SOC) dentro de dispositivos ou na borda). Borda, neste contexto, refere-se a um servidor local ou máquina que está mais perto do dispositivo do que um data center ou nuvem.

Em termos de aplicação alvo, um dispositivo de ponta pode ser classificado em treinamento (ML) ou inferência. Historicamente, a parte de treinamento era realizada no local da nuvem, com a parte de inferência sendo tratada na nuvem ou no dispositivo de borda. Com o desenvolvimento de novas soluções de computação de ponta de alto desempenho, estamos testemunhando uma mudança de paradigma à medida que mais atividades de treinamento estão sendo transferidas para a ponta.

Design de chip AI / ML

Os chips AI / ML em soluções de computação de ponta ou incorporados em dispositivos locais são projetados para uso em ambientes específicos, como corporativo, automotivo, industrial, saúde, Internet das coisas (IoT), etc. Alguns desses aplicativos são de missão crítica, ou seja, qualquer falha pode resultar em consequências desastrosas no mundo real. Por exemplo, considere os sistemas avançados de assistência ao motorista (ADAS) usados dentro de automóveis. Se um processador ADAS experimentar mais do que uma determinada latência ao ler os dados do sensor e fazer uma inferência, isso pode causar uma colisão.

Os ICs usados em aplicações AI / ML são caracterizados por grandes unidades de computação de processamento paralelo, alta dissipação de energia e circuitos complexos que podem fornecer desempenho máximo dentro de um orçamento estrito de energia. Embora algumas empresas empreguem unidades de processamento central (CPUs) tradicionais para tarefas relacionadas à IA, alguns especialistas do setor argumentam que o uso de CPUs não é muito eficiente, devido à natureza distribuída dos algoritmos de IA de última geração. Esses algoritmos funcionam bem para soluções de computação paralela, como as fornecidas por unidades de processamento gráfico (GPUs). Devido à sua natureza reconfigurável, os FPGAs (field-programmable gate arrays) também atraíram o interesse para serem usados como aceleradores de chips AI.

ASICs em aplicativos AI / ML

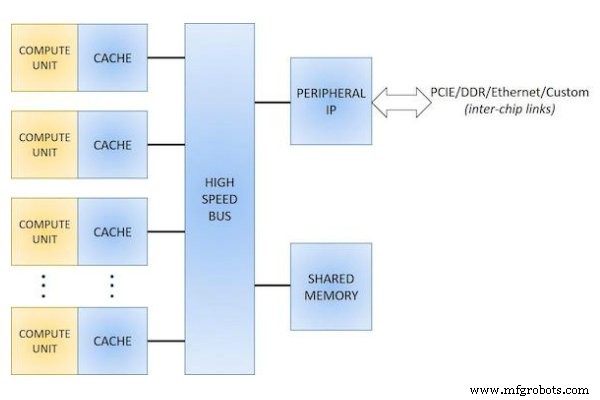

No geral, há um consenso crescente de que os problemas complicados de IA e ML não se prestam a uma solução de design única para todos. Para combater esse problema, muitas empresas desenvolvem seus próprios ICs específicos de aplicativo (ASICs), que otimizam em conjunto com a pilha de software para entregar o melhor valor para um determinado aplicativo AI / ML (Figura 1).

Figura 1. Diagrama de blocos para um design de chip ASIC AI.

Essas empresas reivindicam vários benefícios do uso desses ASICs, como melhor desempenho, mais operações por ciclo, um design mais simples e determinístico em comparação com uma CPU ou GPU, economia de área (devido à exclusão de construções e mecanismos complexos usados em um CPU), menor uso de energia e tempo de desenvolvimento mais rápido.

Computação Heterogênea

Também houve um aumento no uso de computação heterogênea - sistemas que usam uma combinação de diferentes tipos de núcleo de computação em um esforço para combinar o melhor dos diferentes recursos. Por exemplo, em um sistema que usa uma combinação de CPU e GPU, a computação heterogênea pode ser benéfica ao descarregar as tarefas paralelas para a GPU, enquanto a CPU lida com tarefas como controle de processo, que é serial por natureza.

Um aspecto comum entre diferentes classes de processadores AI é que eles são otimizados para alto desempenho e baixa latência, muitas vezes oferecendo multiplicadores de desempenho de operações tera por segundo (TOPS). Para obter uma vantagem neste mercado altamente competitivo, a eficiência energética (medida pelo desempenho por watt) tornou-se tão importante quanto o rendimento bruto. A eficiência energética é frequentemente alcançada usando uma combinação de uma ou mais técnicas de design, como energia e disparo de clock, tensão dinâmica e escala de frequência, designs multi-Vt, etc.

Garantir o projeto confiável e a verificação desses CIs complexos é fundamental, uma vez que as falhas de circuito nesses chips podem ter consequências importantes para a validade da tecnologia e legitimidade dos resultados que eles fornecem.

Verificação de confiabilidade AI / ML IC

A verificação de confiabilidade é um grande desafio em chips AI / ML, devido ao tamanho e complexidade desses projetos, com contagens de transistores da ordem de milhões - às vezes até mesmo de bilhões. Por exemplo, a GPU TESLA P100 da NVIDIA possui uma contagem impressionante de transistores de 15,3 bilhões, enquanto o Loihi IC da Intel contém 128 núcleos neuromórficos e 3 núcleos X-86, com 2,07 bilhões de transistores. E, como os requisitos de confiabilidade para cada ambiente de uso são diferentes, os projetistas devem compreender o conjunto aplicável de requisitos e garantir que sejam atendidos testando seus projetos em relação a especificações de requisitos de confiabilidade bem definidas.

Métodos de verificação de confiabilidade do projeto

Tradicionalmente, os projetistas usavam uma variedade de métodos para garantir a confiabilidade do projeto, incluindo inspeção manual e técnicas de simulação, contando principalmente com o conhecimento e a experiência de sua equipe de projeto. No entanto, a inspeção manual não é uma abordagem viável para esses chips de AI / ML grandes e complexos, uma vez que é demorada e sujeita a erro humano, e virtualmente impossível de fornecer cobertura suficiente. As abordagens tradicionais de simulação do tipo SPICE também não são práticas para esses ICs, devido à falta de escalabilidade para projetos grandes.

Para superar os problemas de capacidade e tempo de execução, muitas equipes de design particionam manualmente um design e verificam diferentes blocos de propriedade intelectual (IP) de forma independente por meio de simulação ou ferramentas tradicionais. No entanto, existem muitas interações entre diferentes blocos de IP em um design (por exemplo, entre diferentes núcleos de computação e o barramento ou link ou memória de alta largura de banda), e as interações entre interfaces muitas vezes tendem a ser negligenciadas durante um processo de particionamento manual. As ferramentas de verificação de IC tradicionais lutam com tempos de execução excessivamente longos para verificar esses projetos complexos, muitas vezes levando dias para verificar projetos grandes e potencialmente atrasando o tempo de lançamento no mercado.

As deficiências em cada um desses processos destacam a necessidade de uma solução abrangente de automação de projeto eletrônico (EDA) que possa tirar proveito do poder de computação de várias CPUs e dispositivos simultaneamente. Com a verificação de confiabilidade automatizada e qualificada, as equipes de design e verificação de produto podem convergir mais rapidamente para a verificação e correções de confiabilidade, reduzindo o tempo de retorno geral (TAT) de dias para horas.

A plataforma de confiabilidade Caliber PERC

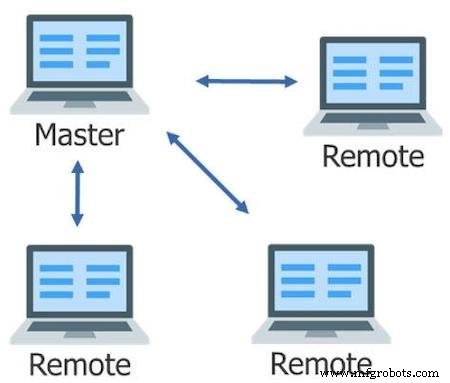

Nos últimos anos, surgiu uma nova classe de ferramentas de verificação de confiabilidade de IC que resolvem esses problemas de processo. Ferramentas como a plataforma de confiabilidade Caliber ™ PERC ™ aproveitam um rico conjunto de recursos e funcionalidades para fornecer verificação de confiabilidade rápida e qualificada para fundição. Por exemplo, a plataforma de confiabilidade Caliber PERC aproveita as vantagens do escalonamento multi-threaded (MT) e flexível (MTflex) da plataforma Caliber, que distribui tarefas para várias CPUs e / ou máquinas remotas para fornecer execução rápida e eficiente dos processos de verificação em chips grandes e complexos como ICs AI / ML (Figura 2).

Figura 2. O dimensionamento flexível e multithread distribui tarefas para vários controles remotos para uma execução geral mais rápida.

Além dessa mecânica básica, mas essencial, a plataforma de confiabilidade do Calibre PERC oferece processamento inovador que combina netlist e informações de layout de um projeto para avaliar de forma rápida e precisa uma ampla gama de possíveis problemas de confiabilidade. Ao permitir que os designers reduzam com eficiência e confiança a suscetibilidade de um projeto a falhas operacionais e de desempenho, esta abordagem para verificação de confiabilidade avançada ajuda a apoiar o crescimento contínuo e a adoção de tecnologia confiável de AI / ML.

Confiabilidade no nível do transistor

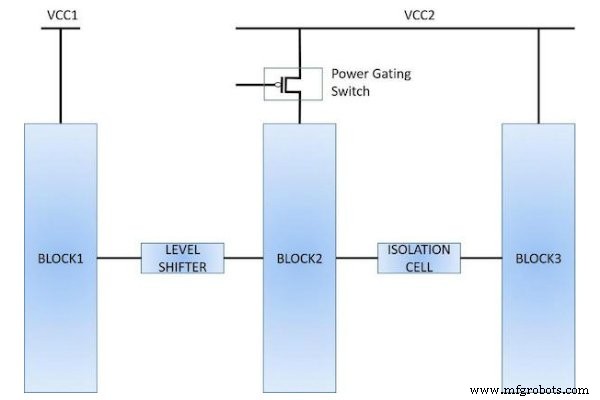

A maioria dos projetos de ML / AI usa vários domínios de energia para uma variedade de finalidades, como fornecer uma fonte de alimentação limpa e sem ruído para IP analógico, permitindo a capacidade de bloquear ou desligar a energia para uma determinada área de um chip, dimensionamento as tensões aumentam ou diminuem independentemente para IPs selecionados ou atendendo a altas demandas de corrente usando vários reguladores de tensão. Por exemplo, o processador Skylake da Intel contém nove domínios de potência primários.

A implementação de um projeto de domínio de potência múltipla requer o uso de elementos de circuito especiais, como reguladores de tensão, interruptores de cabeçalho e rodapé, deslocadores de nível, células de isolamento e células de retenção de estado. Esses elementos apresentam um conjunto único de desafios para verificação de confiabilidade. Por exemplo, os projetistas devem verificar se o deslocador de nível apropriado ou células de isolamento são usados em cada interface de domínio e se eles estão conectados corretamente (Figura 3).

Figura 3. O uso de elementos especiais (como deslocadores de nível, células de isolamento e interruptores de alimentação) dentro de um projeto de baixo consumo de energia requer técnicas de verificação especializadas.

Eles também devem garantir que estão usando os tipos apropriados de dispositivos em diferentes domínios de energia, como dispositivos de óxido espesso para fornecimento de alta tensão. Verificar essas condições requer conhecimentos e processos muito específicos.

A técnica do Unified Power Format

O formato de potência unificado (UPF) é uma técnica amplamente utilizada que permite aos designers empregar uma descrição consistente da intenção de potência em todo o fluxo do projeto. No entanto, os fluxos de verificação tradicionais baseados em UPF são usados para validar IPs no nível de lógica ou de porta, mas eles não têm a capacidade de validar as implementações finais de nível de transistor, particularmente as conexões de poço e em massa.

A plataforma de confiabilidade do Calibre PERC pode ler o arquivo UPF para um projeto e aproveitar as informações do UPF para realizar várias análises no nível do transistor, como identificar deslocadores de nível ausentes ou conectados incorretamente, condições de sobretensão elétrica (EOS), poços flutuantes e muito mais . Ao usar a plataforma de confiabilidade Caliber PERC em conjunto com os dados UPF, os designers podem avaliar as interações do dispositivo programaticamente para fornecer verificação de confiabilidade repetível e determinística.

Confiabilidade vitalícia de chips AI / ML

A segurança operacional é um aspecto crítico para a maioria dos chips AI / ML, que devem operar durante toda a vida útil projetada sem falhas ou falhas. Alguns problemas de confiabilidade elétrica, como instabilidade de temperatura de polarização (BTI) e EOS, podem não se manifestar como falhas imediatas, mas podem causar degradação rápida e envelhecimento ao longo do tempo se não forem corrigidos antes da fabricação. A verificação de confiabilidade pode ajudar a garantir uma operação robusta por um longo período, verificando vários problemas, como resistência ponto a ponto, BTI positivo e negativo, densidade de corrente e eletromigração (EM), todos os quais podem criar degradação de desempenho ou falha catastrófica.

Considere o caso em que um dispositivo de domínio de alta tensão está conduzindo um dispositivo de óxido fino que não é classificado para lidar com a alta tensão. Durante o projeto, o projetista falha ao inserir um deslocador de alto-baixo nível. Mesmo que esta condição não afete necessariamente a funcionalidade no início, ela estressará o dispositivo de óxido fino ao longo do tempo, eventualmente causando falha. O tempo de falha real depende do valor da tensão, do tempo em que a alimentação está LIGADA versus DESLIGADA e dos parâmetros do processo.

EM (a migração de átomos em um condutor devido à corrente elétrica) é outro grande problema que afeta a robustez de longo prazo das interconexões usadas em ICs AI / ML. Essa migração causa a formação de vazios e outeirinhos nos fios. Os vazios causam um aumento significativo na resistência, enquanto os morros podem criar curtos, os quais levam a falhas de circuito. O efeito EM é dependente de muitos fatores, como o comprimento e a largura da linha de metal, o material de interconexão, temperatura de operação, correntes unidirecionais vs. bidirecionais, etc.

As fundições fornecem às empresas de design limites EM para a corrente máxima que os fios podem suportar, com base nas condições de uso esperadas para o produto. Por exemplo, os limites de EM para um IC usado dentro de um telefone móvel seriam consideravelmente mais baixos do que para um IC usado em um ambiente industrial. Algumas empresas têm equipes dedicadas que se envolvem ativamente com a fundição para definir as especificações apropriadas, criar estruturas de teste e realizar a qualificação do produto para tolerância EM. Obviamente, é mais difícil definir esses limites para um produto que pode ser usado em vários ambientes, portanto, os designers normalmente projetam esses chips para as piores condições operacionais. Em todos os casos, é crucial testar o projeto em relação aos limites EM definidos pela fundição e validar se o projeto pode suportar os efeitos EM.

A falha em detectar e corrigir os diferentes problemas de confiabilidade durante a fase de verificação pré-silício pode resultar em uma ampla gama de impactos, incluindo múltiplas rotações de fita, atrasos na colocação do produto no mercado, perda de confiança do cliente, reação negativa significativa do mercado, recalls de produtos e até consequências catastróficas, como ferimentos físicos ou morte. Identificar e corrigir violações de confiabilidade antes da fita adesiva minimiza a chance de mau funcionamento ou falhas do circuito que podem ser caras.

A análise e o gerenciamento da confiabilidade da IA / ML são cruciais

O sucesso recente e a expansão da funcionalidade de AI / ML são amplamente baseados em avanços na tecnologia de semicondutores. À medida que esses novos designs são desenvolvidos, a comunidade de design de hardware deve estar ciente da necessidade de analisar e gerenciar os aspectos de confiabilidade de um design, como o ambiente alvo, condições operacionais, critérios de confiabilidade, etc. Poderosas ferramentas de verificação de confiabilidade EDA projetadas para abordar as questões específicas de confiabilidade e requisitos desses chips grandes e complexos podem ajudar as empresas de design a garantir que seus produtos tenham o desempenho esperado durante toda a vida útil projetada. Por sua vez, isso se traduz em confiança nos resultados alcançados com a utilização de aplicações AI / ML nos mercados mais amplos, suportando a sua utilização e expansão contínuas.

Artigos do setor são uma forma de conteúdo que permite aos parceiros do setor compartilhar notícias, mensagens e tecnologia úteis com os leitores do All About Circuits de uma forma que o conteúdo editorial não é adequado. Todos os artigos da indústria estão sujeitos a diretrizes editoriais rígidas com a intenção de oferecer aos leitores notícias úteis, conhecimentos técnicos ou histórias. Os pontos de vista e opiniões expressos nos Artigos da Indústria são do parceiro e não necessariamente da All About Circuits ou de seus redatores.

Tecnologia da Internet das Coisas

- A Importância da Segurança Elétrica

- Qual é a função do engenheiro de confiabilidade?

- A chave nº 1 para o sucesso da confiabilidade

- A importância das competências essenciais

- O lado não técnico da confiabilidade

- A importância das tendências na confiabilidade do motor elétrico

- A importância da manutenção de rotina no equipamento

- A importância da usinagem rápida na fabricação

- A importância da análise da causa raiz

- A importância do planejamento de contingência