Desempenho analógico / RF do transistor de efeito de campo de túnel de fonte dupla com porta em forma de T

Resumo

Neste artigo, um transistor de efeito de campo de túnel de fonte dupla com porta em forma de T (TGTFET) baseado em silício é proposto e investigado por simulação TCAD. Como um estudo contrastivo, a estrutura, as características e o desempenho analógico / RF do TGTFET, LTFET e UTFET são discutidos. A sobreposição da porta introduzida pela porta em forma de T pode aumentar a eficiência da junção de tunelamento. As regiões de fonte dupla no TGTFET podem aumentar a corrente no estado ( I LIGADO ), oferecendo uma área de junção de túnel dupla. A fim de melhorar ainda mais o desempenho do dispositivo, o n + pocket é introduzido no TGTFET para aumentar ainda mais a taxa de tunelamento banda a banda. Os resultados da simulação revelam que o I do TGTFET LIGADO e relação de comutação ( I LIGADO / eu DESLIGADO ) alcance 81 μA / μm e 6,7 × 10 10 na porta de 1 V para a tensão da fonte ( V g ) A oscilação média de subliminar de TGTFET (SS média , de 0 a 0,5 V V g ) atinge 51,5 mV / dec, e a oscilação mínima de subliminar de TGTFET (SS min , a 0,1 V V g ) atinge 24,4 mV / dec. Além disso, verificou-se que o TGTFET tem forte robustez no efeito de redução da barreira induzida pelo dreno (DIBL). Os efeitos da concentração de dopagem, dimensão geométrica e tensão aplicada no desempenho do dispositivo são investigados a fim de criar a diretriz de projeto do TGTFET. Além disso, a transcondutância ( g m ), condutância de saída ( g ds ), capacitância de porta para fonte ( C gs ), porta para drenar capacitância ( C gd ), frequência de corte ( f T ), e a largura de banda de ganho (GBW) do TGTFET atinge 232 μS / μm, 214 μS / μm, 0,7 fF / μm, 3,7 fF / μm, 3,7 fF / μm, 11,9 GHz e 2,3 GHz a 0,5 V dreno para a tensão de fonte ( V d ), respectivamente. Beneficiando-se da vantagem estrutural, o TGTFET obtém melhores características DC / AC em comparação com o UTFET e o LTFET. Em conclusão, o bom desempenho considerável torna o TGTFET uma escolha muito atraente para a próxima geração de aplicações de baixa potência e analógicas / RF.

Histórico

A redução da escala dos transistores de efeito de campo semicondutores de óxido metálico (MOSFETs) traz uma melhora significativa no consumo de energia do circuito integrado (IC), nas características de comutação, na função do circuito e na densidade do IC [1, 2]. Mas a contradição irreconciliável entre o escalonamento da tensão de alimentação e a redução das correntes de fuga fora do estado ( I DESLIGADO ) finalmente resultará no alto consumo de energia inaceitável [3]. Ao mesmo tempo, a degradação da confiabilidade causada por efeitos de canal curto (SCEs) torna-se cada vez mais séria [4, 5]. Para resolver esses problemas, é válido reduzir a oscilação de sublimiar (SS) e a tensão de alimentação dos dispositivos. Com base no mecanismo de tunelamento banda a banda, os transistores de efeito de campo de túnel (TFETs) alcançam a oscilação subliminar (SS) menor que 60 mV / dec e podem efetivamente reduzir a tensão de alimentação [6,7,8,9,10] . Além disso, devido à existência da junção de tunelamento perto da fonte, o TFET geralmente tem uma pequena porta para a capacitância da fonte ( C gs ) [1, 11], o que é benéfico para o desempenho da frequência do dispositivo.

Estudos recentes mostram que o TFET parece ser um candidato promissor para futuras aplicações de baixa potência [12,13,14,15,16] e aplicações analógicas / RF [17,18,19]. No entanto, devido à pequena área de tunelamento efetiva, a corrente de tunelamento limitada torna-se uma desvantagem inerente no TFET P-I-N convencional, o que leva a uma corrente operacional baixa no estado ( I LIGADO ) A fim de melhorar o desempenho do TFET, muitas novas estruturas foram propostas nos últimos anos [20,21,22,23,24,25]. Beneficiando-se da porta recuada, o transistor de efeito de campo em túnel em forma de L (LTFET) [23, 24] e o transistor de efeito de campo em túnel em forma de U (UTFET) [25] foram propostos para obter I LIGADO com uma estrutura de dispositivo compacta. No entanto, ainda há muito espaço para melhorias no LTFET e UTFET e é necessário despender mais esforços para estudar o desempenho analógico / RF desses dispositivos.

Neste artigo, um transistor de efeito de campo de túnel de fonte dupla com porta em forma de T (TGTFET) com fonte dupla é apresentado e estudado por simulação TCAD. O TGTFET projetado pode dobrar a área de junção de tunelamento em comparação com LTFET e UTFET. A sobreposição de porta introduzida pela porta em forma de T projetada pode aumentar a taxa de tunelamento banda a banda (taxa BBT). Os resultados da simulação mostram que o TGTFET proposto ganha um maior I LIGADO (8,1 × 10 - 5 A / μm em V d =1 V) do que o LTFET e o UTFET nas mesmas condições. Ambos SS min (em V g =0,1 V) e o SS avg (0 ~ 0,5 V V g ) de TGTFET são inferiores a 60 mV / dec (24,4 mV / dec e 51,5 mV / dec, respectivamente). TGTFET ganha melhor característica de entrada / saída ( g m =232 μS / μm, g ds =214 μS / μm) do que o UTFET e o LTFET. Além disso, as características de capacitância de TGTFET, UTFET e LTFET são discutidas em detalhes. Finalmente, o TGTFET ganha melhor desempenho analógico / RF ( f T =11,9 GHz e GBW =2,3 GHz) em comparação com UTFET e LTFET. Como resultado, TGTFET com desempenho considerável pode ser obtido. As estruturas deste artigo são as seguintes:a seção “Métodos” inclui a descrição da estrutura e os parâmetros de TGTFET, LTFET [23, 24] e UTFET [25 ] bem como os métodos de simulação TCAD. A seção “Resultados e Discussão” inclui a descrição dos resultados da simulação. Nesta seção, o mecanismo, a característica e o desempenho analógico / RF do TGTFET são estudados e comparados com o LTFET e o UTFET. A influência dos parâmetros do dispositivo no TGTFET também é analisada em detalhes. A seção “Conclusões” apresenta uma conclusão deste artigo.

Métodos

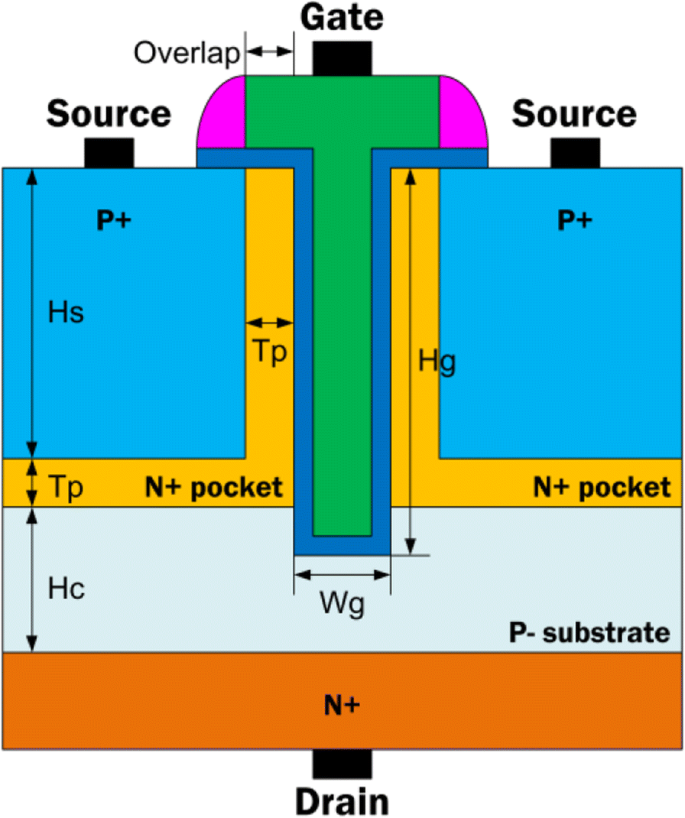

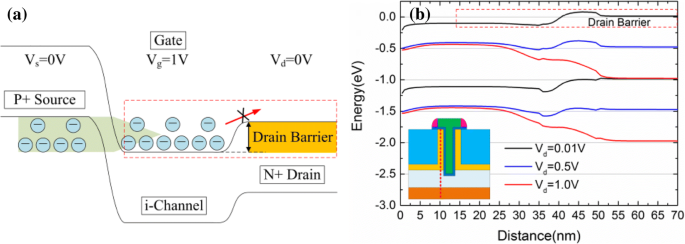

A estrutura do transistor de efeito de campo de túnel de fonte dupla com porta em forma de T (TGTFET) é ilustrada na Fig. 1. A forma da porta é semelhante à letra do alfabeto “T” (região verde). As regiões de fonte dupla estão localizadas nos dois lados do portão (regiões de safira). Dois n + bolsos (regiões amarelas) são inseridos para aumentar a taxa de tunelamento do canal [20,21,22]. O dreno n + é colocado na parte inferior do canal. Portanto, a porta em forma de T se sobrepõe aos bolsos n + nas direções vertical e lateral. Desta forma, o campo elétrico no topo da junção de tunelamento pode ser aumentado. O aumento do campo elétrico faz com que a faixa de energia se curve de forma mais abrupta. Finalmente, a taxa de tunelamento de elétrons é aumentada devido ao aumento do campo elétrico de canto [26].

Esquema do transistor de efeito de campo de túnel de fonte dupla de porta em forma de T proposto (TGTFET)

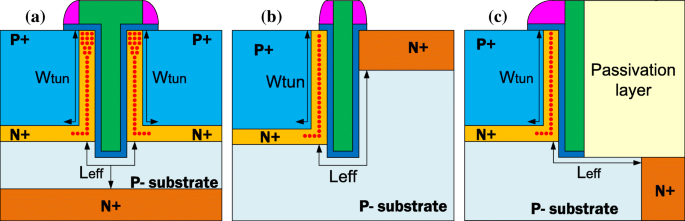

A Figura 2 mostra a estrutura do dispositivo de LTFET [23, 24], UTFET [25] e TGTFET. A sobreposição da porta pode ajudar a aumentar a eficiência de tunelamento do TGTFET. As regiões de fonte dupla em TGTFET podem dobrar a área de junção de tunelamento em comparação com LTFET e UTFET.

Comparação de a o TGTFET proposto, b UTFET e c LTFET

Os parâmetros de TGTFET, UTFET e LTFET à base de silício usados nas simulações são os seguintes:Hs =30 nm (altura da região de origem), Hg =40 nm (altura da porta recuada), Wg =6 nm (largura do região da porta), Hc =15 nm (altura da região do canal), Tp =5 nm (espessura da bolsa n +), ϕ =4 . 33 eV (função de trabalho do portão), Tox =2 nm (espessura do HfO 2 porta dielétrica), N S =1 × 10 20 cm −3 (p + concentração de dopagem da fonte), N D =1 × 10 19 cm −3 (concentração de dopagem n + dreno), N sub =1 × 10 17 cm −3 (concentração de dopagem de substrato p), e N P =5 × 10 18 cm −3 (concentração de n + pocket doping). O coeficiente de largura na simulação é padrão em 1 μm.

Simulações de TGTFET, UTFET e LTFET são realizadas nas ferramentas Silvaco Atlas TCAD. O modelo BTBT não local é apresentado nesta simulação para levar em consideração a variação espacial da banda de energia, o que pode ajudar a facilitar a precisão do processo de tunelamento BTBT. O modelo de mobilidade Lombardi é considerado para tornar a mobilidade do canal mais precisa (considerando o espalhamento da superfície incluindo o campo transversal e a concentração de dopagem). As estatísticas de Fermi e o modelo de redução do gap são levados em consideração para ajustar o efeito das regiões altamente dopadas. O modelo de recombinação Shockley-Read-Hall também é levado em consideração neste artigo.

Resultados e discussão

Mecanismo do dispositivo e características DC com parâmetros diferentes

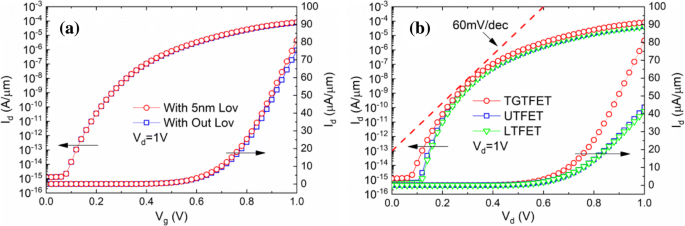

A Figura 3a mostra as características de transferência do TGTFET com e sem a sobreposição de porta. Com a sobreposição de portão adicional, o I LIGADO aumenta de 7,5 × 10 −5 para 8,1 × 10 −5 A / μ m em V g = V d =1 V. A Figura 3b mostra as curvas características de transferência de TGTFET, UTFET e LTFET. Para tornar a comparação mais precisa, os modelos de simulação e as dimensões geométricas desses três dispositivos devem ser idênticos. Como resultado, o TGTFET tem um aumento de cerca de duas vezes em I LIGADO em comparação com LTFET e UTFET, como mostrado na Fig. 3b. SS min do TGTFET é 24,4 mV / dez a V g =0,1 V, e SS média é 51,5 mV / dec quando 0 V < V g <0,5 V. As relações de comutação ( I LIGADO / eu DESLIGADO ) são 6,7 × 10 10 em V g = V d =1 V e 6,5 × 10 8 em V g = V d =0,5 V.

Simulado a características de transferência de TGTFET com / sem sobreposição de porta e b transferir características de TGTFET, UTFET e LTFET

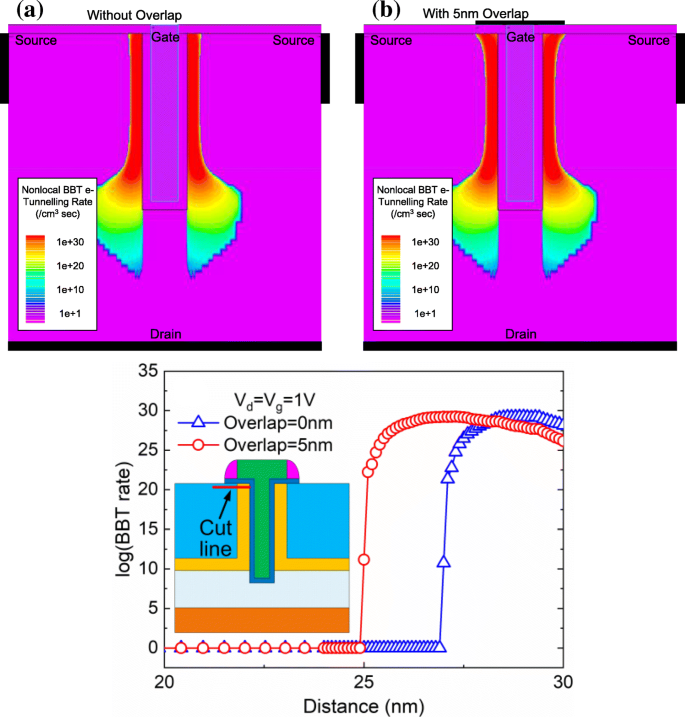

A Figura 4a, b mostra a taxa de BBT de TGTFET com e sem uma sobreposição de porta de 5 nm. Na Fig. 4c, podemos ver claramente que o dispositivo com uma sobreposição de porta de 5 nm tem uma área de tunelamento de elétrons mais ampla sob a superfície do dispositivo, o que pode levar ao I LIGADO aumentando.

Diagramas de taxa de tunelamento de elétrons simulados BBT de a dispositivo sem sobreposição de portão, b dispositivo com sobreposição de porta de 5 nm e c a taxa de tunelamento de elétrons BBT de dois dispositivos, a 1 nm abaixo da superfície do dispositivo; V g = V d =1 V

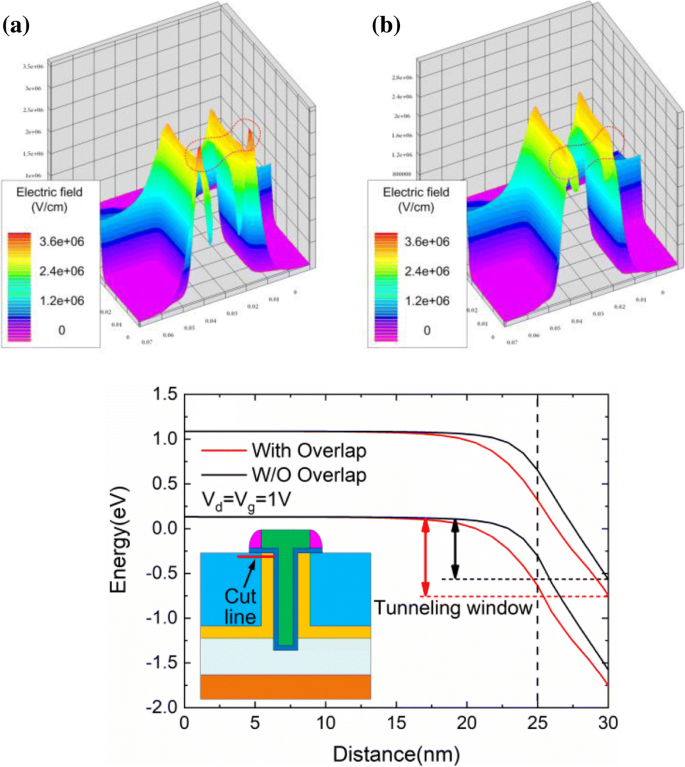

A Figura 5a, b mostra o diagrama 3D dos campos elétricos do TGTFET com e sem sobreposição de porta. Dois picos de campo elétrico aparecem no TGTFET com uma sobreposição de porta de 5 nm, como mostrado no círculo tracejado na Fig. 5a. Nenhum pico de campo elétrico aparece na Fig. 5b atribuído às ausências da sobreposição do portão. A Figura 5c mostra a estrutura da banda de energia sob a superfície do dispositivo. A inserção na Fig. 5c mostra a localização da linha de corte. Com a sobreposição do portão, uma janela de túnel maior pode ser obtida. Assim, uma taxa de BBT mais alta e I LIGADO pode ser conseguida.

Diagrama esquemático 3D dos campos elétricos do dispositivo a com sobreposição e b sem sobreposição; simulado c diagramas de banda de energia da fonte para a região do bolso (1 nm abaixo da interface de óxido)

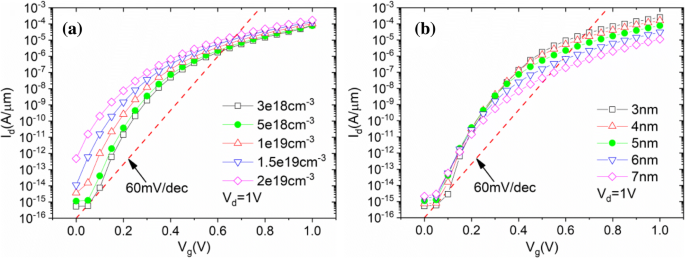

A Figura 6 mostra os efeitos de n + pocket no desempenho do TGTFET. O eu DESLIGADO aumenta rapidamente com o aumento da concentração de dopagem de bolso n +, como mostrado na Fig. 6a. O SS inferior e superior I LIGADO pode ser obtido diminuindo a espessura de n + bolsão (Tp) de 7 para 3 nm quando N P =5 × 10 18 cm −3 , conforme mostrado na Fig. 6b. Ao mesmo tempo, nenhuma corrente subliminar significativa é observada na Fig. 6b. Pode ser confirmado pela Fig. 6a que uma concentração de dopagem relativamente baixa de n + pocket ajudará a suprimir a corrente subliminar.

Correntes de drenagem simuladas com bolsão n + diferente a concentrações e b espessuras em V d =1 V

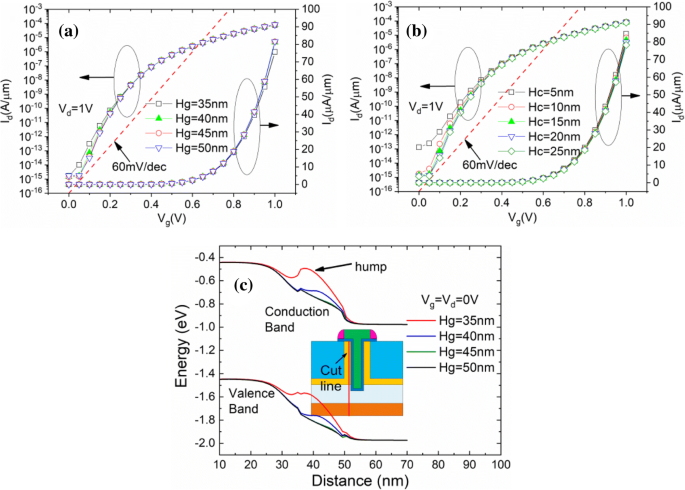

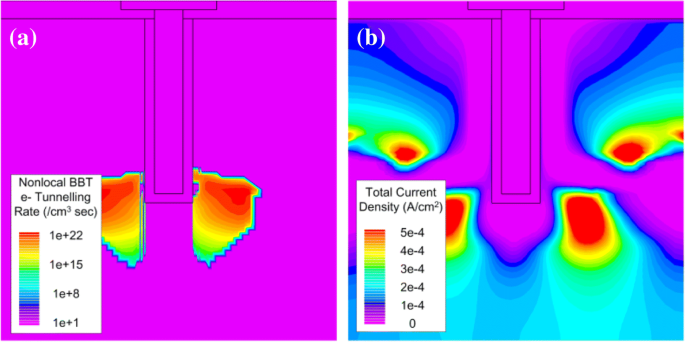

O impacto da altura do portão (Hg) e da espessura do canal (Hc) é mostrado na Fig. 7a, b, separadamente. Um pequeno eu LIGADO e a melhora do SS aparece quando o Hg está aumentando. Porque quando Hg =35 nm, há um óbvio aumento da banda de energia no caminho da corrente no estado ligado, tornando-se um certo obstáculo para os elétrons da sorte (elétrons que passaram pela junção de tunelamento), como mostrado na Fig. 7c, o que pode resultar em eu em diminuir. Quando o Hg aumenta, o aumento da banda de energia é enfraquecido, o que causa o I LIGADO e melhoria de SS. Um leve eu LIGADO a melhora é obtida com a diminuição de Hc, conforme mostrado na Fig. 7b. No entanto, a degradação severa na característica subliminar pode ser observada quando o Hc diminui para 5 nm. Isso pode ser explicado pelo aumento da corrente de tunelamento subliminar no canto do bolsão n +, como mostrado na Fig. 8. A Figura 8a mostra o óbvio fenômeno de tunelamento banda a banda fora do estado quando Hc =5 nm, enquanto a Fig. 8b mostra o eu DESLIGADO densidade de corrente quando Hc =5 nm.

Características de transferência simulada de TGTFET com a Hg diferente, b Hc diferente e c a curva da banda de condução no caminho atual

Diagramas simulados de estado desligado a Taxa de tunelamento de elétrons BTBT e b densidade de corrente quando Hc =5 nm

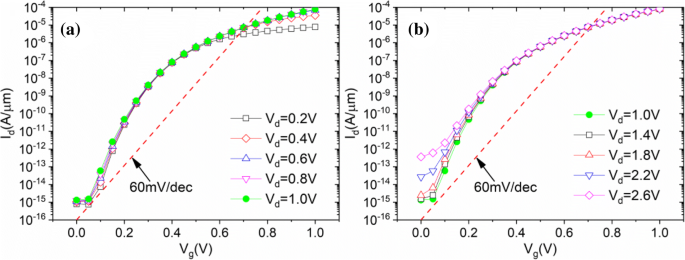

Conforme mostrado na Fig. 9, a influência do dreno para a tensão da fonte ( V d ) também é levado em consideração neste artigo. Para V d <0,6 V, I LIGADO aumenta obviamente com o aumento de V d , como mostrado na Fig. 9a. Isso é explicado pelo fato de que o potencial do canal p está crescendo lentamente em resposta ao aumento de V d e resulta na diminuição da resistência do canal p. Para V d > 1,8 V, mostrado na Fig. 9b, o I LIGADO quase não aumenta com o aumento de V d , mas eu DESLIGADO aumenta consideravelmente. Isso ocorre porque a corrente de tunelamento subliminar no canto do bolsão n + aumenta rapidamente com o aumento de V d . Finalmente, para 0,6 V < V d <1,8 V, o TGTFET exibe um desempenho bom e estável. Como resultado, o TGTFET é robusto para redução da barreira induzida pelo dreno (DIBL) e exibe um desempenho bom e estável em uma faixa dinâmica de tensão aplicada maior.

Correntes de drenagem simuladas para a V d ≤ 1 V e b V d ≥ 1 V

Desempenho analógico / RF de TGTFET, UTFET e LTFET

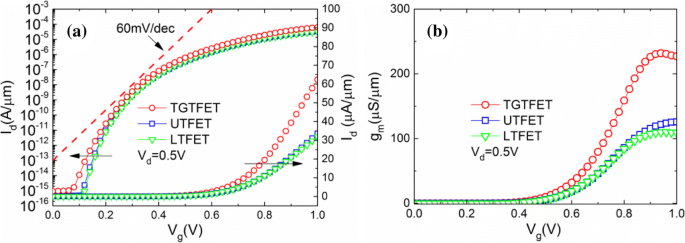

A Figura 10 mostra as características de transferência e curvas de transcondutância de TGTFET, UTFET e LTFET em V d =0,5 V. A transcondutância ( g m ) pode ser obtida a partir da primeira derivada da curva característica de transferência, conforme mostrado na Eq. (1) [27,28,29]:

$$ {g} _ {\ mathrm {m}} ={dI} _ {\ mathrm {d} s} / {dV} _ {\ mathrm {gs}} $$ (1)

a Características de transferência e b curvas de transcondutância de TGTFET, UTFET e LTFET em V d =0,5 V

Como resultado, a transcondutância máxima de TGTFET (232 μS / μm) é cerca de duas vezes maior do que a de UTFET (120 μS / μm) e LTFET (110 μS / μm), conforme mostrado na Fig. 10. Isso é beneficiado por o ganho atual contribuído pela fonte dupla e sobreposição de porta.

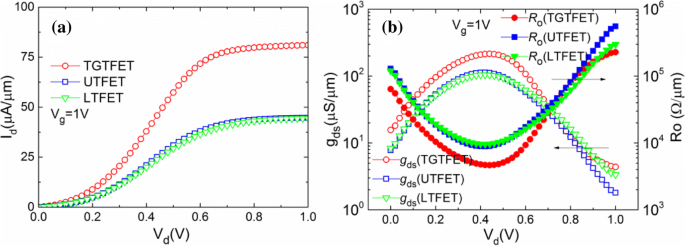

A Figura 11 mostra as características de saída, condutância de saída ( g ds ), e impedância de saída ( R o ) curvas do TGTFET, UTFET e LTFET. Conforme mostrado na Fig. 11a, pode ser visto claramente que a corrente de saída do dispositivo aumenta com o aumento de V d , mas quando V d atinge acima de 0,6 V, a corrente de saída tende a saturar. Por meio da observação, é fácil descobrir que a corrente de saída do TGTFET é duas vezes maior do que a do UTFET e do LTFET. A Figura 11b mostra a condutância de saída ( g ds ) e impedância de saída ( R o ) curvas do TGTFET, UTFET e LTFET. O g ds pode ser obtido por meio da derivação da corrente de saída, conforme mostrado na Eq. (2) [27, 29] enquanto R o pode ser expresso como o recíproco da condutância de saída.

$$ {g} _ {\ mathrm {ds}} ={dI} _ {\ mathrm {ds}} / {dV} _ {\ mathrm {ds}} $$ (2)

a Características de saída, b condutância de saída ( g ds ), e c impedância de saída ( R o ) curvas do TGTFET, UTFET e LTFET

Devido às vantagens na corrente de saída, o TGTFET ganha o maior g ds e o mínimo R o desses três dispositivos. Sob condição de polarização de porta 1-V, o TGTFET obteve o máximo g ds de 214 μS / μm e o mínimo R o de 4,6 kΩ / μm sob 0,45 V V d . Sob a mesma condição de polarização de porta, UTFET e LTFET obtiveram o máximo g ds de 113 μS / μm e 105 μS / μm e o mínimo R o de 9,0 kΩ / μm e 9,6 kΩ / μm sob 0,4 V V d .

Além disso, na Fig. 11, não é difícil descobrir que a região linear das características de saída do dispositivo mostra certa não linearidade. Conforme mostrado na Fig. 11a, R o diminui primeiro e depois aumenta com o aumento de V d . Alguns grupos de pesquisa fornecem o processo físico correspondente sobre este fenômeno [7, 30], mas ainda existem alguns problemas que não foram explicados claramente. Como sabemos, R o é determinado pela resistência da região do canal e junção de tunelamento. Quando V d <0,4 V, R o diminui com o aumento de V d . Considere as seguintes situações, quando V d =0 V e V g =1 V, nenhum dos elétrons da sorte pode ser varrido para o lado do dreno, e quase todos os elétrons são aprisionados na região do canal por uma barreira de dreno relativamente alta, como mostrado no quadro da linha pontilhada vermelha na Fig. 12a, b. Quando 0 V < V d <0,4 V, com o aumento de V d , a barreira de drenagem se torna mais fraca (como mostrado na Fig. 12b). Assim, os elétrons presos na região do canal podem passar pela barreira do dreno e, então, ser coletados pelo dreno. Este é um processo de excitação térmica de elétrons do canal ao dreno. Finalmente, como a junção de tunelamento foi completamente ligada (quando V g =1 V), a corrente de tunelamento está sempre em excesso e a resistência introduzida pela junção de tunelamento pode ser ignorada. Neste momento, R o é determinado pela resistência do canal e R o é decidido pelo processo de excitação térmica do elétron através da barreira do dreno. Assim, R o diminui com o aumento de V d . Quando V d > 0,6 V, esses três dispositivos gradualmente entram na área de saturação e R o torna-se maior. Isso ocorre porque quando V d é grande, quase todos os elétrons através da junção de tunelamento são arrastados para o lado do dreno pelo campo elétrico relativamente alto. A corrente de tunelamento torna-se o limite da corrente de dreno. Nesta condição, R o é determinado principalmente pela junção de tunelamento. No entanto, a eficiência do tunelamento não pode aumentar significativamente enquanto V d está aumentando. V d tem um pequeno efeito na estrutura da banda de energia da junção de tunelamento (n + bolsão lateral), conforme mostrado na Fig. 12b. Como resultado, a corrente de tunelamento não pode aumentar obviamente, e quase não há I LIGADO aumentar com o aumento contínuo de V d (quando V d > 0,6 V), o que significa que a impedância aumenta. Além disso, quando 0,4 V < V d <0,6 V, R o é determinado tanto pela resistência do canal quanto pela junção de tunelamento.

a Diagrama esquemático da banda de energia em V d =0 V e V g =1 V. b Resultados da simulação do diagrama de banda de energia em diferentes vieses de V d

Pode ser obtido a partir da análise acima que o R o de TFET é influenciado tanto pelo processo de tunelamento quanto pelo processo de excitação térmica de elétrons do canal. Os principais mecanismos físicos podem dominar R o muda com V d variação. Finalmente, o R o diminui primeiro e depois aumenta, causando a não linearidade das características de saída. A propósito, através da observação da Fig. 11b, é fácil descobrir que a impedância de saída do TGTFET é muito menor do que a do UTFET e do LTFET. Isso se deve ao melhor benefício de eficiência de tunelamento da fonte dupla e da estrutura de sobreposição de porta lateral do TGTFET.

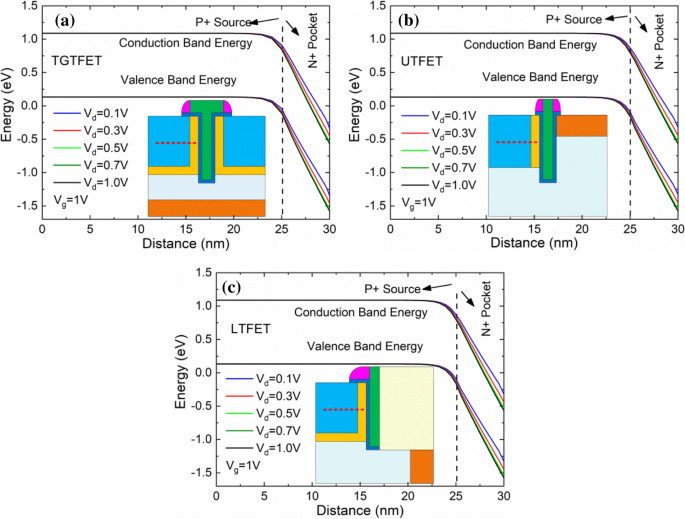

A Figura 13 mostra a estrutura da banda de energia do TGTFET, UTFET e LTFET com diferentes tensões aplicadas. As linhas vermelhas pontilhadas na inserção representam a posição para desenhar a banda de energia (que está 15 nm abaixo da superfície, apenas na metade da altura da região da fonte). Pode-se ver que com um V d aumentar de 0,1 para 0,5 V, a estrutura de banda de TGTFET, UTFET e LTFET tem uma tendência óbvia de flexão. Isso ocorre porque a tensão do dreno pode reduzir o potencial elétrico da junção do túnel perto do lado do dreno. Isso indica que, para TGTFET, UTFET e LTFET, o aumento de V d de 0,1 a 0,5 V é benéfico para a eficiência do tunelamento. No entanto, quando V d > 0,5 V, a mudança da banda de energia com V d aumento não vale a pena mencionar. Isso é consistente com os resultados da análise na Fig. 12b.

A estrutura da banda de energia de a TGTFET, b UTFET e c LTFET em V g =1

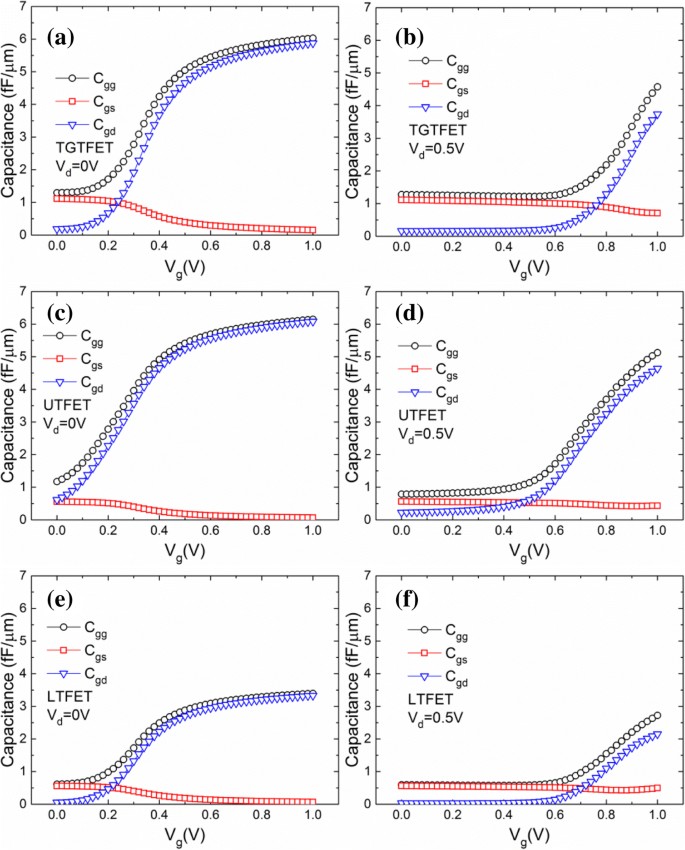

Como sabemos, a capacitância da porta ( C gg ) do dispositivo pode afetar significativamente as características de frequência dos circuitos integrados. Para TGTFET, UTFET e LTFET, C gg geralmente consiste em C gs (capacitância da porta para a fonte) e C gd (porta para drenar capacitância). Portanto, a característica de C gg , C gs e C gd é de grande importância para avaliar as características de frequência e capacidade de aplicação analógica dos dispositivos. Especialmente para TFET, as características de capacitância são bastante diferentes do MOSFET. Devido à existência de junção de tunelamento na área de origem, TFET geralmente tem um pequeno C gs [1,11]. Portanto, o C gg do TFET é determinado principalmente por C gd . A Figura 14 mostra a capacitância de TGTFET, UTFET e LTFET versus V g sob V d =0,5 V e V d =0 V, separadamente.

Capacitância de TGTFET versus V g sob a V d =0 V e b V d =0,5 V. Capacitância de UTFET versus V g sob c V d =0 V e d V d =0,5 V. Capacitância de LTFET versus V g sob e V d =0 V e f V d =0,5 V

Através da observação da Fig. 14a, b, é fácil descobrir que o C gs de TGTFET sob tensão de porta de 1 V é 0,15 fF / μm em V d =0 V e 0,7 fF / μm em V d =0,5 V, que é muito mais menor do que C gd (5,8 fF / μm em V d =0 V e 3,7 fF / μm em V d =0,5 V). Assim, o C gg do TGTFET é determinado principalmente por C gd . Quando V d =0 V, C gg e C gd aumenta rapidamente com o aumento de V g , como mostrado na Fig. 14a. Isso porque com o aumento de V g , os elétrons são agregados à interface da porta no canal do dispositivo, o que faz com que a capacitância aumente rapidamente. Quando V d =0,5 V, C gd não aumenta obviamente até V g é aumentado para mais de 0,6 V, conforme mostrado na Fig. 14b. Isso ocorre porque quando V g é baixo, apenas alguns elétrons da sorte podem passar pela junção de tunelamento e entrar no canal. Alguns desses elétrons da sorte participarão do processo de recombinação, e a maioria dos outros será rapidamente coletada pelo dreno devido à tensão de dreno de 0,5 V. Portanto, é muito difícil para esses elétrons da sorte permanecerem no canal do dispositivo. No entanto, com o V g aumentar, o número de elétrons da sorte aumenta rapidamente. Neste momento, nem a coleta de dreno nem o processo de recombinação elétron-buraco podem esgotar rapidamente esses elétrons da sorte. Assim, a concentração de elétrons no canal aumenta e a capacitância aumenta rapidamente. Como resultado, a curva característica da capacitância tende a se deslocar para a direita enquanto V d aumenta, como mostrado na Fig. 14a, b. A análise e os fenômenos acima também são aplicáveis ao UTFET e LTFET, conforme mostrado na Fig. 14c-f. Além disso, a capacitância da porta do UTFET em 0 V e 0,5 V V d atingiu 6,2 fF / μm e 5,1 fF / μm, respectivamente, e o do LTFET atingiu 3,4 fF / μm e 2,7 fF / μm, respectivamente.

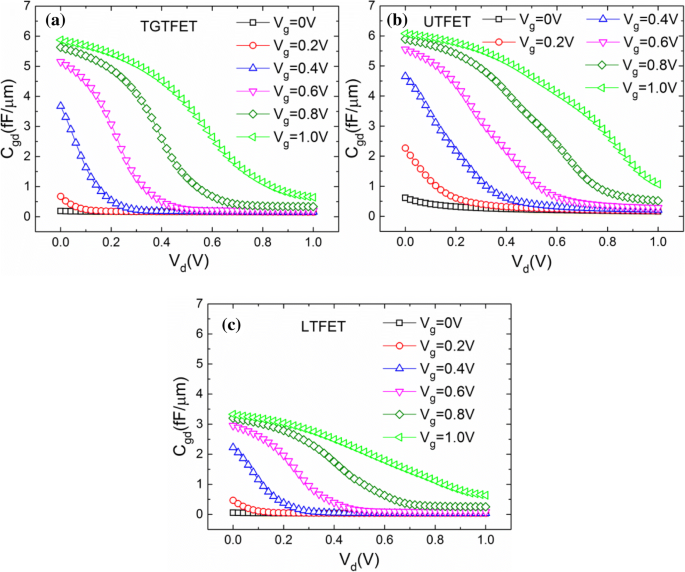

Como não há sobreposição direta entre a porta e o dreno do LTFET e a distância entre a porta e o dreno é relativamente grande, o LTFET tem as melhores características de capacitância e o menor C gg . Em contraste, há uma sobreposição direta entre a porta e o dreno do UTFET. Portanto, os elétrons próximos ao lado do dreno são mais facilmente controlados pelo portão, resultando em um grande C gg de UTFET. Para o TGTFET, embora a distância entre a porta e o dreno seja pequena, há uma região de canal levemente dopada que pode isolar a porta e o dreno. Assim, a capacitância do TGTFET é melhor do que a do UTFET, mas ligeiramente inferior à do LTFET. A Figura 15 mostra o C gd características de TGTFET, UTFET e LTFET versus V d sob diferentes V g . A partir da observação da Fig. 15a-v, não é difícil descobrir que o C gd as características desses três dispositivos são semelhantes. Ou seja, para um V fixo g , C gd diminui com o aumento do V d . Por outro lado, para um V fixo d , C gd aumenta com o aumento de V g .

C gd características de a TGTFET, b UTFET e c LTFET versus V d sob diferentes V g

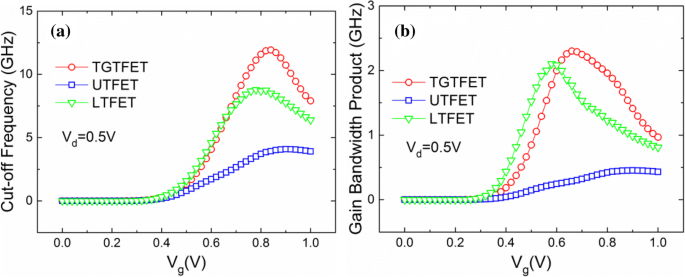

Como sabemos, tanto da frequência de corte ( f T ) e largura de banda de ganho (GBW) são os critérios de avaliação para avaliar as características de frequência dos dispositivos. f T depende da proporção de g m para C gg , conforme mostrado na Eq. (3) [30, 31]. Para um certo ganho DC igual a 10, GBW pode ser expresso pela proporção de g m para C gd , conforme mostrado na Eq. (4) [17]:

$$ {f} _T =\ frac {g _ {\ mathrm {m}}} {2 \ pi {C} _ {\ mathrm {gs}} \ sqrt {1 + 2 {C} _ {\ mathrm {gd} } / {C} _ {\ mathrm {gs}}}} \ approx \ frac {g _ {\ mathrm {m}}} {2 \ pi \ left ({C} _ {\ mathrm {gs}} + {C } _ {\ mathrm {gd}} \ right)} =\ frac {g _ {\ mathrm {m}}} {2 \ pi {C} _ {\ mathrm {gg}}} $$ (3) $$ \ mathrm {GWB} ={g} _ {\ mathrm {m}} / 2 \ pi 10 {C} _ {\ mathrm {gd}} $$ (4)

A Figura 16 mostra as curvas características do f T e GBW de TGTFET, UTFET e LTFET. Beneficiando-se de vantagens estruturais, como fonte dupla e sobreposição de porta lateral introduzida pela porta em forma de T, o TGTFET obtém as características de frequência mais destacadas em comparação com UTFET e LTFET. Sob a condição de V d =0,5 V, o f T e o GBW do TGTFET atingiu os valores máximos de 11,9 GHz e 2,3 GHz, respectivamente. Benefiting from the long distance between gate and drain and without gate/drain overlap, LTFET obtains a small C gg and good frequency characteristics. The f T and GBW of LTFET reach the 8.7 GHz and 2.1 GHz, separately. The capacitance characteristics of UTFET are inferior compared with that of TGTFET and LTFET. This is because the direct gate/drain overlaps. As a result, the maximum value of f T and GBW of UTFET can only reach 4.1 GHz and 0.5 GHz separately.

The characteristic curves of a f T and b GBW of TGTFET, UTFET, and LTFET versus V g at V d = 0.5 V

Conclusions

In this paper, a T-shape gate dual-source tunnel field-effect transistor (TGTFET) with good performance is proposed and investigated. The structure, mechanism, and the influence of device parameter on the characteristic of TGTFET are discussed. In addition, the characteristics of TGTFET, UTFET, and LTFET are discussed and compared in this paper. The dual-source regions are introduced to double the area of the tunneling junction. The gate overlap and the n+ pockets can obviously enhance the tunneling efficiency of the tunneling junction in TGTFET. Finally, the TGTFET with impressive characteristics (I ON = 8.1 × 10 −5 A/μm, I ON / eu OFF = 6.7 × 10 10 and SSmin = 24.4 mV/dec) is obtained. At the same time, TGTFET is robust to DIBL, which means TGTFET can exhibit a good and stable performance in a larger applied voltage dynamic range. Furthermore, the analog/RF performance of TGTFET is studied and compared with UTFET and LTFET. The key parameter such as input/output characteristics, capacitance characteristics, GBW, and f T are analyzed. Benefiting from the no direct overlap between the gate and drain, TGTFET obtains a relatively small C gd and C gg . Finally, TGTFET with remarkable frequency characteristics (f T = 11.9 GHz and GBW = 2.3 GHz) is obtained. As a conclusion, it is expected that TGTFET can be one of the promising alternatives for the next generation of device in low-power and analog/RF applications.

Abreviações

- C gd :

-

Gate to drain capacitance

- C gs :

-

Gate to source capacitance

- f T :

-

Cut-off frequency

- GBW:

-

Gain bandwidth

- g ds :

-

Output conductance

- g m :

-

Transconductance

- Hc:

-

Height of the channel layer

- Hg:

-

Height of the gate electrode

- Hs:

-

Height of the source layer

- LTFET:

-

L-shape gate tunnel field-effect transistor

- N D :

-

Doping concentration of n+ drain

- N P :

-

Doping concentration of n+ pocket

- N S :

-

Doping concentration of p+ source

- N sub :

-

Doping concentration of p− substrate

- R o :

-

Output impedance

- TGTFET:

-

T-shape gate dual-source tunnel field-effect transistor

- Tox:

-

Thickness of the HfO2 gate dielectric

- Tp:

-

Thickness of n+ pocket

- UTFET:

-

U-shape gate tunnel field-effect transistor

- V d :

-

Drain to source voltage

- V g :

-

Gate to source voltage

- Wg:

-

Width of the gate electrode

Nanomateriais

- Transistores, efeito de campo de junção (JFET)

- Transistores, efeito de campo de porta isolada (IGFET ou MOSFET)

- Transistores de efeito de campo de junção

- Transistores de efeito de campo de porta isolada (MOSFET)

- O Transistor de efeito de campo de junção (JFET) como uma chave

- Túnel

- Primeiro transistor de temperatura ambiente ultrarrápido totalmente ótico do mundo

- Desempenho fotocatalítico acionado por luz visível de nanocompósitos N-dopados com ZnO / g-C3N4

- Preparação e desempenho fotocatalítico de fotocatalisadores de estrutura oca LiNb3O8

- Um romance fotocatalisador de heterojunção Bi4Ti3O12 / Ag3PO4 com desempenho fotocatalítico aprimorado