Ge pMOSFETs de alta mobilidade com dielétrico ZrO2:Impactos do pós-recozimento

Resumo

Este artigo investiga os impactos do recozimento pós-metal (PMA) e recozimento pós-deposição (PDA) no desempenho elétrico de transistores de efeito de campo semicondutores de óxido metálico tipo p (pMOSFETs) com ZrO 2 dielétrico. Para os transistores sem PDA, corrente no estado ( I LIGADO ), oscilação subliminar (SS) e características de espessura equivalente de capacitância (CET) são melhoradas com o aumento da temperatura do PMA de 350 para 500 ° C. Cristalização de ZrO 2 dielétrico na temperatura PMA mais alta contribui para o aumento da permissividade de ZrO 2 e a diminuição da densidade dos estados da interface ( D it ), resultando em um CET reduzido e alta mobilidade efetiva do orifício ( μ eff ) É demonstrado que os pMOSFETs Ge com um tratamento de PDA a 400 ° C têm um CET mais baixo e um SS mais íngreme, mas um μ inferior eff em comparação com dispositivos sem PDA.

Histórico

Germânio (Ge) tem sido considerado um dos materiais de canal p atraentes para CMOS avançados porque oferece mobilidade de orifício muito maior do que o Si [1,2,3]. Um dielétrico de porta de alta qualidade e passivação efetiva da superfície de Ge são as chaves para realizar a mobilidade superior efetiva do portador ( μ eff ) e alta corrente de comando no transistor Ge [4,5,6,7]. Vários materiais high-κ, como HfO 2 [8], ZrO 2 [7, 9], La 2 O 3 [10], e Y 2 O 3 [11] foram estudados como dielétricos de porta alternativos para transistores de efeito de campo semicondutores de óxido metálico tipo p (pMOSFETs) para alcançar escalabilidade de espessura equivalente de capacitância (CET) para sub-1 nm. Entre estes, ZrO 2 o dielétrico tem atraído mais atenção devido ao valor κ muito mais alto [12, 13] e à melhor qualidade interfacial [14] em comparação com os baseados em Hf. Foi amplamente relatado que a cristalização de ZrO 2 pode melhorar ainda mais o desempenho elétrico do Ge pMOSFET, por exemplo, reduzindo CET e aumentando μ eff [15, 16]. No entanto, há uma falta de estudo sobre os impactos das etapas do processo para ZrO 2 cristalização no desempenho do dispositivo de transistores Ge.

Neste artigo, investigamos os impactos do recozimento pós-metal (PMA) e do recozimento pós-deposição (PDA) no desempenho elétrico de Ge pMOSFETs com ZrO 2 dielétrico. Melhorou significativamente μ eff e a CET reduzida pode ser alcançada em dispositivos com temperatura PMA mais alta.

Métodos

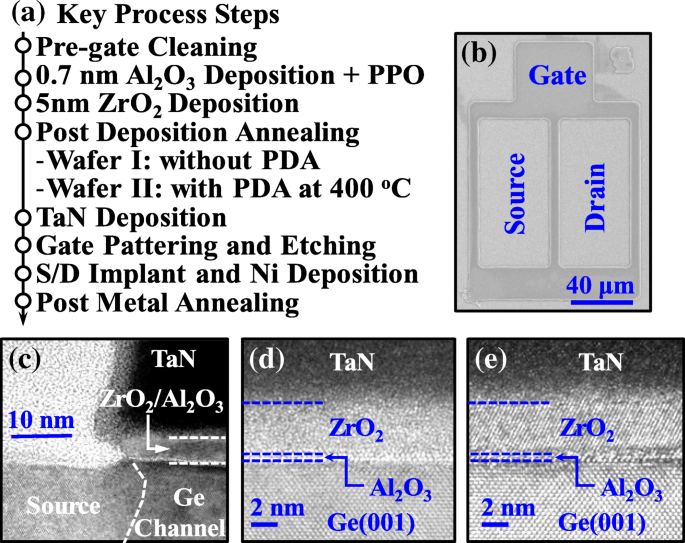

Principais etapas do processo para fabricar Ge pMOSFETs com ZrO 2 dielétricos são mostrados na Fig. 1a. Os Ge pMOSFETs foram fabricados em wafer Ge (001) tipo n com uma resistividade de 0,088–0,14 Ω ∙ cm. Após vários ciclos de limpeza química na solução diluída de HF (1:50) e enxágue em água DI. O wafer de Ge foi carregado em uma câmara de deposição de camada atômica (ALD). A superfície Ge foi passivada por uma pós-oxidação de ozônio (OPO), ou seja, um Al ultrafino 2 O 3 camada foi depositada a 300 ° C e, em seguida, a OPO in situ foi realizada a 300 ° C por 15 min. Depois disso, um ZrO 2 de 5 nm de espessura foi depositado a 250 ° C na mesma câmara ALD usando TDMAZr e H 2 O como precursores de Zr e O, respectivamente. Durante a deposição, Zr [N (CH 3 ) 2 ] 4 fonte foi aquecida a 85 ° C. O processo de PDA foi realizado em alguma amostra a 400 ° C por 60 s usando o recozimento térmico rápido. As amostras com e sem PDA foram designadas wafer II e I, respectivamente. Em seguida, um eletrodo de porta TaN de 100 nm de espessura foi depositado por pulverização catódica reativa. Após a padronização e corrosão da porta, as regiões de origem / dreno (S / D) foram formadas por BF 2 + implantação a uma energia de 30 keV e uma dose de 1 × 10 15 cm −2 . Contatos S / D de níquel de quinze nanômetros foram formados por um processo de decolagem. Finalmente, o PMA a 350, 400, 450 e 500 ° C por 30 s foi realizado para ativação do dopante e metalização S / D.

a Principais etapas do processo para fabricar Ge pMOSFETs com ZrO 2 dielétrico. b Imagem SEM do transistor fabricado. c Imagem XTEM de Ge pMOSFET mostrando a porta e as regiões S / D. d , e Imagens HRTEM de pilhas de portas de Ge pMOSFETs no wafer I recozido a 400 ° C e 500 ° C, respectivamente

A Figura 1b mostra a imagem do microscópio eletrônico de varredura (SEM) de um Ge pMOSFET fabricado. A Figura 1c mostra a imagem do microscópio eletrônico de transmissão transversal (XTEM) de Ge pMOSFET, mostrando a região de origem / dreno, porta de metal e ZrO 2 dielétrico. As Figuras 1d ee mostram as imagens TEM de alta resolução (HRTEM) das pilhas de portas de Ge pMOSFETs com um PMA a 400 e 500 ° C, respectivamente, no wafer I. Observa-se que o ZrO 2 dielétrico foi totalmente cristalizado e submetido a um PMA a 500 ° C. A espessura de Al 2 O 3 a camada interfacial é de cerca de 0,7 nm.

Resultados e discussão

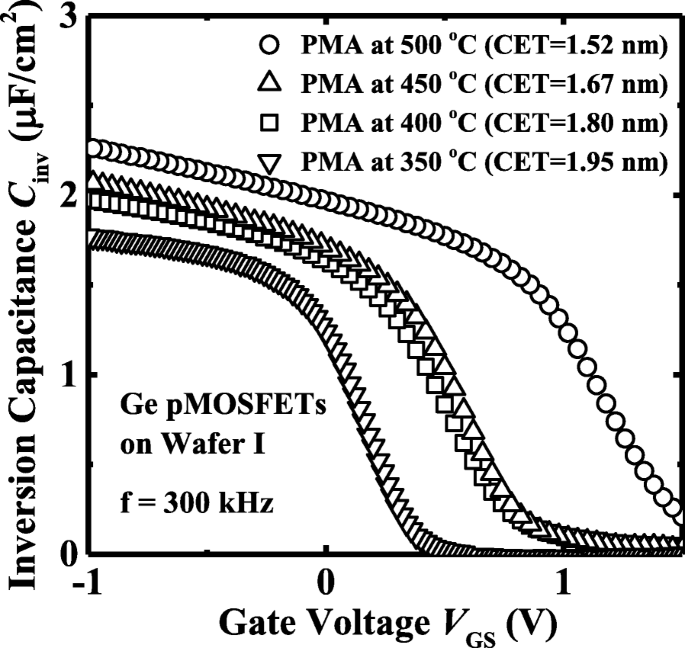

Capacitância de inversão C inv vs. V GS curvas medidas a uma frequência de 300 kHz para os dispositivos no wafer I são mostrados na Fig. 2. Os valores CET são extraídos para ser ∼ 1,95, 1,80, 1,67 e 1,52 nm para os dispositivos com PMA em 350, 400, 450, e 500 ° C, respectivamente. O CET menor é alcançado em uma temperatura de PMA mais alta devido à cristalização de ZrO 2 . Em geral, os valores de κ para ZrO amorfo e cristalino 2 são cerca de 20–23 e 28–30, respectivamente. Um ZrO cristalino de 5 nm de espessura 2 contribui com um EOT de ~ 0,7 nm. A mudança de C-V curvas com várias temperaturas de PMA se devem ao fato de que a cristalização reduz a densidade das armadilhas de massa em ZrO 2 dielétrico.

Inversão C inv - V GS curvas para os Ge pMOSFETs no wafer I com um PMA a 350 ° C, 400 ° C, 450 ° C e 500 ° C

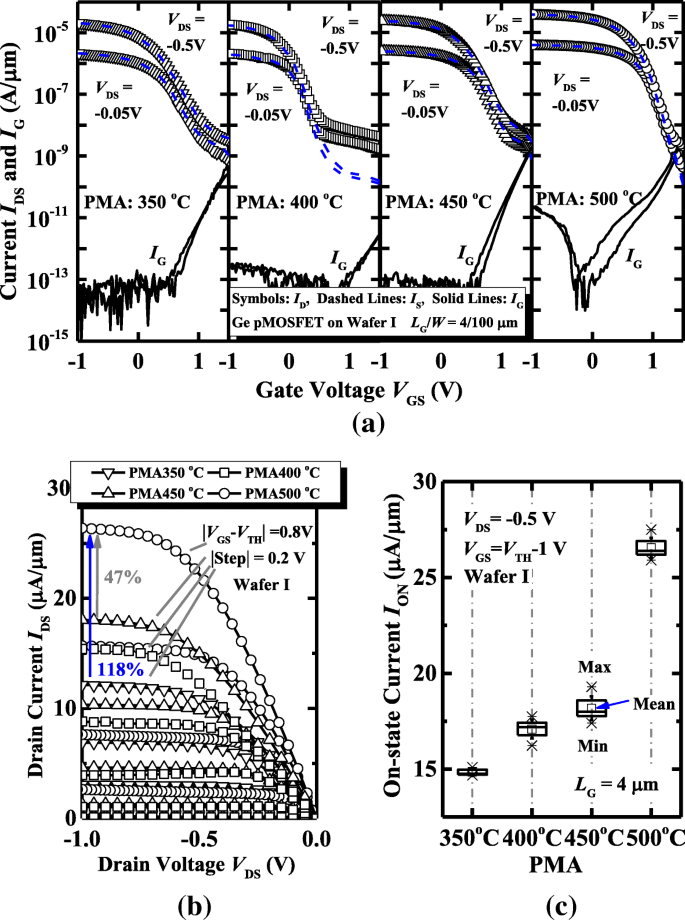

A Figura 3a mostra as características de transferência medidas e correntes de fuga de porta I G de Ge pMOSFETs no wafer I com as diferentes temperaturas de PMA. Todos os dispositivos têm um comprimento de portão L G de 4 μm e uma largura de portão W de 100 μm. Ge pMOSFETs exibem muito menor I G em comparação com eu DS para todas as temperaturas PMA. Um eu LIGADO / eu DESLIGADO proporção acima de 10 4 é obtido para o dispositivo com um PMA a 500 ° C. O eu DS - V DS curvas dos dispositivos medidos no overdrive do portão diferente | V GS - V TH | são mostrados na Fig. 3b. Observa-se que a tensão limite V TH é definido como o V GS em eu DS de 10 −7 A / μm. O transistor Ge com PMA a 500 ° C obtém ~ 47% e 118% de melhoria da corrente de acionamento em comparação com os dispositivos recozidos a 450 ° C e 350 ° C, respectivamente, a V DS de - 1,0 V e um | V GS - V TH | de 0,8 V. A Figura 3c mostra o gráfico estatístico do I LIGADO em um V DS de - 0,5 V e um V GS - V TH de -1 V para pMOSFETs Ge com as várias temperaturas de PMA. Todos os transistores neste gráfico têm um L G de 4 μm e um W de 100 μm. Dispositivos com PMA a 500 ° C exibem um I melhorado LIGADO em comparação com aqueles com temperaturas de PMA mais baixas, o que é atribuído à diminuição da resistência S / D, ao CET reduzido e ao μ mais alto eff , que será discutido mais tarde.

a Medido I D , eu S , e eu G vs. V GS curvas de Ge pMOSFETs no wafer I com o PMA em 350, 400, 450 e 500 ° C. b eu DS - V DS curvas medidas nos diferentes V GS - V TH para os dispositivos. c O dispositivo recozido a 500 ° C tem uma corrente no estado mais alta I LIGADO em comparação com os transistores com o PMA nas temperaturas mais baixas

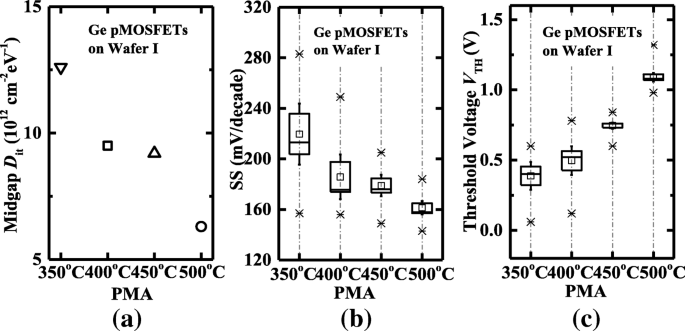

A Figura 4 mostra os gráficos estatísticos de midgap D it , SS e V TH características para os dispositivos com as diferentes temperaturas PMA. Conforme mostrado na Fig. 4a, com base no método de condutância máxima [17], o midgap D it os valores são extraídos para serem 1,3 × 10 13 , 9,5 × 10 12 , 9,2 × 10 12 e 6,3 × 10 12 cm −2 eV −1 para os dispositivos com PMA em 350, 400, 450 e 500 ° C, respectivamente. A Figura 4b apresenta que os Ge pMOSFETs recozidos a 500 ° C têm as características SS melhoradas do que os transistores recozidos nas temperaturas mais baixas, devido ao intervalo médio menor D it e CET. Os valores de D it e SS de Ge pMOSFETs com PMA são ainda maiores do que aqueles dos transistores Ge mais bem relatados. Possivelmente poderia ser reduzido otimizando o módulo de passivação OPO, por exemplo, Al 2 O 3 espessura e temperatura e duração da oxidação do ozônio. V TH muda para o V positivo GS com o aumento da temperatura do PMA, que se origina da redução do CET e D it . Conclui-se que o melhor desempenho elétrico é obtido para Ge pMOSFETs com PMA a 500 ° C.

Comparação de a midgap D it , b SS e c V TH para Ge pMOSFETs no wafer I com o PMA em 350, 400, 450 e 500 ° C

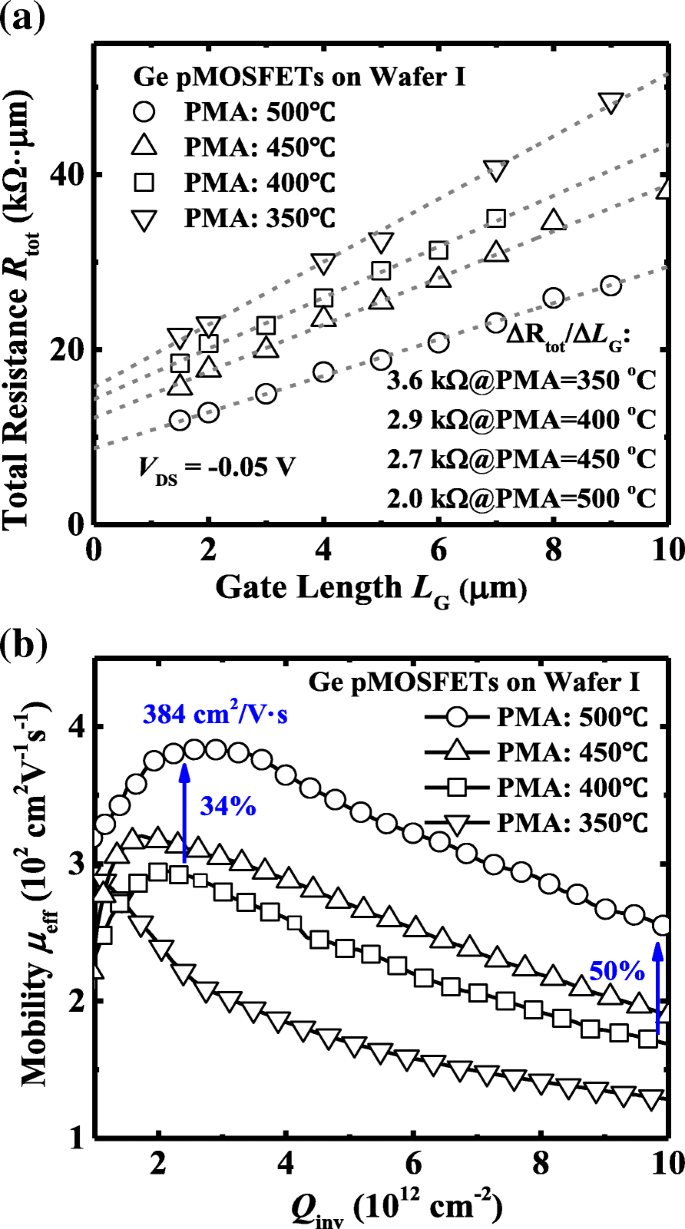

μ eff , como um fator crucial que afeta a corrente e a transcondutância do dispositivo em Ge pMOSFETs, foi medido usando o Δ R tot / Δ L G método [18]. Um grande número de dispositivos foi medido com L G variando de 1,5 a 9 μm. A Figura 5a ilustra a resistência total R tot extraído em um | V GS - V TH | de - 1 V e um V DS de - 0,05 V em função de L G . O R SD é o valor no qual a linha ajustada cruza no y -eixo. O R SD os valores foram estimados em cerca de 7,85, 7,15, 6,10 e 4,35 kΩ · μm para dispositivos com PMA a 350, 400, 450 e 500 ° C, respectivamente. Isso é indicativo da melhor ativação dopante de S / D em temperatura PMA mais alta. μ eff pode ser extraído por μ eff =1 / [ WQ inv (Δ R tot / Δ L G )], onde Q inv é a densidade de carga de inversão no canal Ge e Δ R tot / Δ L G é a inclinação do R tot vs. L G como mostrado na Fig. 5a. O menor Δ R tot / Δ L G para dispositivos com PMA a 500 ° C indica um aprimoramento em μ eff em comparação com transistores com PMA a 450 ° C. A Figura 5b mostra μ eff como uma função de Q inv curvas, extraídas usando a divisão C - V método. O pico de mobilidade do buraco é 384 cm 2 / V · s para dispositivos com PMA a 500 ° C, que é 31% superior ao dos dispositivos com PMA a 400 ° C. Em alto Q inv de 1 × 10 13 cm −2 , Os Ge pMOSFETs que foram submetidos a um PMA a 500 ° C alcançam um aumento de mobilidade em comparação com os dispositivos recozidos a 400 ° C. Transistores Ge com ZrO cristalino 2 têm a densidade mais baixa de carga de armadilha em massa, resultando em menor dispersão remota de buracos de Coulomb, em comparação com os dispositivos com ZrO amorfo 2 . Devido à interface suave entre o ZrO cristalino 2 e dispositivos Ge, Ge recozidos a 500 ° C têm um espalhamento de rugosidade de superfície inferior e mostram uma mudança de mobilidade de pico para o Q superior inv .

a R tot como uma função de L G em um V GS - V TH de - 1 V e um V DS de - 0,05 V para dispositivos em wafer I com várias temperaturas de PMA. b μ eff vs. Q inv extraído pela divisão C - V método. A maior mobilidade é obtida em dispositivos com PMA a 500 ° C

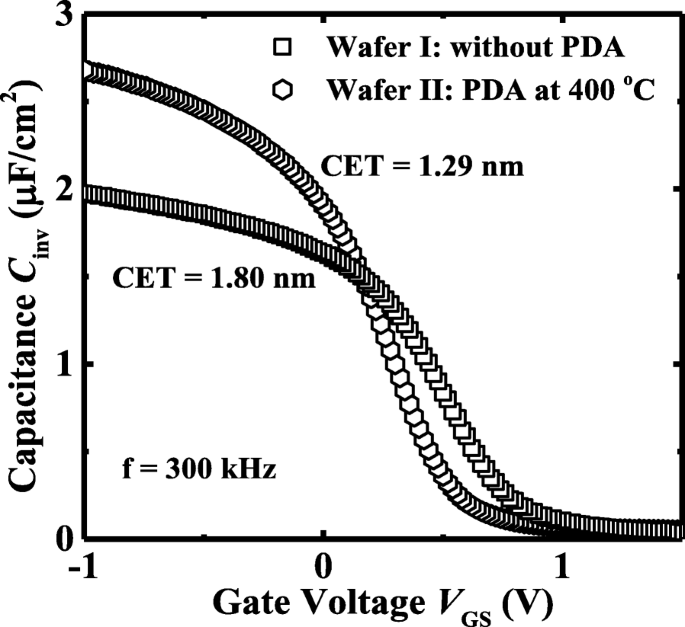

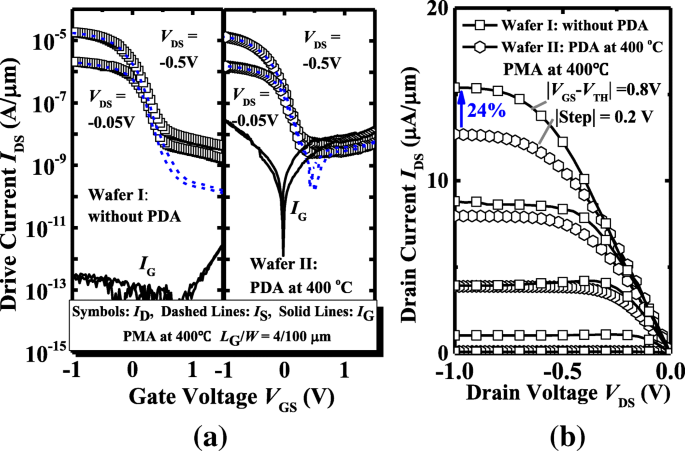

A seguir, discutimos os impactos do PDA nas características elétricas dos Ge pMOSFETs. A Figura 6 mostra o C medido inv vs. V GS dos Ge pMOSFETs no wafer I e no wafer II com um PMA a 400 ° C. O dispositivo que foi submetido a um PDA a 400 ° C tem um valor CET muito mais baixo de 1,29 nm em comparação com o dispositivo sem PDA, 1,80 nm. A Figura 7a mostra o I D , eu S , e eu G - V GS curvas características de Ge pMOSFETs em wafer I e wafer II, e os dispositivos que foram submetidos a um PMA a 400 ° C. Uma corrente de fuga de porta maior é obtida para o dispositivo com PDA em comparação com o transistor sem PDA, o que é devido ao CET mais baixo. O correspondente I DS - V DS curvas dos dispositivos medidos em diferentes overdrive de portão V GS - V TH são mostrados na Fig. 7b. O transistor Ge sem PDA mostra uma melhoria de ~ 24% na corrente de acionamento em relação ao transistor com PDA a 400 ° C no mesmo overdrive de -0,8 V na região de saturação.

C inv -V GS plotagens para os dispositivos em wafer I e II com um PMA a 400 ° C

a eu D , eu S , e eu G vs. V GS curvas de Ge pMOSFETs em wafer I e II com PMA a 400 ° C. b eu DS - V DS curvas medidas em V diferentes GS - V TH para os dispositivos

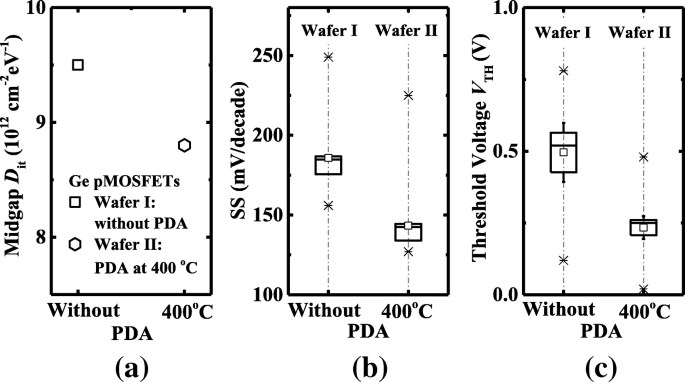

A Figura 8 representa os resultados estatísticos do midgap D it , SS e V TH dos Ge pMOSFETs com e sem PDA. A Figura 8a mostra que quanto menor D it é alcançado em pMOSFETs Ge com PDA a 400 ° C em comparação com dispositivos sem PDA. Na Fig. 8b, o valor mais baixo da oscilação média de subliminar de 142 mV / década é alcançado para dispositivos com PDA a 400 ° C, correspondendo ao CET inferior e ao D inferior it . Indica que os dispositivos com PDA a 400 ° C têm um ZrO 2 superior Interface / Ge. A Figura 8c mostra que os dispositivos com e sem PDA têm um V diferente TH ; pode ser atribuído à densidade de armadilhas na metade inferior do bandgap dominante no V TH .

Comparação de a midgap D it , b SS e c V TH para Ge pMOSFETs em wafer I e II com PMA a 400 ° C

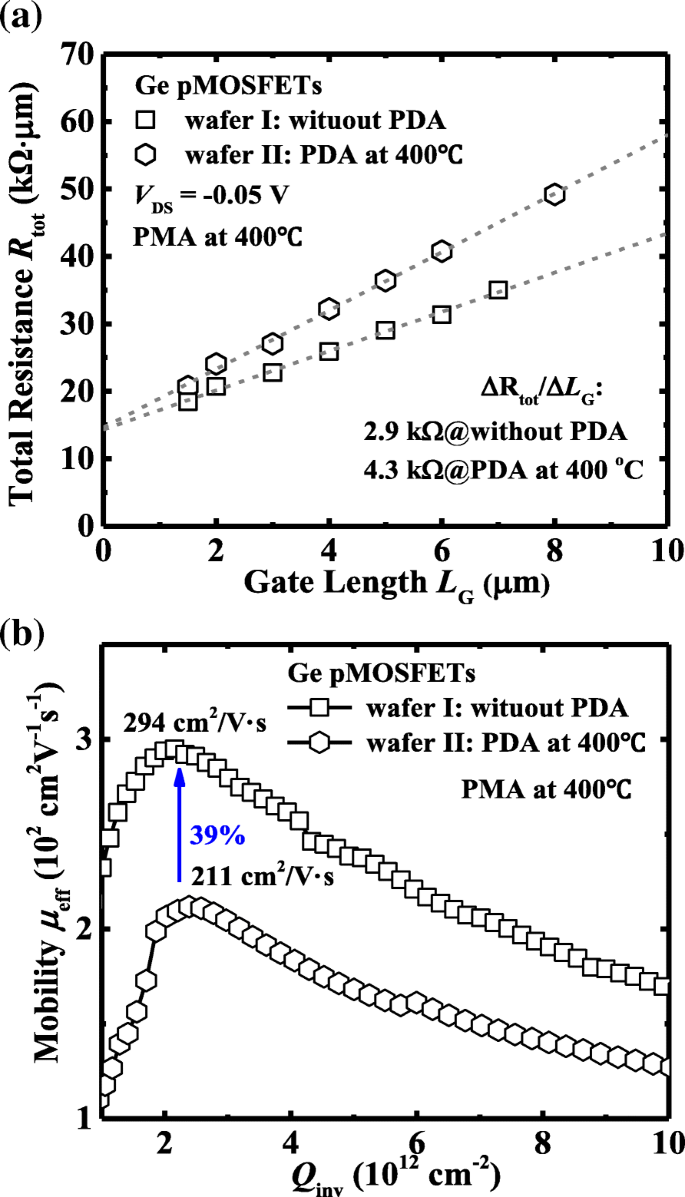

A Figura 9a mostra o R tot vs. L G curvas em uma ultrapassagem de portão de - 1 V e V DS de - 0,05 V para dispositivos com PMA a 400 ° C. O R SD os valores são estimados em cerca de 7,15 e 7,30 kΩ · μm para dispositivos sem e com PDA a 400 ° C, respectivamente. Conforme mostrado na Fig. 9b, um pico notável mais alto μ eff é alcançado para Ge pMOSFETs sem PDA, correspondendo ao menor Δ R tot / Δ L G na Fig. 9a, em comparação com dispositivos com PDA. Os dispositivos com um PDA a 400 ° C exibem um pico μ eff de 211 cm 2 / V · s; a mobilidade inferior do buraco pode ser atribuída principalmente ao forte espalhamento remoto de Coulomb contribuído pela carga fixa em ZrO 2 dielétrico.

a R tot vs. L G curvas para dispositivos em wafer I e wafer II com PMA a 400 ° C. b Mobilidade do furo μ eff vs. Q inv para dispositivos com e sem PDA

Conclusões

Em resumo, os impactos do PMA e PDA no Ge pMOSFET com ZrO 2 dielétricos foram amplamente investigados. Cristalização de ZrO 2 O dielétrico de porta fornece mobilidade de orifício significativamente aprimorada e CET reduzido em comparação com dispositivos na temperatura PMA mais baixa. Uma mobilidade de buraco de pico de 384 cm 2 / V · se corrente de unidade aprimorada foram alcançados em dispositivos com PMA a 500 ° C. Dispositivos com PDA a 400 ° C exibiram o CET inferior e o menor D it mas a mobilidade pobre do orifício e a maior corrente de fuga em comparação com transistores sem PDA.

Disponibilidade de dados e materiais

Os conjuntos de dados que suportam as conclusões deste artigo estão incluídos no artigo.

Abreviações

- ALD:

-

Deposição de camada atômica

- BF 2 + :

-

Íon fluoreto de boro

- CET:

-

Espessura capacitiva efetiva

- Ge:

-

Germânio

- HF:

-

Acido hidrosulfurico

- HRTEM:

-

Microscópio eletrônico de transmissão de alta resolução

- IL:

-

Camada interfacial

- MOSFETs:

-

Transistores de efeito de campo semicondutores de óxido metálico

- Ni:

-

Níquel

- PDA:

-

Recozimento pós-deposição

- PMA:

-

Recozimento pós-metal

- SS:

-

Balanço de sublimiar

- TaN:

-

Nitreto de tântalo

- TDMAZr:

-

Tetraquis (dimetilamido) háfnio

- ZrO 2 :

-

Dióxido de zircônio

- μ eff :

-

Mobilidade efetiva da operadora

Nanomateriais

- KUHMUTE redesenha mobilidade com impressão 3D SLS

- Impressão 3D de alta velocidade com AFPM

- Impressão 3D de alta velocidade com AION500MK3

- Controle de Polarização Terahertz Completo com Largura de Banda Ampliada via Metasurfaces Dielétricos

- Memória resistiva ZrO2 / ZrO2 - x / ZrO2 sem conformidade com comportamento de comutação multiestado interfacial controlável

- Conversor de polarização com birrefringência controlável baseado em metassuperfície híbrida totalmente dielétrica-grafeno

- Célula solar híbrida de silício orgânico nanoestruturado de alto desempenho com estrutura de superfície modificada

- Aprimoramento dielétrico de capacitores de Al2O3 / ZrO2 / Al2O3 MIM depositados na camada atômica por recozimento por micro-ondas

- Uma referência de voltagem sem resistor de baixa potência em nanoescala com alto PSRR

- Ge pMOSFETs de alta mobilidade com passivação de Si amorfo:impacto da orientação da superfície