Gravador de divisão de carga in situ (CSIR) para exame em tempo real do efeito de carregamento de plasma em processos FinFET BEOL

Resumo

Um novo dispositivo para monitorar danos induzidos por plasma no processo de back-end-of-line (BEOL) com capacidade de divisão de carga é proposto e demonstrado pela primeira vez. Este novo registrador in situ de divisão de carga (CSIR) pode rastrear de forma independente a quantidade e a polaridade dos efeitos de carga do plasma durante o processo de fabricação de circuitos avançados de transistor de efeito de campo (FinFET). Ele não apenas revela os níveis de carga de plasma em tempo real e in situ nas antenas, mas também separa o efeito de carga positivo e negativo e fornece duas leituras independentes. À medida que as tecnologias CMOS buscam linhas de metal mais finas no futuro, o novo esquema de separação de carga fornece uma ferramenta poderosa para a otimização do processo BEOL e outras melhorias na confiabilidade do dispositivo.

Histórico

Processos aprimorados com plasma são amplamente usados na formação de circuitos de transistor de efeito de campo fin (FinFET), que são compostos de muitas estruturas de razão de aspecto alta e linhas de metal finas [1]. Durante a fabricação, gravação e etapa de deposição para realizar essas composições 3D podem levar a um estresse induzido por plasma significativo para os dispositivos FinFET [2,3,4]. Conforme a tecnologia CMOS FinFET avança, a largura de linha e o passo do metal reduzem mais agressivamente do que sua altura, levando à necessidade de formar valas de alto formato definidas por linhas extremamente finas. Inevitavelmente, isso promove a gravidade do dano induzido por plasma (PID) aos transistores, e seu efeito correspondente na confiabilidade do circuito torna-se uma das principais preocupações no desenvolvimento de tecnologias FinFET [5,6,7]. Na formação de pequenos contatos, vias e linhas metálicas finas, geralmente são aplicados plasma de alta potência e alta seletividade [8]. Além disso, na decapagem da aleta bulk, a pulverização catódica de íons reativos na superfície da aleta pode levar a defeitos na aleta bulk, críticos para as características dos transistores [9]. A fim de permitir portas metálicas finas e estruturas de interconexão densas, pilhas de metal complexas são mais frequentemente usadas em tecnologias FinFET avançadas [10, 11]. Além disso, alto- k O dielétrico de porta usado em tecnologia avançada geralmente leva a um aprisionamento induzido por estresse aprimorado após o processo de plasma [12,13,14]. Durante o carregamento do plasma, o caminho de descarga através de aletas estreitas e para o substrato pode levar a níveis de tensão mais não uniformes em todo o wafer [15]. O estresse induzido por plasma no óxido da porta do transistor é conhecido por resultar na degradação adicional da integridade dielétrica da porta [16, 17].

O dano induzido por plasma no filme dielétrico de porta pode levar à degradação do desempenho em cenários de carregamento altamente não uniformes, mesmo perda de rendimento [18,19,20], como resultado de falhas de confiabilidade [21, 22]. Assim, em tecnologias FinFET avançadas, os dispositivos de teste com estruturas de antenas ampliadas são geralmente usados para monitorar os efeitos do PID, que fornecem feedbacks para a otimização do processo.

A medida mais comum e amplamente usada de PID é a característica de tempo de quebra das amostras de teste com grandes estruturas de antena. O dano latente nesses padrões PID são tipicamente refletidos pela medição da degradação dependente do tempo das camadas dielétricas da porta, portanto, falhando em fornecer o feedback em tempo real dos processos de plasma [23]. Além disso, os dispositivos de teste convencionais não podem dizer as fontes e a polaridade da taxa de carga induzida por plasma e / ou potencial máximo acumulado na antena. Um gravador PID com uma porta flutuante acoplada a uma estrutura de antena foi proposto com capacidade de detecção in situ em nosso estudo anterior [24, 25]. Neste trabalho, propusemos um gravador PID revisado com um recurso de divisão de carga. Por meio de um diodo direto e um diodo reverso conectado a uma estrutura de antena comum, o novo design fornece caminhos separados para cargas positivas e negativas. Portanto, os níveis de carga de ambas as polaridades podem ser registrados de forma independente. Este novo gravador in situ de divisão de carga (CSIR), exigindo apenas pequenas antenas, permite um estudo futuro do efeito de carga de plasma em processos de meio-fim de linha (MEOL).

Métodos

Polaridade de carregamento de plasma

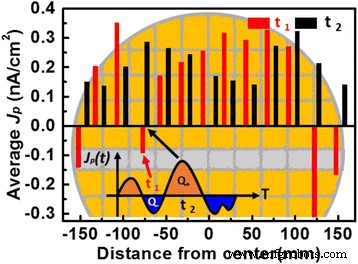

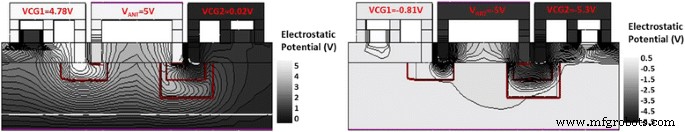

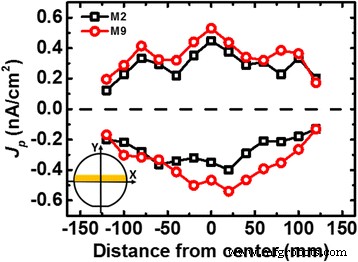

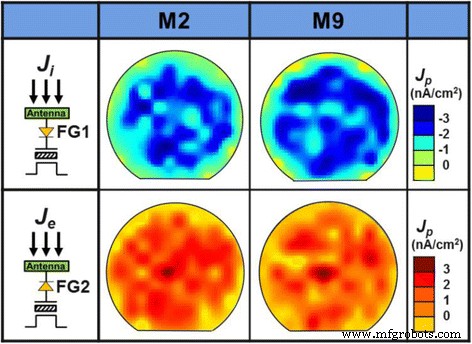

Estudos anteriores relataram que, durante o processo de corrosão na formação de camadas de poli ou metal, a não homogeneidade do plasma, bem como as variações do potencial da antena podem levar a uma diferença drástica na taxa de carregamento ou mesmo as polaridades podem mudar em diferentes locais [24, 25]. O macroambiente na câmara de plasma e os micropadrões podem afetar a distribuição das taxas de carga em um wafer [26]. Nomeadamente, a taxa de carregamento de plasma na corrosão de fim de linha (BEOL) varia espacialmente e em tempo oportuno. Durante os processos de plasma de radiofrequência (RF), a superfície do wafer coleta a corrente de carga, J p , que é composto por uma corrente iônica J i e uma corrente de elétrons J e [26]. A corrente de íons é quase constante com o tempo e é determinada pela densidade de íons J i e a velocidade de Bohm [26]. Uma vez que o potencial de plasma V p ( t ) é maior do que o potencial da porta V G na maior parte do tempo, a corrente de elétrons flui apenas durante os curtos períodos em que o potencial do plasma está próximo de seu mínimo. Durante Q FG processo, a tensão da porta pode aumentar ou diminuir ao longo de muitos ciclos de RF, dependendo de qual componente das correntes é maior, até que uma tensão da porta em estado estacionário seja alcançada quando a corrente de tunelamento se equilibra J p na antena. Conforme mostrado na Fig. 1, a distribuição da taxa de carga do plasma, J P ( x , y , t ), através do wafer durante o processo de corrosão em diferentes estágios de mudanças na magnitude, bem como nas polaridades, onde pode ser expresso como na Eq. (1) onde J e representa a densidade de corrente de elétrons e J i representa a densidade de corrente de íons.

$$ {J} _ {\ mathrm {p}} ={J} _ {\ mathrm {e}} + {J} _ {\ mathrm {i}} \ dots $$ (1)

Distribuição da taxa de carga induzida por plasma na linha central do wafer durante o processo de corrosão em momentos diferentes. A polaridade de carregamento do plasma em um local específico pode mudar ao longo do tempo

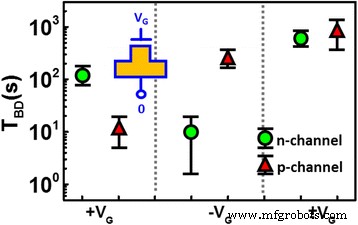

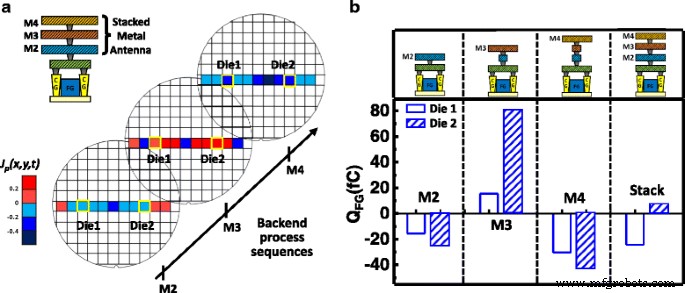

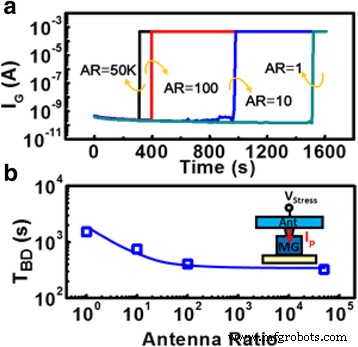

As diferentes polaridades de carga de plasma resultam em carga de antena positiva ou negativa, Q P , acumulado em um horário e local diferentes. Para esclarecer, na hora t 1 , um negativo J p leva a carga negativa da antena Q -. Em t 2 , um J positivo p induz uma carga de antena positiva Q + no local idêntico no wafer, conforme ilustrado na Fig. 1. Assim, carga positiva ou negativa pode se acumular em uma mesma antena em momentos diferentes durante o processo de corrosão. A partir de relatórios anteriores [27], os níveis de pico de J e e J i estão em torno de - 0,15 e 0,35 mA / cm 2 , respectivamente. Foi descoberto [28, 29] que o estresse DC e AC / porta bidirecional no FinFET do canal n e do canal p resulta em diferentes danos latentes ao filme dielétrico da porta. Estresses de alta tensão com polarização DC positiva ou negativa e tensão AC com uma frequência de chaveamento de 0,1 Hz são aplicados a amostras de teste FinFET convencionais, respectivamente. Conforme mostrado na Fig. 2, o tempo para desagregação ( T BD ) de um transistor estressado por estresse positivo, negativo e de porta em ambas as direções são comparados. Os resultados indicam que a tensão da porta DC causará danos piores nas amostras, enquanto a tensão da porta AC resulta em danos menos graves a esses transistores, conforme sugerido pelo T mais longo BD para amostras submetidas a estresse bidirecional. A Figura 2 também mostra que a degradação do óxido depende não apenas da polaridade de carga, mas também do tipo de poços sob os transistores de canal n e canal p, o que se espera ser causado pela diferença nos caminhos de descarga desses testes dispositivos durante o processo. Conseqüentemente, detector PID convencional, que usa T BD já que o indicador de gravidade do dano não pode refletir o nível de carga do plasma durante o processo. Por outro lado, o registrador de carga de plasma proposto em nosso trabalho anterior registra o nível de estresse ao injetar ou ejetar elétrons de / para uma porta flutuante (FG) acoplada por uma antena coletora de carga. Os dados registrados, carga de porta flutuante ( Q FG ), é lido posteriormente após a fabricação [24, 25]. A gravação é então medida pela mudança de tensão de limiar no transistor lido, do qual o canal é controlado e dirigido pela mesma porta flutuante. O potencial elevado na antena com Q P do carregamento de plasma pode induzir tensão positiva e negativa da antena durante a formação de uma única camada de metal. Além disso, para diferentes camadas de metal, diferentes parâmetros de fabricação são usados. Por exemplo, o tempo de gravação, o produto químico usado e as temperaturas da câmara podem variar. Esses parâmetros podem afetar a distribuição de carga da antena em um wafer durante a corrosão. Em outros casos, um transistor com conexões a múltiplas camadas de metal está sujeito a sequências de carregamento de plasma ainda mais complexas, conforme ilustrado na Fig. 3a.

Tempo para decomposição ( T BD ) de FinFETs de canal n e canal p estressados por carga positiva, negativa e positiva + negativa nos eletrodos de porta. T BD de dispositivos sob diferentes tensões de polaridade sugere que o dano acumulado no dielétrico da porta depende não apenas da polaridade de carregamento, mas também dos poços sob FinFETs correspondentes

a O efeito de carga do plasma para as diferentes camadas de metal varia em diferentes locais no wafer. b As cargas positivas e negativas podem se compensar nas camadas de metal empilhadas

Em diferentes estágios do processo BEOL, a corrente de carga de plasma em uma antena particular pode alternar entre corrente de íon e elétron, ou seja, a corrente Q P também pode mudar de positivo para negativo. As gravações em amostras com antena consistindo em metal 2, metal 3, metal 4 e múltiplas camadas de metal estão resumidas na Fig. 3b. Os dados sugerem que o carregamento líquido de uma única camada de metal [24] em uma determinada mudança de polaridade de uma camada para outra. Além disso, o efeito de média encontrado no Q FG das amostras com estruturas de antena de múltiplas camadas de metal é ainda suportado pelos dados medidos na Fig. 3b. Com V positivo e negativo G na antena, o Q final FG será então calculada a média por injeção e ejeção de elétrons para / do FG, que pode ocorrer sequencialmente. Este efeito de compensação limitará o registrador para revelar as condições reais de estresse que um dispositivo experimentou durante os processos de plasma. O CSIR revisado foi projetado para resolver o problema de como registrar individualmente os efeitos de carga positivos e negativos sem interferência e para fornecer dados mais detalhados sobre a situação de carga na câmara de plasma.

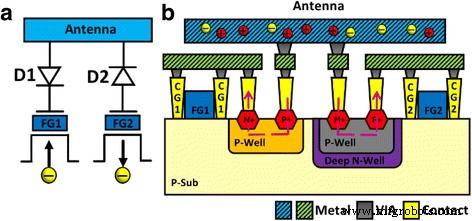

Teste padrão para separação de carga

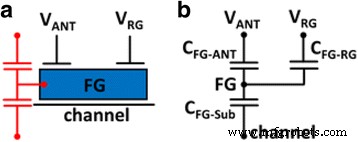

Nesta pesquisa, o carregamento de íon positivo e o carregamento de elétron negativo na antena podem ser separados com um novo registrador in situ de divisão de carga (CSIR) proposto, conforme ilustrado na Fig. 4a. Um CSIR consiste em dois portões flutuantes, FG 1 e FG 2 que registram os diferentes tipos de efeito de carregamento separadamente. A estrutura da antena se conecta às duas portas de acoplamento por meio de um diodo direto (D1) e um diodo reverso (D2), respectivamente. Na metade esquerda da estrutura, as cargas positivas fluirão para a porta de acoplamento 1 (CG 1 ) a D1. Quando CG 1 é carregada positivamente, a tensão é acoplada à porta flutuante através das ranhuras de contato em ambos os lados. A porta flutuante será carregada negativamente à medida que os elétrons são injetados do substrato. A metade direita da estrutura, por outro lado, é o caminho de carga negativa, permitindo que a corrente flua da antena para a porta de acoplamento 2 (CG 2 ) a D2, resultando em Q positivo FG . A Figura 4b mostra ainda a vista em corte transversal do CSIR com diodos pn no chip, direcionando os caminhos de carregamento positivo e negativo para as portas de acoplamento separadas, CG 1 e CG 2 , que acopla o potencial da antena ao FG 1 e o FG 2 , respectivamente.

a Registrador in situ de divisão de carga com duas portas flutuantes separadas conectando-se a um diodo direto (D1) e um diodo reverso (D2) para detectar carga de elétron / íon, respectivamente. b Ilustração em corte transversal do novo gravador in situ de divisão de carga com diodos pn on-chip, direcionando a carga positiva e negativa para as portas de acoplamento separadas, CG 1 e CG 2

Quando a metade esquerda do gravador está habilitada no CSIR sob uma antena carregada positivamente, a metade direita fica inativa porque a carga é bloqueada pelo diodo reverso e vice-versa. Ambos os diodos no chip são compostos por n + / p-well. Para D2, para sustentar a tensão negativa em seu poço p, a região p precisa ser cercada por um poço n profundo, bloqueando o caminho de carga diretamente para o substrato. A distribuição de potencial simulada na seção transversal em um CSIR sob os períodos de carregamento positivo e negativo da antena é mostrada na Fig. 5a e b, respectivamente. Assumindo que o potencial em uma antena atinge 5 V, através do diodo à esquerda, a carga positiva flui para a porta de controle à esquerda, o que resulta em uma alta tensão positiva ( V CG1 ) Ao mesmo tempo, a carga positiva é bloqueada pelo diodo à direita, resultando em um V próximo de zero CG2 . A diferença de potencial nas duas portas de controle é verificada pelos contornos de potencial simulados na Fig. 5a. O efeito da carga negativa na antena é mostrado na Fig. 5b. Perfis de potencial simulados verificam se os diodos pn no chip podem efetivamente direcionar e bloquear o potencial para CG 1 e CG 2 , complementarmente, conforme projetado. Desta forma, os efeitos de carga positivos e negativos correspondentes a diferentes fontes nos tratamentos de plasma podem ser obtidos de forma independente, evitando compensação de carga e problemas de interferência no detector.

Distribuição de potencial simulada em CSIR com tensão de porta de antena positiva e negativa. Os diodos pn direto e reverso separam com sucesso a polaridade de carga da antena

Resultados e discussão

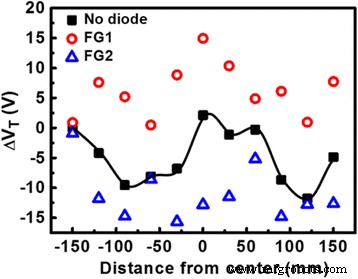

A mudança de tensão de limiar medida (Δ V T ) no dispositivo controlado por FG 1 com diodo direto e aquele por FG 2 com diodo reverso e amostras sem diodo são comparados na Fig. 6. Os dados ao longo da linha central de um wafer revelam que um gravador com uma única porta flutuante está sujeito à neutralização de carga mesmo dentro do processamento de uma única camada de metal. O efeito de média de um gravador sem diodo prova que as taxas de pico de carga não serão refletidas com exatidão. Por outro lado, as leituras do novo CSIR podem fornecer níveis de carga positivos e negativos, de forma independente. Para investigar mais a fundo o efeito da carga do plasma na formação do metal 2 (M2), a carga coletada no FG 1 e FG 2 do CSIR de cada matriz pode ser calculado independentemente pela Eq. (2),

$$ {Q} _ {\ mathrm {FG}} ={C} _ {\ mathrm {T}} \ times \ Delta {V} _ {\ mathrm {T}} \ times {\ alpha} _ {\ mathrm {RG}} \ dots $$ (2)

onde Q FG é a carga no portão flutuante. C T é a capacitância total da porta flutuante, conforme ilustrado na Fig. 7. Δ V T é a mudança de tensão de limiar detectada na porta de leitura do gravador, enquanto α RG é a taxa de acoplamento da porta de leitura.

Distribuição de delta V T no FG 1 com diodo direto e FG 2 com diodo reverso e FG sem diodo ao longo da linha central de um wafer

a O diagrama esquemático de um modelo de rede de capacitância em um dispositivo CSIR. b A capacitância total da porta flutuante é todas as capacitâncias mencionadas em série mais aquelas em paralelo

Quando a carga da porta flutuante é inicialmente zero e Q FG atinge o nível saturado quando o campo elétrico através da camada dielétrica do portão é reduzido a zero, o potencial final do portão da antena no final de um processo de plasma pode ser expresso como segue,

$$ {V} _ {\ mathrm {ANT}} =\ frac {V _ {\ mathrm {FB}} - \ frac {Q _ {\ mathrm {FG}}} {C _ {\ mathrm {T}}}} { \ alpha _ {\ mathrm {ANT}}} \ dots $$ (3)

em que, V ANT é o potencial da porta da antena por carregamento de plasma e α ANT representa a relação de acoplamento para a porta flutuante da porta da antena. V FB é a voltagem de banda plana da porta de metal para o substrato de aleta. Sob um determinado tempo de processo, a densidade média da corrente de carga do plasma, J p pode então ser projetado pela Eq. (4).

$$ {J} _ {\ mathrm {p}} =\ frac {V _ {\ mathrm {ANT}} \ times {C} _ {\ mathrm {ANT}}} {A _ {\ mathrm {ANT}} \ times \ Delta t} \ dots $$ (4)

onde Δ t é a duração de um processo de plasma [28, 29] e C ANT é a capacitância total da antena de metal, enquanto A ANT é a área de carregamento de uma antena. Todos os parâmetros usados nos cálculos acima estão resumidos na Tabela 1.

A distribuição das taxas de carga positiva e negativa através de um wafer durante o processamento das camadas superior (metal 9) e inferior (metal 2) são ainda comparadas na Fig. 8. Isso implica que a carga na estrutura da antena é mais proeminente no metal superior níveis (metal 9), porque no metal 9, sua maior energia de plasma causa J p ser maior do que J p de metal 2 em termos de magnitude. Além disso, os dados sugerem que as taxas de carregamento de elétrons e íons atingem o pico em torno do centro em ambos os casos. Como esperado, as matrizes fechadas no centro do wafer apresentam alto nível de carga, o que pode ser atribuído ao caminho de descarga mais longo durante o tratamento com plasma. Este efeito de localização é idêntico para as condições dominantes de carregamento de mais elétrons e íons. A taxa de carga de plasma projetada, J P ( x, y ), em média sobre a formação de uma única camada de metal, metal 2 (M2) e metal 9 (M9), são comparados na Fig. 9. Esses mapas de wafer revelam que a taxa de carga de elétrons parece estar em um platô, exceto na borda , enquanto as taxas de carregamento de íons mostraram uma variação maior na seção intermediária do wafer. No futuro, espera-se que esses mapas de wafer sob diferentes condições de processamento forneçam insights para a câmara de plasma ou mais diretrizes de otimização, compensando melhor os efeitos de carga.

Comparação da taxa de carga positiva e negativa na linha central de um wafer para processos de metal 2 e metal 9. As taxas de carga atingem o pico em torno do centro, o que significa que o dano induzido pelo plasma é mais grave no centro do wafer

A taxa projetada de carga de elétrons e íons, J e ( x , y ) e J i ( x , y ) são obtidos pelos registradores de divisão de carga em toda a superfície de corrosão durante a formação de metal 2 metal 9

Efeito da proporção da antena

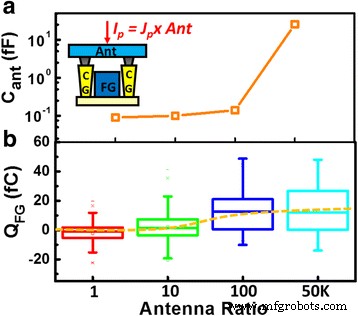

Dispositivos de monitoramento PID tradicionais são tipicamente projetados para amplificar o efeito PID conectando as portas do transistor diretamente a uma grande antena, avaliando os níveis de estresse pelo aumento do Q total P espera-se que seja descarregado através de uma pequena região do canal [30, 31]. A relação da antena (AR) é proporcional à densidade da corrente de tensão através do dielétrico da porta durante os processos de plasma [32]. Grande Q P na antena é conhecido por induzir danos latentes e / ou armadilhas na camada dielétrica, o que acaba levando à degradação da confiabilidade [33]. Como esperado, AR mais alto em FinFETs convencionais eleva significativamente os níveis de estresse, causando um T BD mais grave degradação, ou seja, falha do dispositivo dentro de um período de operação mais curto, consulte a Fig. 10. Por outro lado, em um CSIR, o nível de carga de plasma registrado como a carga de porta flutuante, Q FG , mostra muito pouco efeito de antena. Ou seja, ele não responde ao aumento da área da antena, conforme revelado pelos dados resumidos na Fig. 11.

a As características de tempo de decomposição I G vs tempo dos detectores PID convencionais com o aumento do tamanho da antena. b T BD diminui drasticamente conforme o AR excede 1000

a Conforme a capacitância da antena aumenta, V CG torna-se independente do AR. b Q FG satura quando o AR excede 100 ×

No novo CSIR baseado em porta flutuante, a relação da antena (AR) afetará o potencial de pico nas portas de acoplamento durante o carregamento do plasma. Em tecnologias escalonadas, espera-se que as capacitâncias parasitas na conexão e estrutura de acoplamento reduzam, levando a menos sensibilidade AR nos resultados de gravação. As razões para levar a uma diferença tão óbvia para o efeito AR entre os detectores CSIR e convencionais são as seguintes. Nestes gravadores de porta flutuante, a carga acumulada na antena, Q P não será descarregado através da área do canal. Aumentou Q P aumenta V CG , levando à injeção ou ejeção de elétrons de / para as portas flutuantes. Conforme mostrado na capacitância simulada na Fig. 11a, a capacitância da antena, C formiga , aumenta proporcionalmente à área da antena, A formiga . Com a corrente de carga total diretamente proporcional à área da antena, o AR aumentado em um CSIR não afetará o potencial da antena. Os dados de medição revelam que o Q FG nível permanece quase o mesmo para SCIR com AR excedendo 100 ×.

Este recurso não apenas salva a área do padrão de teste, mas também permite encontrar J P ( x , y ) com maior resolução espacial para estudar o efeito de padronização no PID. Além disso, um detector com antena pequena pode facilitar o projeto de padrões de teste para compreensão do PID no meio-fim da linha (MEOL) e processos de contato.

Finalmente, o resumo de desempenho do novo CSIR para monitoramento de PID no processo BEOL FinFET avançado é resumido na Tabela 2. A faixa de detecção do detector tradicional é AR, enquanto a faixa de detecção do novo gravador in situ é baseada no comprimento de porta flutuante. Além disso, a área do novo gravador in situ pode ser muito pequena. Mais importante ainda, o novo CSIR pode fornecer feedback em tempo real do processo de plasma e níveis separados de carga de íons e taxa de carga de elétrons, de forma independente.

Conclusões

Um novo registrador de divisão de carga in situ (CSIR) para monitorar danos induzidos por plasma é proposto e demonstrado pela primeira vez. O CSIR fornece uma ferramenta poderosa para entender as taxas de carga de elétrons e íons em uma câmara de plasma simultaneamente. Os mapas de wafer podem facilitar um estudo mais aprofundado entre a correlação com a confiabilidade do dispositivo e esses efeitos de carregamento individuais.

Histórico de alterações

Nanomateriais

- Peixe-zebra:um sistema de modelo em tempo real promissor para a entrega de medicamentos neuroespecíficos mediada por nanotecnologia

- Dopagem Substitucional para Mineral Aluminossilicato e Desempenho Superior de Divisão de Água

- Bioflavonóide direcionado ao receptor de folato Nanopartículas de quitosana carregadas com genisteína para efeito anticâncer avançado em cânceres cervicais

- O efeito do plasma sem equilíbrio de contato nas propriedades estruturais e magnéticas de Mn Х Fe3 - X О4 Spinels

- Efeito do tratamento de recozimento in situ na mobilidade e morfologia de transistores de efeito de campo orgânico baseados em TIPS-Pentaceno

- Síntese in situ de nanopartículas bimetálicas de cobre e tungstênio via plasma térmico reativo de radiofrequência (RF)

- Deposição precisa in situ assistida por campo elétrico de nanofibras eletrofiadas γ-Fe2O3 / poliuretano para hipertermia magnética

- Telas fibrosas à base de iodo com eletrofiação in situ para curativo antibacteriano

- Um Nanogerador Triboelétrico Portátil para Monitoramento Respiratório em Tempo Real

- Dispositivo sináptico de captura de carga ReS2 para aplicativo de reconhecimento facial