Transistor de semicondutor de óxido metálico difundido duplo e lateral de resistência ultrabaixa específica com porta dupla aprimorada e camada P-enterrada parcial

Resumo

Uma resistência específica ultra baixa ( R ligado, sp ) O transistor semicondutor de óxido metálico difundido lateralmente (LDMOS) com porta dupla aprimorada e camada parcialmente enterrada em P é proposto e investigado neste artigo. O modelo analítico de resistência para o LDMOS proposto é construído para fornecer uma visão aprofundada da relação entre a resistência da região de deriva e a resistência da região do canal. A camada enterrada em N é introduzida sob o poço P para fornecer um caminho de condução de baixa resistência e reduzir significativamente a resistência da região do canal. A estrutura de porta dupla aprimorada é formada pela camada N-enterrada, evitando a ruptura vertical do tipo punch-through no estado desligado. Camada P-enterrada parcial com comprimento otimizado é adotada sob a região de deriva N para estender a região de depleção vertical e relaxar o pico do campo elétrico no estado desligado, o que aumenta a tensão de ruptura (BV) com baixa resistência da região de deriva. Para o LDMOS com porta dupla aprimorada e camada parcialmente enterrada em P, o resultado mostra que R ligado, sp é 8,5 mΩ · mm 2 enquanto BV é 43 V.

Histórico

Com o aumento da demanda por funções lógicas mais complexas e rápidas em IC de potência analógica, é significativo melhorar o desempenho do transistor semicondutor de óxido metálico difuso lateral (LDMOS), minimizando especialmente a resistência específica ( R ligado, sp ) e maximizando a tensão de ruptura do estado desligado (BV) [1,2,3,4,5,6,7,8,9]. A maioria das tecnologias desenvolvidas concentra-se na otimização da região de deriva para melhorar o equilíbrio de R ligado, sp vs. BV para dispositivos LDMOS [10,11,12,13,14,15,16,17,18,19,20]. Em nosso trabalho anterior, o LDMOS com isolamento de trincheira ultra-rasa (USTI) foi proposto [21]. A profundidade e o ângulo de canto da USTI foram otimizados para alcançar o melhor desempenho da classe. No entanto, para o LDMOS de baixa tensão, a região de deriva está perdendo o domínio em R ligado, sp e a contribuição da região do canal não pode ser ignorada.

Método

Neste trabalho, um novo LDMOS ultrabaixo específico em resistência com porta dupla aprimorada e camada parcialmente enterrada em P é investigado. Os modelos físicos IMPACT.I, BGN, CONMOB, FLDMOB, SRH e SRFMOB são usados na simulação numérica. Um modelo analítico de resistência é proposto para fornecer uma visão aprofundada da relação entre a resistência da região de deriva e a resistência da região do canal. Com base no modelo, a camada N-enterrada e a camada P-enterrada parcial são otimizadas para atingir baixo R ligado, sp e alto BV.

Resultados e discussão

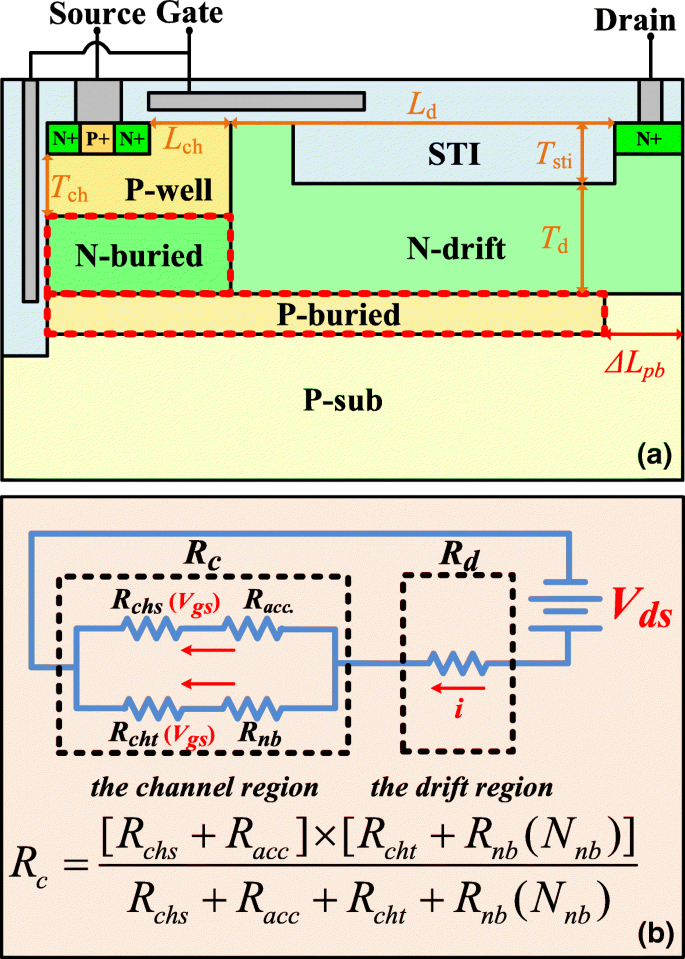

A Figura 1a mostra a seção transversal esquemática de LDMOS de resistência específica ultrabaixa com porta dupla aprimorada e camada parcialmente enterrada em P. O LDMOS apresenta a porta dupla com camada N enterrada e a camada P-enterrada parcial que contribui para reduzir R ligado, sp e aumentar o BV, respectivamente. Na região do canal, a porta dupla aprimorada é formada por porta de trincheira e camada N-enterrada altamente dopada. Em comparação com a estrutura de porta dupla convencional, a camada enterrada em N reduz significativamente a resistência da região do canal ao fornecer um caminho de condução de baixa resistência sob o poço P no estado ligado. Na região de deriva, a camada parcial enterrada em P com alta concentração de dopagem é introduzida sob a região de deriva N para aumentar o BV, mantendo baixo R ligado, sp . A camada P-enterrada parcial ajuda a reduzir o campo elétrico vertical no estado desligado sem quebrar o equilíbrio de carga na região de deriva. O tamanho da chave do novo dispositivo está listado na Tabela 1.

a Visão esquemática de seção transversal de LDMOS de resistência específica ultrabaixa com porta dupla aprimorada e camada P-enterrada parcial. b Esquemático equivalente em resistência para o LDMOS proposto

A Figura 1b mostra o modelo de resistência equivalente esquemático para o LDMOS proposto. A resistência total é considerada como a resistência da região de deriva ( R d ) e a resistência da região do canal ( R c ) em série. Na região do canal, o caminho de condução do canal de superfície é paralelo ao caminho de condução do canal de trincheira. Assim, R c é igual a ( R chs + R acc ) // ( R cht + R nb ), onde R chs , R acc , R cht , e R nb são as resistências do canal de porta de superfície, a região de acumulação, o canal de porta de trincheira e a camada N-enterrada, respectivamente. Com base no modelo de resistência sobre proposto, a redução de R c alcançaria diminuindo R nb sem afetar os outros desempenhos, porque as outras resistências são determinadas principalmente pela tecnologia do processo, tensão de operação e tensão de limiar. O R d foi reduzido com a introdução de camada enterrada em P sob a região de deriva N para aumentar o efeito de campo de superfície reduzida (RESURF) em nosso trabalho anterior. Neste trabalho, a camada P-enterrada parcial é adotada para melhorar o BV, mantendo o baixo R d .

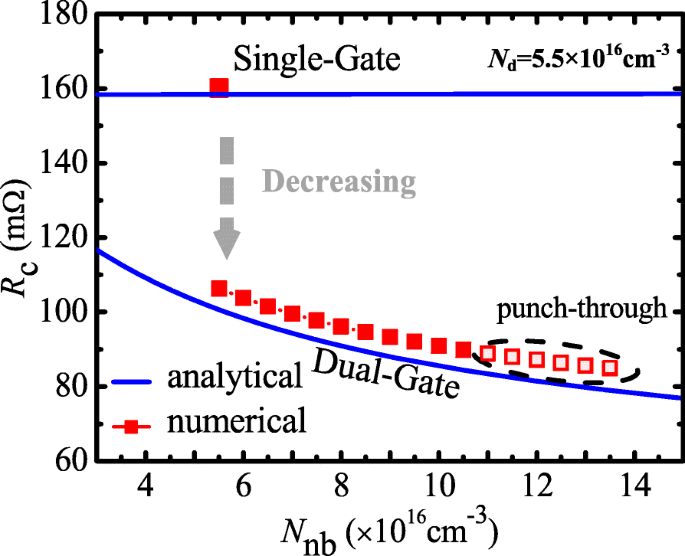

Visando a redução de R c , a camada N-enterrada com alta concentração de dopagem é introduzida sob o poço P. A Figura 2 mostra R numérica e analítica c como funções da concentração de dopagem da camada N-enterrada ( N nb ) com porta única e porta dupla. É indicado que a estrutura de porta dupla ajuda a reduzir R c em comparação com o portão único. Quando N nb = N d =5,5 × 10 16 cm −3 , R c é 110 mΩ. De acordo com o modelo de resistência, R nb é o principal contribuidor de R c . E então, o R nb é desejado diminuir com o objetivo de menores R c . Conforme mostrado na Fig. 2a, R c é reduzido com N nb aumentando. Quando N nb =1,35 × 10 17 cm −3 , R c é reduzido para 85 mΩ. No entanto, a Fig. 2 também mostra que N nb seria limitado por uma quebra completa. Por causa da adição de portão de trincheira, R c diminui inicialmente em 34% com N nb = N d =5,5 × 10 16 cm −3 . Como N nb aumenta, R c diminui continuamente. Com N otimizado nb =1,05 × 10 17 cm −3 , R c diminuiu 45%, finalmente. Quando N nb > 1,05 × 10 17 cm −3 , o colapso total acontecerá no poço P. O resultado analítico de R ligado, sp mostrado na Fig. 2 indica que o modelo proposto fornece um bom ajuste com os resultados da simulação numérica. Portanto, o modelo é confiável para guiar o projeto de otimização.

Numérico e analítico R c como uma função de N nb com porta única e porta dupla ( Z =1 cm). N d é a concentração de dopagem da região N-deriva

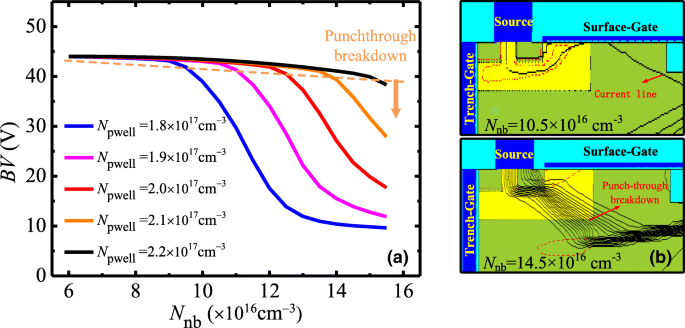

A Figura 3a mostra o BV numérico em função de N nb com concentração de dopagem diferente de P-well ( N pwell ) N nb tem efeito não apenas sobre o R c , mas também o BV. Para um dado N pwell , BV se mantém inalterado em pequeno N nb , e então diminui com N nb aumentando. Quando N nb aumenta para 1,2 × 10 17 cm −3 , BV começa a cair com N pwell =2 × 10 17 cm −3 . A queda de BV é atribuída à ruptura por punção na região do poço P, como mostrado na Fig. 3b. À medida que a tensão de drenagem aumenta, a região de depleção no poço P se estende até a fonte. Quando a região de depleção ataca a junção N + / P-well, ocorre a ruptura do punch-through. Para um grande N pwell , o esgotamento se estende principalmente para a região de deriva e a quebra de punção é evitada sem degradar o BV. Embora o poço P com alta concentração de dopagem beneficie-se de evitar a ruptura do punch-through, aumentaria a tensão de limiar. Assim, N pwell de 2 × 10 17 cm −3 é escolhido levando-se em consideração a tensão limite e a compensação entre o BV e R ligado, sp .

a BV numérica em função de N nb com N diferente pwell . b Perfil de densidade atual para N nb =10,5 × 10 16 cm −3 e 14,5 × 10 16 cm −3 enquanto N pwell =2 × 10 17 cm −3 no colapso

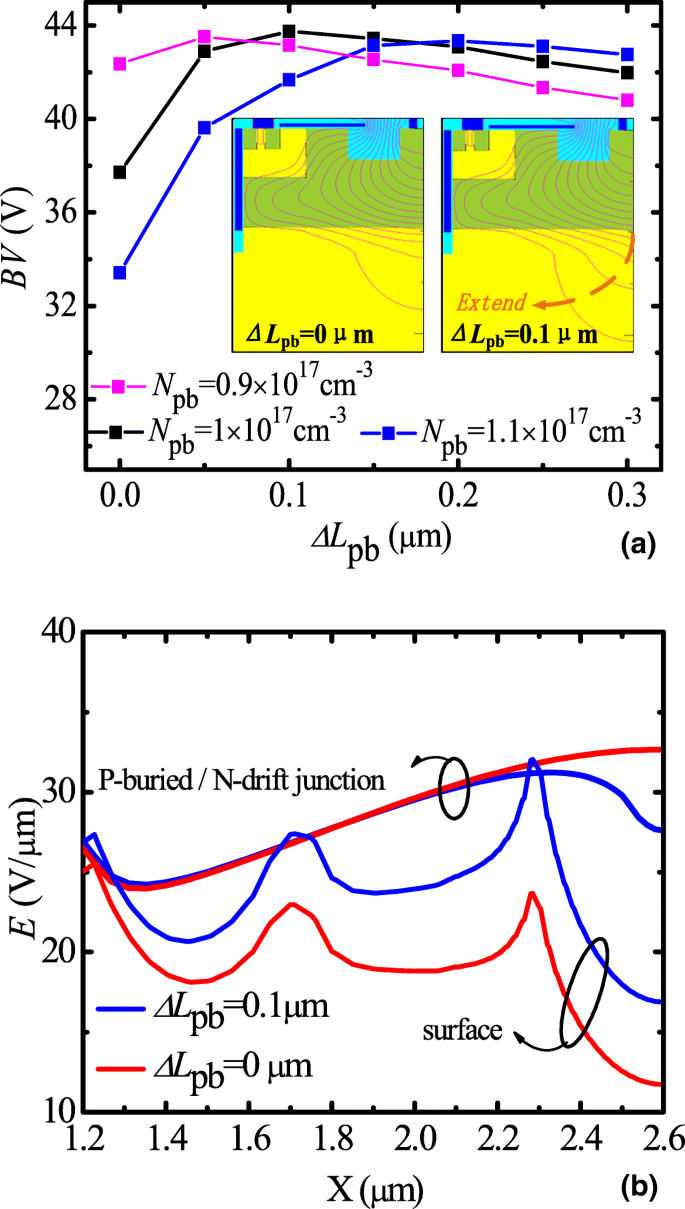

A fim de alcançar baixo R d e alto BV, camada parcialmente enterrada em P é introduzida sob a região de deriva N. A Figura 4a mostra BV como uma função de Δ L pb com N diferente pb . Para um dado N pb , como Δ L pb aumenta, o VB aumenta e depois diminui ligeiramente. Quando Δ L pb =0,1 μm, N pb =1 × 10 17 cm −3 , BV atinge o valor máximo 43 V. A inserção mostra o perfil de contorno equipotencial com N pb =1 × 10 17 cm −3 . É indicado que o contorno equipotencial na estrutura da camada P enterrada parcial se estende mais ao substrato em comparação com a camada totalmente P enterrada. A Figura 4b mostra a distribuição do campo elétrico na superfície e a interface de junção P-enterrada / N-deriva. Para LDMOS convencionais otimizados, a quebra ocorre geralmente na interface N-drift / P-enterrada. Para o LDMOS proposto, a junção de N-deriva / P-sub substitui a junção de N-deriva / P-enterrada para relaxar o campo elétrico vertical e estender a região de depleção, o que resulta em um maior BV, mantendo baixo R d .

a BV em função de ΔL pb com N diferente pb . A inserção é o perfil de contorno equipotencial com N pb =1 × 10 17 cm −3 . b Distribuição do campo elétrico na superfície e na interface de junção P-enterrada / N-deriva

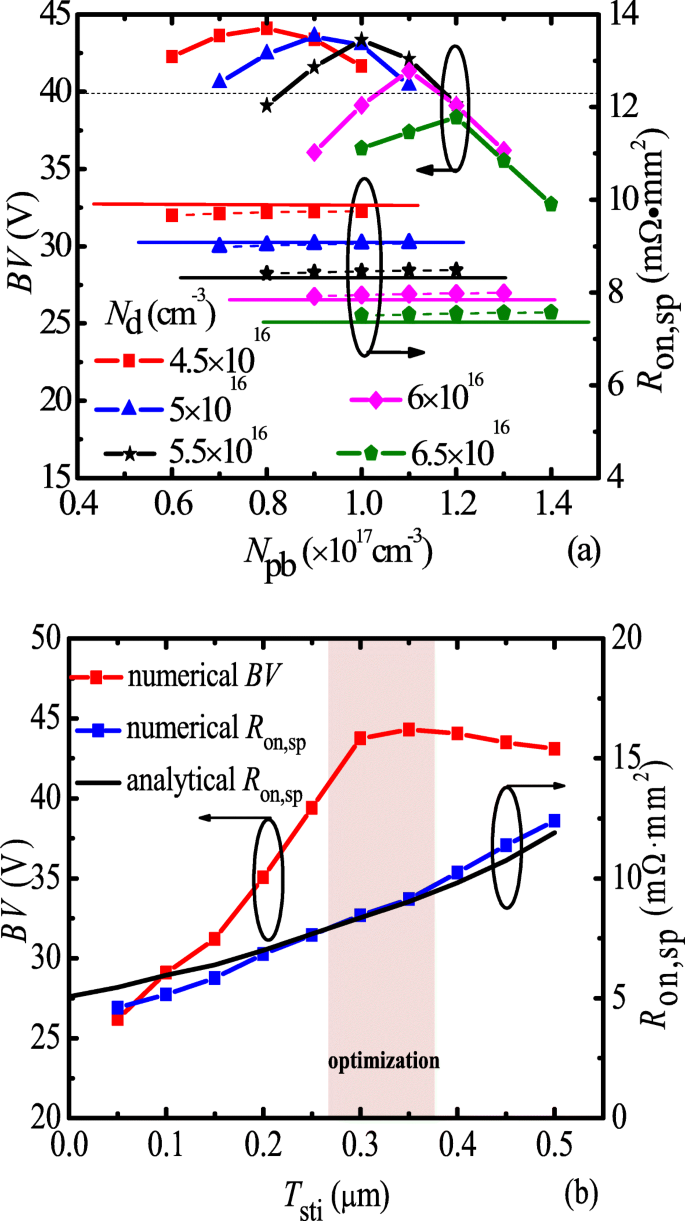

O equilíbrio de carga entre o desvio N e a camada enterrada em P parcial é necessário para atingir um alto BV. A Figura 5a mostra que BV e R numérica e analítica ligado, sp como funções da concentração de dopagem do P-enterrado ( N pb ) para diferentes N d . Para um dado N d , BV tem um valor máximo com N variado pb , e o máximo de BV aumenta com a diminuição de N d . No entanto, R ligado, sp pode ser aumentado como N d diminuindo. Devido a BV exigido superior a 40 V, o N d =5,5 × 10 16 cm −3 e N pb =1 × 10 17 cm −3 são escolhidos. A Figura 5b mostra BV e R numérica e analítica ligado, sp como funções da espessura da camada STI ( T sti ) T sti tem forte impacto no BV e R ligado, sp , e deve ser projetado e otimizado cuidadosamente, assim como nosso trabalho anterior [21]. Para T sti <0,3 μm, o ponto de ruptura sob a borda da placa de poli campo tem um alto pico de campo elétrico. Como T sti aumenta, o pico do campo elétrico é relaxado e, em seguida, BV aumenta. Para T sti =0,3 μm, BV de 43 V é obtido. Para T sti ≥ 0,3 μm, o pico do campo elétrico sob a borda da placa de campo poli é suficientemente baixo, como resultado, o ponto de ruptura é transferido para a junção P / N sob o lado do dreno. Como T sti aumenta, o VB aumenta e depois satura.

a Numérico (linha pontilhada) e analítico (linha sólida) BV e R ligado, sp como funções de N pb para diferentes N d . b Numérico (linha pontilhada) e analítico (linha sólida) BV e R ligado, sp como funções de T sti

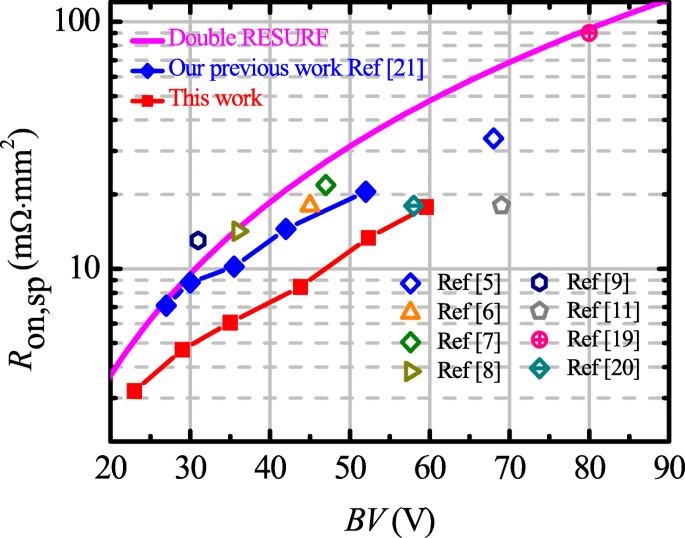

A Figura 6 mostra o benchmark das tecnologias Bipolar-CMOS-DMOS (BCD) existentes e o LDMOS proposto. Aparentemente, a tecnologia de processo para LDMOS proposta é compatível com nossa tecnologia BCD desenvolvida, que alcançou o melhor desempenho da classe de LDMOS. No processo de fabricação do LDMOS proposto, a camada N-enterrada poderia compartilhar a mesma máscara com o P-well. Para o LDMOS proposto, R ligado, sp é 8,5 mΩ · mm 2 enquanto BV =43 V, que é reduzido em cerca de 37% em comparação com nosso trabalho anterior.

O benchmark das tecnologias BCD existentes e o LDMOS proposto

Conclusão

Um novo LDMOS ultrabaixo específico em resistência com porta dupla aprimorada e camada parcialmente enterrada em P é proposto e investigado por simulação numérica neste artigo. Camada N-enterrada com alta concentração de dopagem é utilizada para alcançar porta dupla aprimorada com redução de R c . Camada P-enterrada parcial é introduzida sob a região N-drift para aumentar BV com manter o equilíbrio da carga. O processo de fabricação do LDMOS neste trabalho é compatível com a tecnologia BCD existente relatada em nosso trabalho anterior. O resultado mostra que o R ligado, sp do LDMOS proposto é reduzido em 37% no BV de 43 V em comparação com o trabalho anterior. Com a tecnologia de processamento de semicondutores indo para o nível nanométrico, o R ligado, sp pode reduzir ainda mais com a diminuição do comprimento do canal.

Abreviações

- BCD:

-

Bipolar-CMOS-DMOS

- BV:

-

Queda de tensão

- LDMOS:

-

Transistor semicondutor de óxido metálico difundido duplo lateral

- RESURF:

-

Reduz o campo de superfície

- R ligado, sp :

-

Resistência específica

- USTI:

-

Isolamento de trincheira ultra-rasa

Nanomateriais

- Nanofibras e filamentos para entrega aprimorada de drogas

- Características interfaciais, elétricas e de alinhamento de banda de pilhas de HfO2 / Ge com camada intermediária de SiO2 formada in situ por deposição de camada atômica aprimorada com plasma

- Um romance fotocatalisador de heterojunção Bi4Ti3O12 / Ag3PO4 com desempenho fotocatalítico aprimorado

- Efeito da Estabilidade Térmica Aprimorada da Camada de Suporte de Alumina no Crescimento de Nanotubos de Carbono de Parede Única Alinhados Verticalmente e Sua Aplicação em Membranas de Nanofiltraç…

- Influência de nanopartículas de Ag com diferentes tamanhos e concentrações incorporadas em uma camada compacta de TiO2 na eficiência de conversão de células solares de perovskita

- Potencial antiproliferativo e de desencadeamento de apoptose de nanopartículas lipídicas direcionadas à base de paclitaxel com internalização celular aprimorada por receptores de transferrina - u…

- Absorvedor omnidirecional pelo efeito do plasma vazio na região visível com campo elétrico localizado altamente aprimorado

- Transistor de efeito de campo SnSe2 com alta relação liga / desliga e fotocondutividade comutável por polaridade

- Nanomembranas de TiO2 fabricadas por deposição de camada atômica para eletrodo supercapacitor com capacitância aprimorada

- Nanofolhas porosas de ZnO com modificação de superfície parcial para separação de cargas aprimorada e alta atividade fotocatalítica sob irradiação solar