Integrado

Veja a série RTOS Revelado Este artigo continua a examinar os semáforos. Serviços utilitários de semáforo O Nucleus RTOS tem quatro chamadas API que fornecem funções utilitárias associadas aos semáforos:redefinir o semáforo, retornar informações sobre um semáforo, retornar o número de semáforo

Veja a série RTOS Revelado As caixas de correio foram apresentadas em um artigo anterior. Eles são talvez o segundo método mais simples de comunicação entre tarefas - depois dos sinais - com suporte do Nucleus SE. Eles fornecem um meio de baixo custo, mas flexível, de passar mensagens simples entr

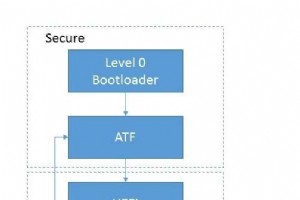

Desde o seu lançamento em 2011, a arquitetura do processador ARMv8 tornou-se bastante difundida no mercado de dispositivos móveis. De acordo com as previsões do CEO da ARM Limited, os processadores desta geração irão adquirir uma quota de mercado mundial de até 25% até 2020. É bastante natural que o

Nota do editor:Nosso bom amigo Max está procurando sugestões para calculadoras e solucionadores eletrônicos. Nada é muito grande ou muito pequeno. Diga a ele o que você acha que pode valer a pena incluir na lista de ferramentas do EEWeb.com. De vez em quando, um raio de sol inesperado atravessa a

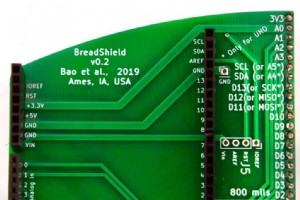

Recebo um número extraordinário de emails de pessoas que lançaram campanhas de crowdfunding para vários projetos. Isso provavelmente ocorre porque eu mesmo mergulhei nas águas do crowdfunding ocasionalmente, além do fato de que eu postei várias colunas sobre projetos que particularmente me atraíram.

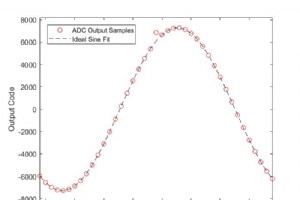

Conforme os conversores analógico-digital (ADCs) de alta velocidade aumentaram na taxa de amostragem, também aumentou o problema de erros de código - também conhecidos como códigos sparkle - nos dados de saída do ADC. Um erro de código é definido como um erro no código de saída de um ADC que excede

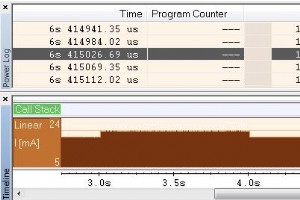

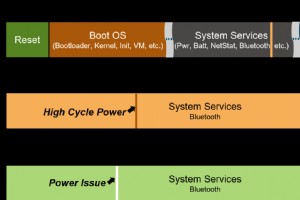

Em meu último post, “Fundamentos do modo de baixo consumo de energia do Arm Cortex-M”, exploramos os fundamentos dos modos de baixo consumo de energia que podem ser encontrados em todos os processadores Arm Cortex-M e como poderíamos aproveitar as instruções WFI e WFE para colocar um processador dor

O poder tende a custar; altos custos de energia altamente. Esta adaptação um tanto forçada da famosa citação de Lord Acton captura dois aspectos importantes do projeto de semicondutores e do consumo de energia. Observando o consumo médio de energia ao longo do tempo, fica claro que um chip com alto

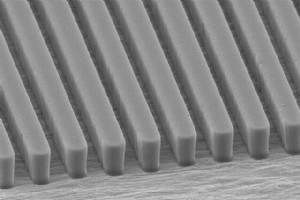

Nos últimos anos, vimos uma proliferação de novos aplicativos eletrônicos exigindo pacotes menores, novos formatos, menor consumo de energia e maior funcionalidade, incluindo processamento de sinal integrado, sensores, interfaces de imagem e componentes de gerenciamento de energia - todos integrados

Desde o surgimento do design eletrônico, onde existem designs, existem bugs. Mas onde havia bugs, inevitavelmente havia depuração, envolvida em uma luta épica com falhas, bugs e erros para determinar qual prevaleceria - e com que precisão. De muitas maneiras, a evolução da tecnologia de depuração

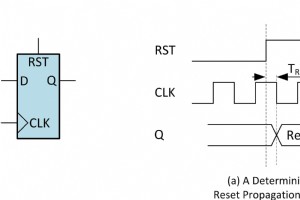

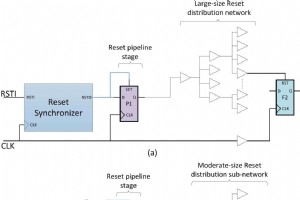

A falta de coordenação entre reinicializações assíncronas e relógios lógicos síncronos leva a falhas intermitentes na inicialização. Nesta série de artigos, discutimos os requisitos e desafios do reset assíncrono e exploramos soluções avançadas para projetos ASIC vs FPGA. Reinicializações assíncro

A falta de coordenação entre reinicializações assíncronas e relógios lógicos síncronos leva a falhas intermitentes na inicialização. Nesta série de artigos, discutimos os requisitos e desafios do reset assíncrono e exploramos soluções avançadas para projetos ASIC vs FPGA. Reinicializações assíncro

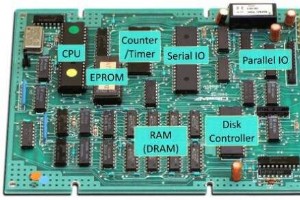

Há uma infinidade de Sistemas Operacionais em Tempo Real (RTOS) disponíveis na Internet (Clique Aqui para ver uma “pequena” lista). Muitas dessas ofertas, no entanto, agora são projetos mortos / sem manutenção. Dos restantes, a maioria tem suporte para apenas um microcontrolador ou uma família de

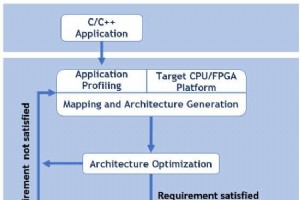

Recentemente, Brian Bailey organizou uma mesa redonda que resultou em um artigo de duas partes chamado Supporting CPUs Plus FPGAs . Os especialistas discutiram a realidade em evolução do design de sistemas baseados em FPGAs e CPUs. Esta discussão aborda os desenvolvimentos recentes no fluxo de des

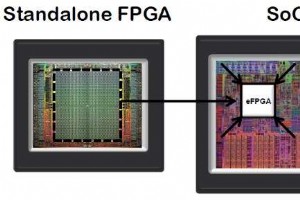

Há muito tempo estou interessado na tecnologia que sai do Achronix. Eles chamaram meu interesse pela primeira vez por volta de 2004/2005 com seu tecido FPGA assíncrono. Eventualmente, isso conseguiu atingir velocidades equivalentes a um FPGA síncrono com clock de 2 GHz (se é que existia tal besta),

Os fones de ouvido estéreo auditáveis e verdadeiramente sem fio estão ganhando popularidade, mas ainda estão longe de atingir seu potencial máximo. Esses minúsculos dispositivos podem transformar a maneira como as pessoas interagem com o ambiente, adicionando capacidades auditivas aprimoradas, div

Nota do editor:o design sem fio pode frustrar os melhores planos para o desenvolvimento de dispositivos conectados. Em particular, uma linha de alimentação de antena projetada incorretamente pode ser difícil de descobrir até o final do desenvolvimento durante o teste. Aqui está uma amostra de um bom

Nos últimos anos, avanços significativos no reconhecimento automático de voz (ASR) levaram a uma abundância de dispositivos e aplicativos que usam a voz como sua interface principal. O espectro IEEE a revista declarou 2017 o ano do reconhecimento de voz; A ZDNet relatou da CES 2017 que a voz é a p

Durante o curso da minha carreira, estive envolvido no desenvolvimento de uma série de designs de FPGA para alguns projetos realmente interessantes. Infelizmente, também estive envolvido no resgate de vários projetos de FPGA que se perderam. Conforme eu trabalhava nesses designs de problemas, tornou

O termo 5G - significando a quinta geração de rede móvel ou sistemas sem fio - está aparecendo cada vez mais nos dias de hoje. Fala-se de implantações iniciais já em 2020. O que é menos falado é o fato de que os padrões 5G ainda estão sendo considerados e definidos, e muitos aspectos ainda estão em

Integrado