Transistores de efeito de campo InSe bidimensionais de alto desempenho com novo contato ôhmico em sanduíche para nós sub-10 nm:um estudo teórico

Resumo

O transistor de efeito de campo (FET) bidimensional (2D) baseado em InSe mostrou notável mobilidade de portadora e alta relação liga-desliga em relatórios experimentais. Investigações teóricas também previram que o alto desempenho pode ser bem preservado em nós abaixo de 10 nm no limite balístico. No entanto, tanto a experiência experimental quanto os cálculos teóricos apontaram que a obtenção de alta qualidade ôhmica tornou-se o principal fator limitante para FET 2D de alto desempenho. Neste trabalho, propusemos um novo contato ôhmico imprensado com índio para InSe FET e avaliamos exaustivamente seu desempenho a partir de visualizações de material e dispositivo com base em métodos ab initio. As propriedades do material denotam que todas as questões fundamentais do contato ôhmico, incluindo a barreira de tunelamento, a barreira Schottky e dopagem efetiva, estão bem relacionadas com a introdução da estrutura em sanduíche, e uma excelente resistência de contato foi alcançada. No nível de desempenho do dispositivo, os dispositivos com comprimento de porta de 7, 5 e 3 nm foram investigados. Todas as métricas de dispositivos de contato em sanduíche excedem em muito os requisitos do International Technology Roadmap for Semiconductors (ITRS) e exibem uma promoção óbvia em comparação com as estruturas convencionais. Aumento máximo de corrente com 69,4%, 50% e 49% são obtidos para dispositivos com comprimento de porta de 7, 5 e 3 nm, respectivamente. Enquanto isso, a redução máxima do atraso intrínseco com 20,4%, 16,7% e 18,9% são atingidos. Além disso, é apresentado um benchmark de produto de atraso de energia (EDP) em relação a outros FETs 2D. Todos os FETs InSe com contato ôhmico imprensado superam MoS 2 FETs, bem como requisitos do ITRS 2024. O melhor resultado se aproxima do limite superior do FET BP ideal, denotando preponderância superior de estruturas em sanduíche para FETs InSe na próxima geração de tecnologia de semicondutor de óxido metálico complementar (CMOS).

Introdução

Semicondutores bidimensionais (2D) têm atraído muito interesse em dispositivos eletrônicos devido às suas aplicações atraentes para a próxima geração de tecnologia de semicondutor de óxido metálico complementar (CMOS) [1, 2]. Sua espessura ultrafina e boa propriedade dielétrica podem fornecer excelente controle de porta eletrostática para suprimir os conhecidos efeitos de canal curto [3]. Além disso, como poucas camadas de materiais 2D geralmente possuem superfície lisa com falta de ligações pendentes, a mobilidade de portadores de superioridade de materiais 2D pode ser bem preservada em sistemas corporais ultrafinos em comparação com semicondutores convencionais [4]. Exceto para o grafeno sem intervalos, a maioria dos semicondutores 2D sintetizados como dichalcogenetos de metais de transição (TMDs), fósforo preto (BP) e seleneto de índio (InSe) possuem band gap zero e são demonstrados como adequados para transistor de efeito de campo (FET ) FETs baseados em TMDs mostraram alta relação liga-desliga, tanto quanto 10 8 e baixa corrente de fuga em dispositivos de canal curto, beneficiando-se da grande massa efetiva [5]. Os FETs baseados em BP apresentaram características de corrente e comutação excelentes [6], devido à alta mobilidade de ~ 1000 cm 2 / V se propriedade de transporte anisotrópico [7]. Recentemente, o InSe demonstrou apresentar uma mobilidade superior de ~ 2000 cm 2 / V s à temperatura ambiente [8, 9] e FET com base em InSe revelou uma alta proporção liga-desliga de 10 8 [10]. Cálculos de primeiro princípio também identificaram que o InSe FET pode ser bem reduzido a sub-10 nm no limite balístico [11, 12]. No entanto, devido ao desprezo da resistência de contato e à hipótese de forte dopagem, aproximar-se do limite teórico ainda é um desafio em aplicações reais. Na verdade, como o método de dopagem confiável e a forma de contato ôhmico de alta qualidade ainda estão faltando, os FETs baseados em materiais 2D incluindo InSe são geralmente FET de barreira Schottky (SB) [13,14,15,16]. O SB nas regiões ativas produz grande resistência de contato e baixo nível de dopagem degrada ainda mais a densidade de corrente. Alcançar baixa resistência de contato com regiões ativas suficientemente dopadas tornou-se o principal fator limitante para FET baseado em materiais 2D (2D FET) para atingir alto desempenho [17,18,19].

Visando as questões acima, propusemos um novo contato ôhmico imprensado para InSe FET. O índio foi selecionado como o metal do eletrodo, pois estudos experimentais e teóricos recentes sugerem que o índio pode ser um candidato promissor para que o InSe FET alcance um bom desempenho [20,21,22]. Teoricamente, avaliamos a qualidade de contato ôhmico e o desempenho de dispositivos com comprimento de porta de 7, 5 e 3 nm seguindo a estrutura do International Technology Roadmap for Semiconductors 2013 (ITRS) [23]. Deve-se notar que embora o ITRS tenha sido substituído pelo International Roadmap for Devices and Systems (IRDS) [24], o ITRS2013 apresenta uma tendência de escala clara para transistores e ainda foi adotado em estudos recentes [25, 26]. Este manuscrito está organizado da seguinte forma:primeiro, as propriedades elétricas dos contatos em sanduíche e convencionais (superiores) são investigadas. Em segundo lugar, as métricas de desempenho do dispositivo, como corrente no estado e atraso intrínseco, são avaliadas e comparadas com os requisitos do ITRS. Finalmente, o benchmark de produto de atraso de energia versus atraso intrínseco é apresentado para comparar com outros dispositivos baseados em materiais 2D.

Métodos

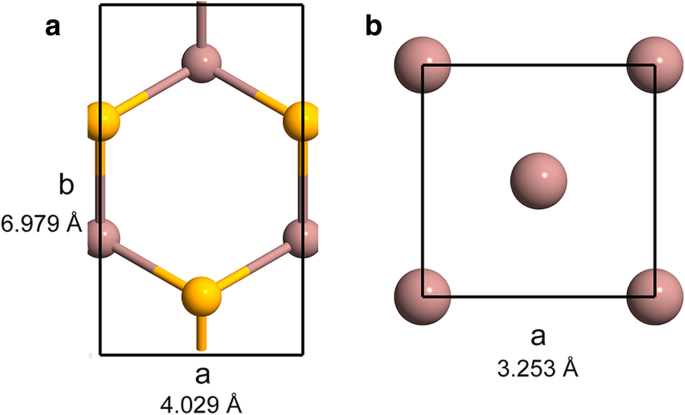

Todas as estruturas atômicas foram otimizadas por VASP [27]; corte de energia de 335 eV foi empregado durante todos os cálculos. A célula unitária do InSe foi relaxada com o critério de estresse de 0,01 eV / Å sob a estrutura do MetaGGA do SCAN [28]. Os parâmetros de rede do índio metálico foram obtidos do manual de química e física [29]. Conforme mostrado na Fig. 1, a constante de rede do InSe é 4,029 Å, que está em muito boa concordância com relatórios experimentais [30, 31].

Vista superior da célula unitária para InSe ( a ) e índio ( b ), respectivamente

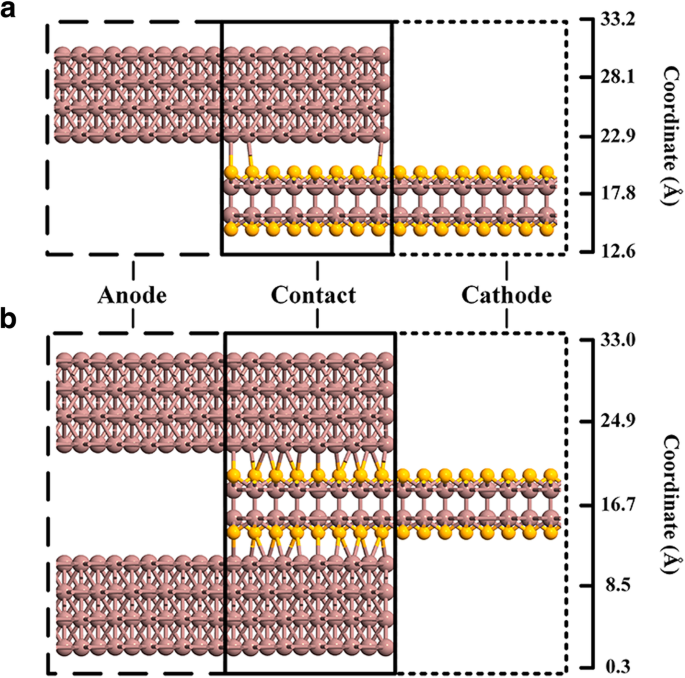

A estrutura inicial do índio no InSe foi construída com células unitárias 4 × 1 × 1 e 5 × 2 × 1 de InSe e superfície do índio (001), respectivamente. A deformação absoluta média foi de 1,32%, o que é suficiente para preservar as propriedades intrínsecas do material. Conforme mostrado na Fig. 2a, b, a estrutura em sanduíche foi construída com camadas de índio / InSe / índio, o índio dos lados inferior e superior tem simetria espelhada com centro de InSe. Ambas as estruturas híbridas foram relaxadas com van der Waals (vdW) funcional de optb88 com critério de força em cada átomo inferior a 0,02 eV / Å [32, 33]. A área de contato final é 16,19 Å × 6,41 Å. A resistência do contato ôhmico foi então avaliada por um dispositivo de duas sondas como mostrado nas Fig. 2a, b. Livrando-se da resistência desnecessária do semicondutor fora das regiões de contato, o InSe no cátodo foi fortemente dopado com 1 × 10 14 e / cm 2 para contatos superiores e intercalados.

Estruturas atômicas de contato e dispositivo de duas sondas relacionado usado para avaliação da resistência de contato. a , b são para contatos superiores e intercalados, respectivamente . As coordenadas denotam a localização dos átomos na direção fora do plano

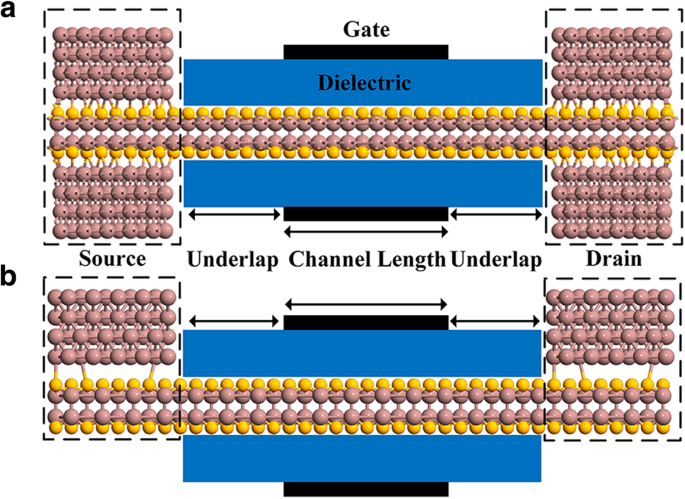

Quanto à avaliação do desempenho do dispositivo, a geometria do InSe FET com contatos ôhmicos em sanduíche e no topo é mostrada na Fig. 3a, b, respectivamente. Todos os dispositivos e nomes de nós seguem os requisitos de ITRS e IRDS, respectivamente. Os parâmetros do dispositivo estão listados na Tabela 1. Para suprimir o tunelamento intrabanda, subposição de 1 nm (UL) foi aplicada a um comprimento de porta de 3 nm. Ao contrário da modelagem de contato ôhmico, nenhuma das partes dos dispositivos foi dopada intencionalmente. Os dispositivos foram construídos combinando a fonte, o dreno e o canal ao longo da direção do transporte. O canal e suas duas interfaces com regiões ativas foram adicionalmente relaxadas com fonte e dreno fixos. Todas as simulações foram baseadas na teoria da função de Green de não equilíbrio (NEGF) e realizadas por QuantumATK com cálculo totalmente autoconsistente [34,35,36], que geralmente foi empregado para projetar e investigar transistores em nós sub-10 nm [17 , 37,38,39]. O conjunto de base polarizada duplo-zeta foi empregado com corte mecânico de 90 Rydberg. A malha de k-point do pacote de Monkhorst foi amostrada com densidade de 8 / Å −1 × 11 / Å −1 × 180 / Å −1 . O solucionador de gradiente conjugado paralelo é escolhido como o solucionador de Poisson por uma questão de eficiência. A corrente de todos os dispositivos pode ser obtida resolvendo a fórmula de Landauer-Büttiker [40]:

$$ I \ left ({V} _ {\ mathrm {Bias}} \ right) =\ frac {2e} {h} \ int T \ left (E, {V} _L, {V} _R \ right) \ esquerda [{f} _ {\ mathrm {R}} \ esquerda (E, {V} _R \ direita) - {f} _L \ esquerda (E, {V} _L \ direita) \ direita] dE $$

Geometrias de FETs InSe com sanduíche ( a ) e superior ( b ) Contatos

Onde, V Polarização é o preconceito e pode ser alcançado por: V Polarização = V R - V L , T ( E , V L , V R ) é o coeficiente de transmissão das portadoras, f R ( E , V R ) e f L ( E , V L ) são a função de distribuição de Fermi-Dirac para cátodo (dreno) e ânodo (fonte), respectivamente.

Resultados e discussão

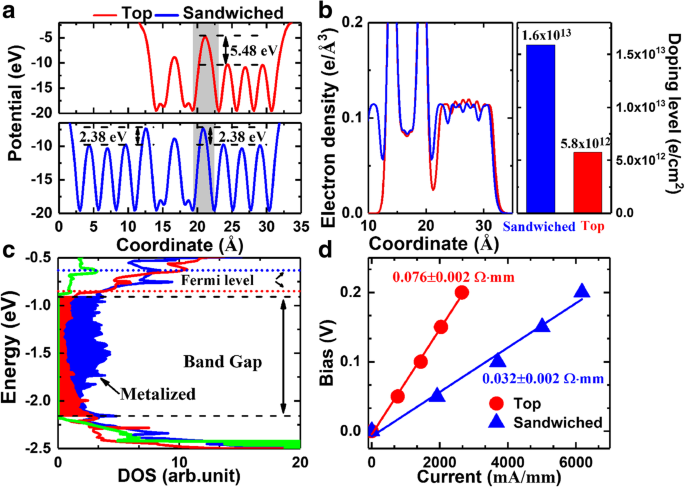

Em geral, existem três fatores-chave correlacionados à qualidade de contato ôhmico em materiais 2D [18], ou seja, a barreira de tunelamento e a distância que é derivada da lacuna vdW, sobreposição orbital entre o eletrodo e o semicondutor e também a altura SB. Primeiro, a barreira de tunelamento e a distância foram descritas pelo potencial efetivo mostrado na Fig. 4a. Em comparação com o contato superior, a introdução do contato em sanduíche não apenas fornece um caminho de transporte adicional no lado inferior, mas também dá origem a uma diminuição da barreira de tunelamento de 5,48 para 2,38 eV, levando a uma redução de 56,6%. Enquanto isso, a distância interfacial também fica ligeiramente reduzida com 0,66 Å, denotando que a largura da barreira de tunelamento também fica reduzida. Em segundo lugar, a sobreposição orbital pode ser avaliada a partir da distribuição de carga de valência na Fig. 4b. Pode-se notar que o contato em sanduíche possui mais elétrons de valência na região interfacial em comparação com o contato superior, indicando uma sobreposição orbital mais forte entre o índio e o InSe. Este recurso também ajuda a introduzir o efeito de dopagem no InSe, e o número de elétrons em excesso pode ser calculado usando a população de Mulliken. Extraímos o número total de elétrons em InSe de estruturas em sanduíche e de contato superior, respectivamente. Então, o nível de dopagem pode ser obtido dividindo-se o número de elétrons pela área da região de contato, já que a carga líquida do InSe isolado deve ser sempre zero. Conforme mostrado no painel direito da Fig. 4b, o contato imprensado produz um nível de dopagem muito alto de 1,6 × 10 13 e / cm 2 , que é quase 2,8 vezes maior do que o contato superior. Um nível tão alto aproximou a hipótese em simulações de FET de tunelamento 2D, que normalmente afirma um nível de dopagem muito mais pesado do que o FET de óxido metálico-semicondutor. Em terceiro lugar, a densidade de estados (DOS) de InSe em estruturas pristinas, em sanduíche e em contato com o topo são mostradas na Fig. 4c. A sobreposição orbital entre o índio e o InSe na região interfacial metalizou a lacuna de banda do InSe, e o ensanduichado resulta em um nível mais alto. Esse recurso aumenta muito a injeção de portadora através da barreira de tunelamento vdW na região interfacial, pois os estados metalizados no gap de banda oferecem canais de tunelamento adicionais. Além disso, os níveis de Fermi são colocados acima do mínimo da banda de condução, resultando em degeneração de energia de ~ 0,07 e 0,27 eV para contatos de topo e sanduíche, respectivamente. Portanto, os SB entre o índio e o InSe são completamente eliminados. Em quarto lugar, a resistência de contato ôhmica foi calculada com base na curva de polarização-corrente obtida dos dispositivos de duas sondas, e todos os resultados são mostrados na Fig. 4d. Podemos notar que ambos os contatos são ôhmicos devido às evoluções lineares. No nível teórico, isto é, negligenciando a rugosidade da superfície, impurezas interfaciais, etc., a estrutura em sanduíche leva a um valor de contato muito baixo de 0,032 ± 0,002 Ω mm, o que reduz mais da metade da resistência do contato superior. Com base nas discussões acima, é interessante notar que o dobro da região de contato sempre leva a uma melhora de mais do que o dobro do contato ôhmico. Como o contato superior com índio foi recentemente confirmado experimentalmente como sendo eficaz para aumentar o desempenho de dispositivos baseados em InSe [21, 22], a estrutura em sanduíche pode ser uma solução de contato ôhmico atraente para FETs InSe.

a Potencial efetivo normal para a direção do transporte. A coordenada corresponde à localização dos átomos e é definida na Fig. 1. As regiões escuras correspondem ao gap vdW. b Distribuição de elétrons de média plana normal à direção de transporte. O painel direito é o nível de dopagem. A coordenada corresponde à localização dos átomos e é definida na Fig. 1. c DOS do InSe. O verde corresponde ao InSe primitivo. d Polarização dependente da corrente dos dois dispositivos de sondagem. Todo o vermelho e o azul correspondem aos contatos superiores e intercalados, respectivamente

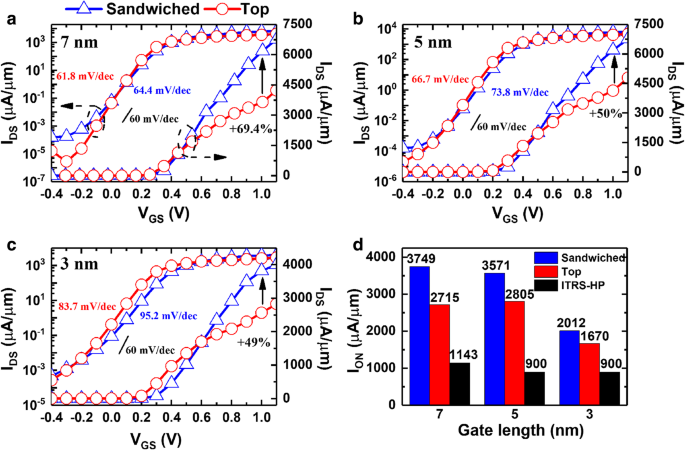

Em seguida, o desempenho do dispositivo foi avaliado, e as características de transferência do InSe FET em 2019, 2021 e 2024 nós foram mostradas na Fig. 5. Pode-se observar que as oscilações de subliminar (SS) de todos os nós estão abaixo de 100 mV / dec , e SS no nó 2019 mostra características de comutação quase ideais de 61,8 e 64,4 mV / dec para dispositivos de contato superior e em sanduíche, respectivamente, indicando excelente controle eletrostático em InSe FETs. Além disso, os dispositivos de contato em sanduíche levam a uma melhoria evidente do I DS em comparação com os principais com aumento máximo de 69,4%, 50% e 49% sendo alcançado em 2019, 2021 e 2024 nós, respectivamente. Além disso, eu LIGADO foi extraído seguindo o requisito de alto desempenho (HP) no ITRS. Conforme mostrado na Fig. 5d, I LIGADO de todos os sistemas está muito acima dos requisitos da HP. Em comparação com os dispositivos de contato superior, os sistemas em sanduíche ainda apresentam uma promoção de 38,2%, 27,3% e 20,5% para 2019, 2021 e 2024 nós, respectivamente.

Transferir características de FETs InSe no nó. a 2019, b 2021 e c 2.024 nós, respectivamente. d Comparações de I ON seguindo os requisitos da HP de ITRS

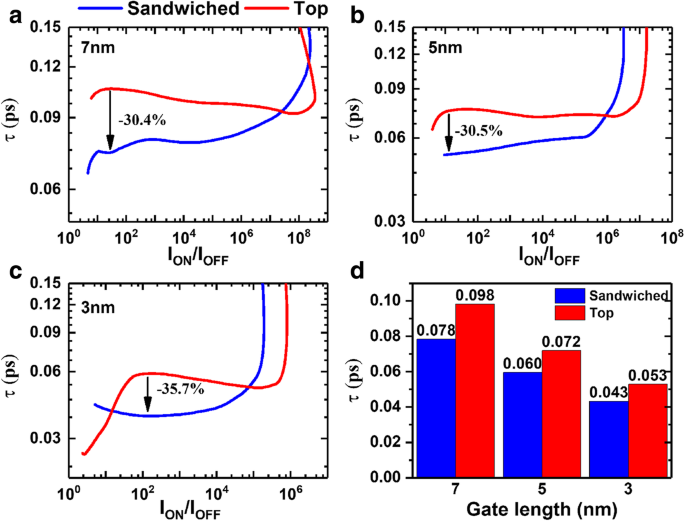

Outra métrica essencial do FET é o atraso intrínseco (τ), que significa o limite superior da velocidade de chaveamento no circuito lógico. O τ foi obtido por τ =(Q LIGADO - Q OFF ) / I LIGADO , onde Q ON e Q OFF são cobranças nos estados ligado e desligado, respectivamente. Os estados ligado e desligado são restringidos em | V DS | =0,68, 0,64 e 0,64 V para 2019, 2021 e 2024 nós, respectivamente. O atraso intrínseco em função da relação liga-desliga é mostrado na Fig. 6. Apesar da evolução não monotônica no grande atraso que é derivado do tunelamento sob baixas tensões de porta [41], todos os atrasos estão abaixo de 0,15 ps e são suficientemente reduzidos do que o requisito ITRS de 0,44-0,46 ps. Além disso, os dispositivos de contato em sanduíche dão origem a uma redução de mais de 30% nas regiões de I LIGADO / I DESLIGADO ≤ 10 7 , 10 6 , 10 5 para nós de 2019, 2021 e 2024, respectivamente. Com base nos requisitos de HP mostrados na Fig. 6d, os dispositivos de contato em sanduíche ainda podem promover a velocidade de comutação com 20,4%, 16,7% e 18,9% para 2019, 2021 e 2024 nós, respectivamente.

Atraso intrínseco em função da relação liga-desliga no nó. a 2019, b 2021 e c 2.024 nós, respectivamente. d Comparações de atraso intrínseco seguindo o requisito HP de ITRS

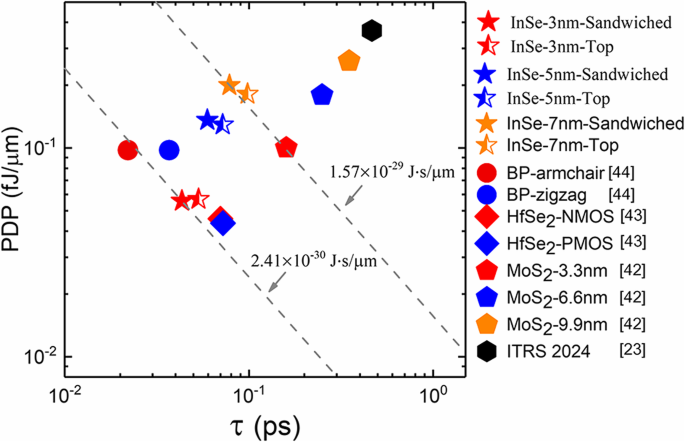

Para avaliar o desempenho do dispositivo de forma mais intuitiva, o produto de atraso de energia (PDP) versus atraso intrínseco é extraído. PDP corresponde ao consumo de energia em um único evento de comutação e é definido por PDP =(Q ON - Q OFF ) V DS com todos os parâmetros derivados dos requisitos da HP de ITRS. Os resultados e a comparação com outros FETs 2D são mostrados na Fig. 7. Em primeiro lugar, todos os FETs 2D foram selecionados com base na regra de que foram preliminarmente verificados como transistores em relatórios experimentais, o que vai um passo adiante para a tecnologia CMOS. Em segundo lugar, exceto para InSe e MoS 2 [42], todos os outros dispositivos foram simulados com forte dopagem em regiões ativas e negligência da resistência de contato ôhmica [43, 44], portanto, os resultados correspondem ao limite superior de desempenho. Como pode ser visto, todos os produtos de atraso de energia (EDP) estão abaixo do requisito ITRS 2024, indicando o futuro atraente dos FETs 2D. O máximo de EDP pertence ao MoS 2 FET a 9,9 nm, e o melhor é de BP FET. Quanto aos FETs InSe, os dispositivos em contato intercalados sempre têm um desempenho melhor do que os com contato superior em todos os nós. O EDP mais alto de dispositivos em contato em sanduíche está no comprimento de porta de 7 nm (nó de 2019) e excede todos os MoS 2 FETs. O mais baixo está no comprimento de porta de 3 nm (nó de 2024) e até se aproxima do limite superior do FET BP na direção da poltrona, que é bem conhecido pelas excelentes propriedades de transporte. Consequentemente, o EDP do InSe FET significa que os dispositivos em contato sanduíche exibem competitividade suficiente entre os FETs 2D.

Produto de atraso de energia versus atraso intrínseco composto de InSe e outros FETs 2D. As orientações tracejadas em cinza correspondem a EDP específico

Conclusões

Neste trabalho, um novo contato ôhmico imprensado com índio foi proposto para o InSe FET. O contato ôhmico imprensado não apenas duplica a região de contato, mas também promove a qualidade do contato mais do que o dobro, levando a uma excelente resistência de contato. No nível de desempenho do dispositivo de comprimento de porta 7, 5 e 3 nm, os FETs InSe com contato ôhmico imprensado apresentam promoção de desempenho universal em comparação com dispositivos convencionais de contato superior. De acordo com o requisito de HP do ITRS, a corrente no estado e o atraso intrínseco são aprimorados em 38,2 ~ 20,5% e 20,4 ~ 16,7%, respectivamente. Um benchmark de EDP contra outros FETs 2D também revela que os FETs InSe com contato ôhmico imprensado têm vantagens sobre outros FETs 2D. Nosso estudo oferece uma nova rota para FETs InSe de alto desempenho.

Disponibilidade de dados e materiais

Os conjuntos de dados usados e / ou analisados durante o estudo atual estão disponíveis junto ao autor correspondente, mediante solicitação razoável.

Abreviações

- 2D:

-

Bidimensional

- CMOS:

-

Semicondutor de óxido metálico complementar

- TMDs:

-

Dichalcogenetos de metais de transição

- BP:

-

Fósforo preto

- InSe:

-

Seleneto de índio

- FET:

-

Transistores de efeito de campo

- SB:

-

Barreira Schottky

- 2D FET:

-

FET baseado em materiais 2D

- ITRS:

-

Roteiro de tecnologia internacional para semicondutores

- vdW:

-

van der Waals

- UL:

-

Underlap

- NEGF:

-

Função de Green fora de equilíbrio

- DOS:

-

A densidade de estados

- SS:

-

Balanço de sublimiar

- HP:

-

Alta performance

- τ:

-

Atraso intrínseco

- PDP:

-

Produto com atraso de energia

- EDP:

-

Produto com retardamento de energia

Nanomateriais

- Espaçadores de ar para chips de 10 nm

- Nexam fornecerá Diab com Nexamite de melhoria de propriedades para espuma PET de alto desempenho

- Fibras de carbono ativado com nanoestrutura hierárquica derivada de luvas de algodão como eletrodos de alto desempenho para supercondensadores

- Transistores de efeito de campo Nanoflake SnSe multicamadas com contatos óhmicos de baixa resistência

- O estudo de um novo sistema micelar em forma de verme aprimorado por nanopartículas

- Evolução da área de contato com carga normal para superfícies rugosas:de escalas atômicas a macroscópicas

- Deposição de camada atômica de nanofilmes de óxido de índio para transistores de filme fino

- Microarranjos mesoporosos de VO2 bidimensional para supercapacitor de alto desempenho

- Transistores de efeito de campo ferroelétricos baseados em padrões de faixa de micron-largas dominadas por nanotubo de carbono de parede única com camada de controle de defeito de HfO2

- Uma nova microestrutura de cluster de nanocônios com propriedades anti-reflexo e superhidrofóbicas para dispositivos fotovoltaicos