Ge pMOSFETs de alta mobilidade com passivação de Si amorfo:impacto da orientação da superfície

Resumo

Relatamos a passivação amorfa de Si de pMOSFETs Ge fabricados em superfícies orientadas (001) -, (011) - e (111) para aplicações avançadas de CMOS e transistores de filme fino. A passivação do Ge pelo Si amorfo é realizada por pulverização catódica de magnetrão à temperatura ambiente. Com a espessura fixa de Si t Si , (001) Ge pMOSFETs orientados alcançam a maior corrente no estado I LIGADO e mobilidade efetiva do orifício μ eff em comparação com os dispositivos em outras orientações. Em uma densidade de carga de inversão Q inv de 3,5 × 10 12 cm −2 , Transistores Ge (001) com 0,9 nm t Si demonstrar um pico μ eff de 278 cm 2 / V × s, que é 2,97 vezes maior do que a mobilidade universal Si. Com a diminuição de t Si , eu LIGADO de transistores Ge aumenta devido à redução da espessura capacitiva efetiva, mas as características de oscilação subliminar e piso de vazamento são degradadas atribuídas ao aumento do intervalo médio D it .

Histórico

O germânio (Ge) tem atraído enormes interesses de pesquisa para aplicações avançadas de CMOS e transistores de filme fino devido à sua maior mobilidade de orifício e menor processamento de orçamento térmico em comparação com o Si [1,2,3,4,5,6]. Para alcançar a alta mobilidade do canal, o processo de passivação da superfície que leva a uma alta qualidade de interface é necessário antes da formação da pilha de portas. Várias técnicas de passivação de superfície foram desenvolvidas para fornecer os benefícios da mobilidade do portador em transistores de efeito de campo semicondutores de óxido metálico Ge (MOSFETs) [1, 2, 7,8,9,10]. Dentre essas técnicas, um tampão de silício (Si) passivado em Ge tem sido o hotspot nos últimos anos, devido às suas vantagens de supressão efetiva de estados de interface e boa estabilidade térmica e confiabilidade [11]. A formação da tampa de passivação de Si foi amplamente estudada usando deposição química de vapor (CVD) com precursores de SiH 4 [1], Si 2 H 6 [4], Si 3 H 8 [12] e evaporação do feixe E [13]. Embora o método CVD possa fornecer uma camada de passivação mais uniforme sobre a deposição física de vapor (PVD), sua taxa de passivação tem uma forte correlação na orientação da superfície do canal e na temperatura do processo. A técnica PVD pode fornecer a taxa de passivação melhorada mesmo em temperatura ambiente, que tem as vantagens de baixo orçamento térmico e baixo custo, tornando-a mais adequada para transistores de filme fino e aplicações de integração 3D de back-end-of-line. Nesta carta, nós fabricamos pMOSFETs Ge de alta mobilidade em superfícies orientadas (001) -, (011) - e (111) utilizando a passivação de Si amorfo por pulverização catódica de magnetron. Mobilidade efetiva do orifício significativamente melhorada μ eff é alcançado em transistores Ge em comparação com a mobilidade universal Si. Impactos da orientação da superfície e espessura de Si t amorfo Si no efeito de aumento da passivação de Si amorfo em μ eff são estudados.

Métodos

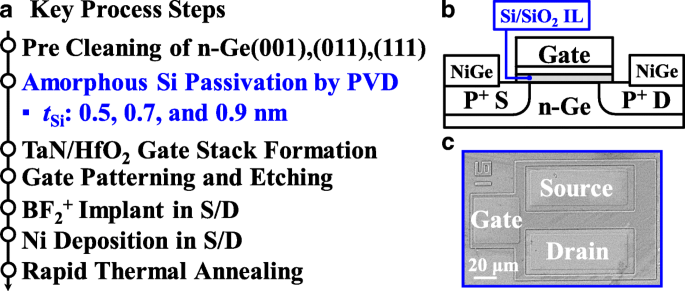

A Figura 1a mostra as principais etapas do processo para a fabricação de Ge pMOSFETs em superfícies orientadas (001) -, (011) - e (111). Após a limpeza do pré-portão em solução diluída de HF (1:50), a camada de passivação de Si amorfo ultrafina foi depositada em substratos n-Ge por pulverização catódica magnetron a uma potência alvo de 50 W. Três durações de passivação de 60 s, 80 s e 100 s foram usados correspondendo à deposição de 0,5, 0,7 e 0,9 nm t si , respectivamente. Depois disso, um HfO 2 de 5 nm de espessura o dielétrico de porta foi depositado a 250 ° C por deposição da camada atômica usando TDMAHf e H 2 O como precursores de Hf e O, respectivamente. Um eletrodo de porta TaN de 50 nm foi depositado por pulverização catódica reativa. Em seguida, o eletrodo da porta foi padronizado e gravado, o que foi seguido por BF 2 + implantação nas regiões de fonte / dreno (S / D) a 30 KeV com uma dose de 1 × 10 15 cm - 2 . Metais S / D não autoalinhados de níquel 15 nm foram formados pelo processo lift-off. Finalmente, o recozimento térmico rápido a 400 ° C foi realizado para ativação de dopante e metalização S / D. A Figura 1b mostra o esquema transversal do Ge pMOSFET com Si / SiO 2 camada interfacial (IL). A Figura 1c mostra a imagem do microscópio de vista superior de um Ge pMOSFET fabricado.

a Sequência do processo mostrando as etapas principais empregadas para fabricar os Ge pMOSFETs com diferentes t Si . b Esquemático transversal de um Ge pMOSFET com SiO 2 IL. c Imagem do microscópio de visão superior de um Ge pMOSFET fabricado

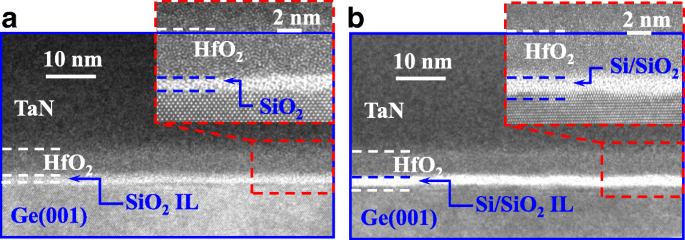

A Figura 2a, b mostra as imagens do microscópio eletrônico de transmissão (TEM) da pilha de portas de alta κ / metal com SiO 2 / Si camada interfacial (IL) no canal Ge (001) com t Si de 0,5 e 0,9 nm, respectivamente. As inserções mostram as imagens TEM de alta resolução (HRTEM) das amostras. Para o dispositivo com um t Si de 0,5 nm, a camada amorfa de Si foi completamente oxidada, enquanto para o dispositivo com 0,9 nm t Si , cerca de duas monocamadas de Si permaneceram após as etapas de recozimento subsequentes.

Imagens TEMS transversais de pilhas de gate Ge pMOSFET com a 0,5 nm t Si e b 0,9 nm t Si . Imagens HRTEM em inserções mostram que Si / SiO 2 IL é formado entre HfO 2 e canal Ge

Resultados e discussão

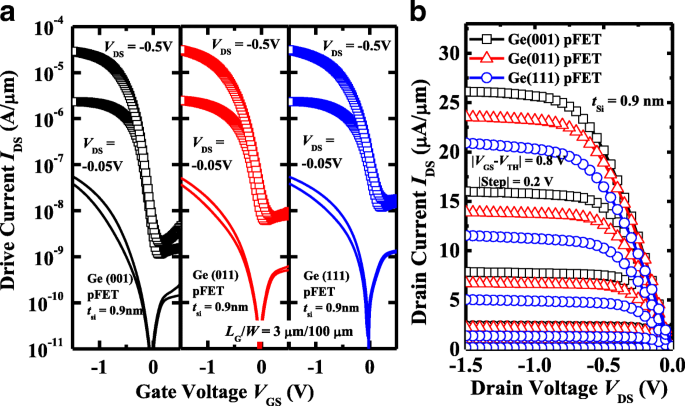

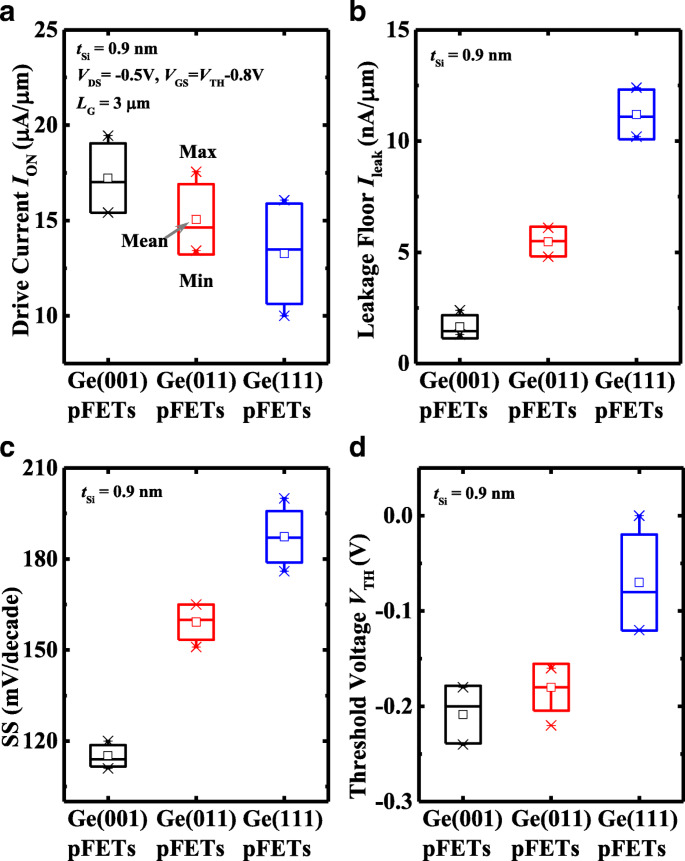

A Figura 3a representa o I medido DS - V GS e eu G - V GS curvas dos pMOSFETs Ge típicos em (001) -, (011) -, e (111) - superfícies orientadas com 0,9 nm t Si , que mostram as excelentes características de transferência. Todos os transistores têm um comprimento de porta L G de 3 μm e uma largura de portão W de 100 μm. A direção do canal é [110] para todas as orientações. O eu DS - V DS curvas dos dispositivos medidos em diferentes overdrive de portão V GS - V TH são mostrados na Fig. 3b. Aqui, tensão de limiar V TH é definido como o V GS em eu DS de 10 −7 A / μm. Observa-se que Ge (001) pMOSFET atinge a maior corrente de acionamento I LIGADO em comparação com os transistores nas superfícies (011) e (111) no V fixo GS - V TH . Posteriormente, mostraremos que isso é atribuído ao fato de que Ge (001) pMOSFETs têm uma maior mobilidade efetiva de orifício μ eff em comparação com os dispositivos nas outras duas orientações de superfície. Realizamos uma comparação abrangente de desempenho elétrico para os dispositivos com o t fixo Si de 0,9 nm, incluindo I LIGADO , piso de vazamento I vazamento , oscilação de sublimiar (SS) e V TH características. eu vazamento é definido como o mínimo I DS em V DS de - 0,05 V. A Figura 4a apresenta o gráfico estatístico do I LIGADO para Ge pMOSFETs em várias orientações, e I LIGADO foi definido como I DS em um V DS de - 0,5 V e um V GS - V TH de - 0,8 V. Todos os transistores neste gráfico têm o L G de 3 μm e W de 100 μm. (001) - dispositivos orientados exibem a média melhorada I LIGADO em comparação com as orientações (011) e (111), que é atribuído ao μ superior eff . A Figura 4b compara o I vazamento para os dispositivos, mostrando que os transistores Ge (001) têm o menor I vazamento deles, e Ge (011) pMOSFETs têm o menor I vazamento do que dispositivos orientados para (111). Deve-se notar que o eu vazamento é determinado pela corrente reversa do p + junção / n na região do dreno, que é afetada pela concentração de dopagem do tipo n de fundo no substrato Ge e ativação do p + implantado dopantes. As concentrações de dopagem do tipo n nas bolachas com várias orientações não são exatamente as mesmas. A orientação da superfície afeta a taxa de ativação de dopante e a qualidade de recristalização das regiões S / D. Além disso, embora o eu G é inferior a I DS antes da ativação dos transistores, isso influenciaria o I vazamento . Da mesma forma, os Ge pMOSFETs orientados (001) demonstram as características SS melhoradas em comparação com outras duas orientações, o que se deve ao fato de que os transistores na superfície (001) têm a densidade de intervalo médio inferior do estado de interface D it em comparação com os outros dispositivos. A Figura 4d mostra que os dispositivos em diferentes orientações têm diferentes V TH . Com base nos resultados da Fig. 4, conclui-se que, com o t fixo Si de 0,9 nm, os pMOSFETs Ge orientados para (001) obtêm as melhores características elétricas.

a Medido I DS - V GS e eu G - V GS curvas de (001) -, (011) -, e (111) -orientado Ge pMOSFETs com 0,9 nm t Si mostrando as excelentes características de transferência. b eu DS - V DS curvas medidas em V diferentes GS - V TH para os dispositivos

Comparação de a eu LIGADO , b eu vazamento , c SS e d V TH para (001) -, (011) -, e (111) - Ge pMOSFETs orientados com um t Si de 0,9 nm

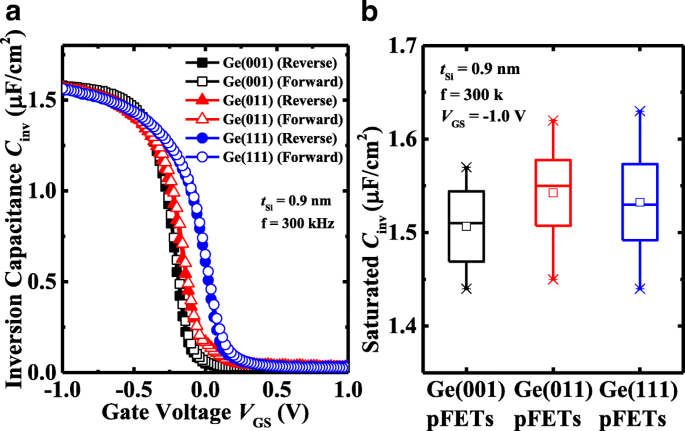

As espessuras de Si / SiO 2 IL em transistores com 0,9 nm t Si em diferentes orientações de superfície são estudados usando capacitância de inversão C inv versus V GS medição, como mostrado na Fig. 5. As medições de varredura para frente e reversa exibem uma histerese insignificantemente pequena nos dispositivos. Os transistores exibem magnitude semelhante a C inv , ~ 1,56 μF / cm 2 , correspondendo à espessura capacitiva efetiva (CET) de 2,2 nm. A Figura 5b mostra os resultados estatísticos de C saturados inv para os dispositivos, que demonstram a diferença muito pequena em C inv nos transistores em diferentes orientações de superfície. Isso indica que a taxa de passivação de Si amorfo por pulverização catódica de magnetron é independente da orientação da superfície. A regra dos deslocamentos da esquerda para a direita do C inv - V GS curvas é bem consistente com a de V TH para os dispositivos na Fig. 4d, que podem ser induzidos pela concentração de dopagem ligeiramente diferente em substratos de orientação diferente.

a Comparação de inversão C inv - V GS curvas entre os Ge pMOSFETs com 0,9 nm t Si em diferentes orientações. As varreduras para frente e para trás são mostradas. b Gráficos estatísticos para o saturado C inv dos dispositivos mostrando as diferenças insignificantes em C inv no regime de inversão

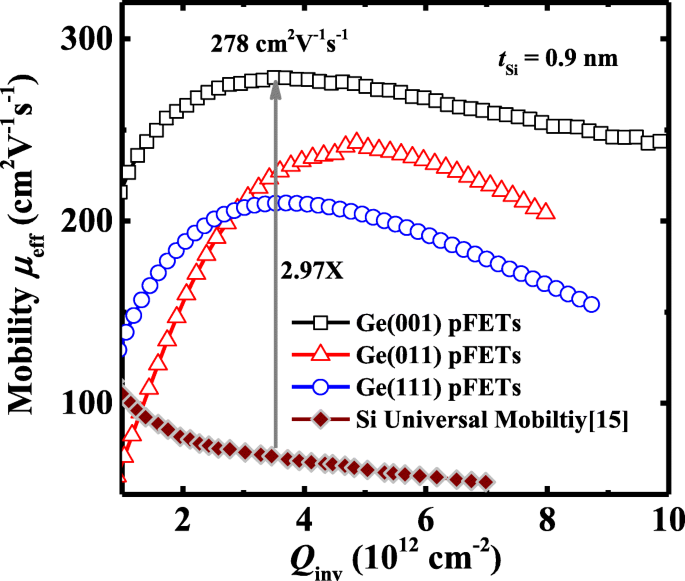

A Figura 6 compara as características de mobilidade dos transistores com 0,9 nm t Si em várias orientações de superfície. O μ eff foi extraído usando um método baseado em inclinação de resistência total [14]. Os pMOSFETs Ge (001) exibem uma mobilidade de canal muito maior em comparação com os dispositivos nas orientações (011) e (111). Transistores no substrato (001) atingem um pico μ eff de 278 cm 2 / V · s em uma densidade de carga de inversão Q inv de ~ 3,5 × 10 12 cm −2 , que é 2,97 vezes maior do que a mobilidade universal Si. Rugosidade da superfície na interface Si / Ge e densidade dos estados da interface ( D it ) pode afetar μ eff dos dispositivos em alta densidade de portadora de inversão. É improvável que as bolachas de Ge adquiridas comercialmente com várias orientações de superfície tenham a diferença óbvia na rugosidade da superfície. Portanto, é especulado que o aumento da mobilidade em dispositivos orientados para (001) é principalmente devido ao espalhamento de portadora reduzido contribuído pelos estados de interface. Neste trabalho, avaliamos o midgap D it dos dispositivos, e com o t fixo Si de 0,9 nm, os Ge pMOSFETs orientados para (001) realmente têm o midgap inferior D it em comparação com as outras orientações.

Parcela de μ eff versus Q inv para Ge pMOSFETs com 0,9 nm t Si em substratos orientados (001) -, (011) - e (111). Os pMOSFETs Ge (001) alcançam o aumento de 2,97 vezes em μ eff em um Q inv de 3,5 × 10 12 cm −2 em comparação com a mobilidade universal Si. O μ eff foi extraído usando um método baseado em inclinação de resistência total [17]

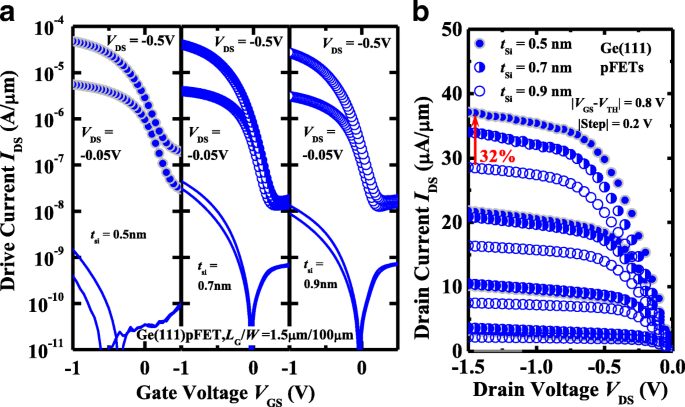

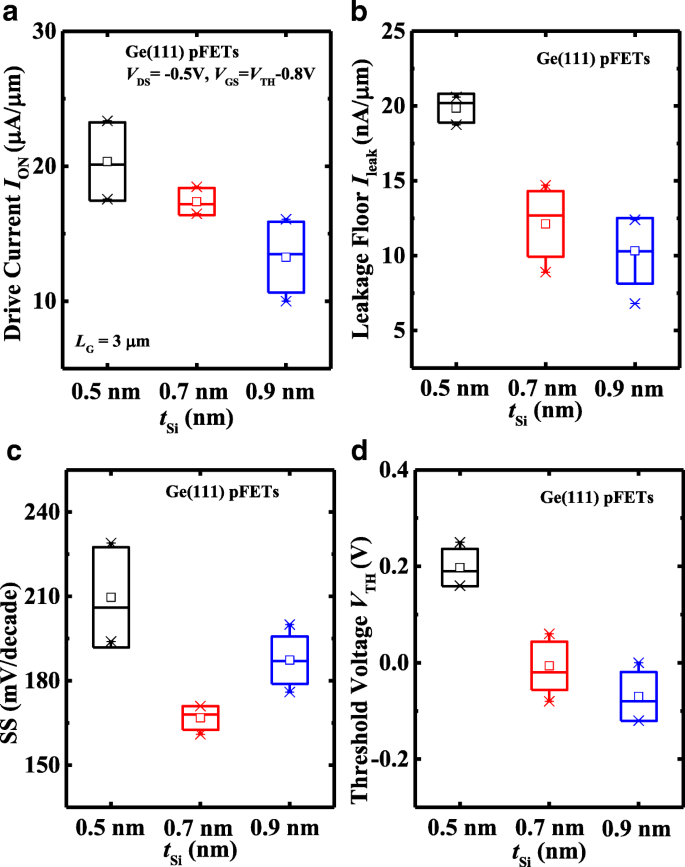

O impacto de t Si sobre o desempenho elétrico de Ge pMOSFETs também é investigado. A Figura 7a, b apresenta o I medido DS - V GS e eu DS - V DS curvas, respectivamente, dos Ge pMOSFETs orientados para (111) com t Si de 0,5, 0,7 e 0,9 nm em um V DS de - 0,05 e - 0,5 V. Os transistores têm um L G de 1,5 μm. Observa-se que Ge pMOSFETs com 0,9 nm t Si exibem características de transferência melhoradas em comparação com os dispositivos com mais fino t Si , mas eu LIGADO do dispositivo diminui com o aumento de t Si . Em V DS de - 1,5 V e V GS - V TH de - 0,8 V, Ge (111) pMOSFET com 0,5 nm t Si demonstra uma melhoria de 32% em I LIGADO em comparação com o dispositivo com 0,9 nm t Si . A Figura 8 representa os resultados estatísticos de I LIGADO , eu vazamento , SS e V TH dos Ge pMOSFETs em (111) -orientação com diferentes t Si . Na Fig. 8a, vemos que os transistores com 0,5 nm t Si alcançar o I melhorado LIGADO em comparação com os dispositivos com t mais espesso Si , que é devido ao transistor com 0,5 nm t Si que tem um CET menor, levando a um C mais alto inv . Percebe-se que eu vazamento diminui com o aumento de t Si (Fig. 8b), e transistores com 0,5 nm t Si tem as características SS inferiores às dos dispositivos com camada de passivação de Si amorfo de 0,7 e 0,9 nm (Fig. 8c). Isso pode ser devido aos transistores com 0,5 nm t Si tendo um midgap mais alto D it . A relação entre SS e midgap D it de Ge pMOSFET pode ser expresso por SS =ln (10) ⋅ ( kT / q) ⋅ [1 + ( C it + C d ) / C boi ], onde C boi , C d e C it são a capacitância de óxido, a capacitância da camada de depleção e a capacitância de armadilhas de interface, respectivamente. C it pode ser calculado por q × D it , foram D it é a densidade de interceptação da interface. Embora transistor com 0,5 nm t Si tem o maior C boi em comparação com os outros dois dispositivos, seu midgap superior D it pode levar ao SS inferior para os dispositivos com o t mais espesso Si . A passivação da superfície também afetará o I vazamento do dreno à fonte. Com a varredura de V GS da posição para o negativo, o canal é transferido do modo de acumulação para o modo de inversão. No entanto, se o D it é alto, alguns pontos na superfície do canal são fixados pelas armadilhas de interface e os caminhos de vazamento podem ser formados, aumentando I vazamento do dreno à fonte. Como mostrado na Fig. 8d, os pMOSFETs Ge (111) mostram o deslocamento de V TH para negativo V GS direção com o aumento de t Si , que é atribuído ao aumento da CET. Além disso, a densidade das armadilhas na metade inferior do bandgap parece aumentar para o mais fino t Si , o que pode levar à mudança de V TH [2].

a eu DS - V GS e eu G - V GS e b eu DS - V DS curvas de Ge (111) pMOSFETs com vários t Si . Transistor com 0,5 nm t Si exibe uma melhoria de 32% em I LIGADO em comparação com o dispositivo com 0,9 nm t Si em V DS de - 1,5 V e V GS - V TH de - 0,8 V

Comparação de a eu LIGADO , b eu vazamento , c SS e d V TH para Ge pMOSFETs orientados por (111) com 0,5, 0,7 e 0,9 nm t Si mostrando que transistores com 0,5 nm t Si tenho o melhor eu LIGADO , mas pior SS e eu vazamento características em comparação com dispositivos com t mais espesso Si

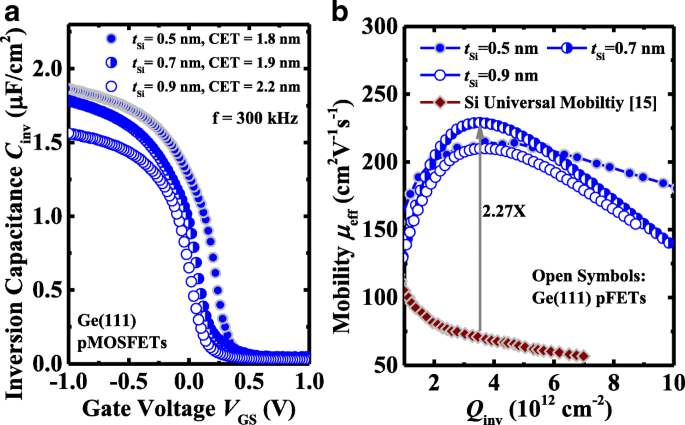

A Figura 9a mostra o C inv em função de V GS curvas para os Ge pMOSFETs na superfície orientada (111) com t Si de 0,5, 0,7 e 0,9 nm medidos a uma frequência de 300 kHz. Os valores CET nas regiões de inversão são extraídos em 1,8, 1,9 e 2,2 nm para os dispositivos com 0,5, 0,7 e 0,9 nm t si , respectivamente. μ eff como uma função de Q inv as características dos dispositivos são extraídas e mostradas na Fig. 9b. O Ge pMOSFET orientado (111) com 0,7 nm t si atinge o pico de mobilidade mais alto de 229 cm 2 / V s, que é 2,27 vezes maior em comparação com a mobilidade universal Si. Deve-se notar que os dispositivos com 0,5 nm t Si exibem um μ significativamente melhorado eff sobre os transistores com t mais espesso Si em alto Q inv (por exemplo, 10 13 cm −2 ) Isso também leva ao I superior LIGADO em alto V GS - V TH nos dispositivos com 0,5 nm t Si em comparação com os dispositivos com 0,7 e 0,9 nm t Si . O μ eff em alto Q inv diminui conforme t Si aumenta de 0,5 nm para 0,7 ~ 0,9 nm, o que é atribuído ao fato de que a maior rugosidade da superfície leva a um espalhamento mais forte da rugosidade da superfície dos portadores. Durante a passivação da superfície Ge usando a pulverização catódica de magnetron à temperatura ambiente, a difusão dos átomos da superfície é fortemente suprimida. Assim, com o aumento de t Si , a rugosidade da superfície é maior, o que pode ser observado nas imagens HRTEM da Fig. 2.

a C inv - V G características medidas a 300 kHz para dispositivos orientados a (111) com 0,5, 0,7 e 0,9 nm t Si . b μ eff como uma função de Q inv para Ge pMOSFETs [17]

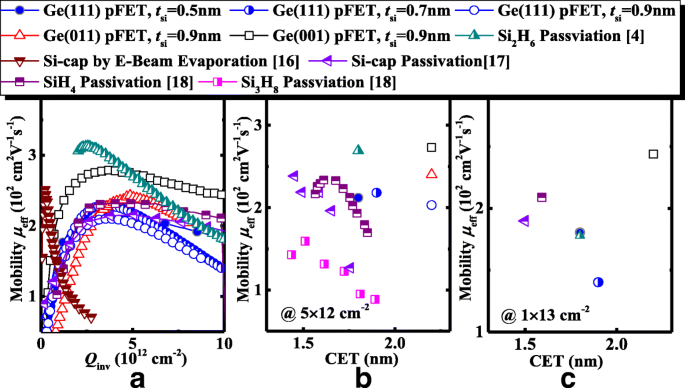

Na Fig. 10, comparamos o μ eff dos Ge pMOSFETs neste trabalho com aqueles dos transistores Ge relaxados relatados com Si por evaporação de feixe E, SiH 4 , Si 2 H 6, e Si 3 H 8 passivação. Em comparação com o Si amorfo por evaporação de feixe E na Ref. [15], Ge pMOSFETs neste trabalho exibem o μ significativamente melhorado eff . É visto que, no CET semelhante, Ge pMOSFETs utilizando a passivação de Si amorfo por pulverização catódica tem o menor μ eff em comparação com os dispositivos com Si 2 H 6 passivação. O processo de passivação usando Si amorfo precisa ser otimizado ainda mais para aumentar a mobilidade do portador.

a μ eff para os Ge pMOSFETs neste trabalho versus os resultados publicados para Ge pMOSFETs relaxados. b , c Comparativo de mercado de μ eff extraído em Q inv =5 × 10 12 e 1 × 10 13 cm −2 , respectivamente, dos Ge pMOSFETs com os diferentes valores CET [18, 19]

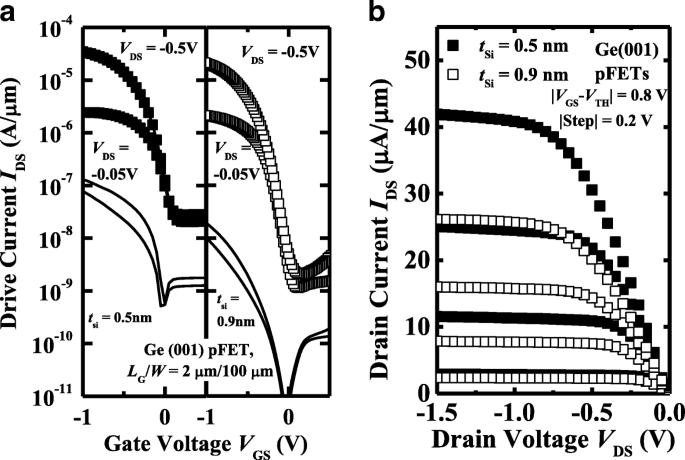

Ge pMOSFETs com os diferentes t Si na superfície orientada (001) também são caracterizadas. As Figuras 11a, b ilustram o I medido DS - V GS e eu DS - V DS curvas, respectivamente, de um par de Ge (001) pMOSFETs com 0,5 e 0,9 nm t Si . Semelhante aos dispositivos orientados para (111), Ge (001) pMOSFET com 0,5 nm t Si obtém a melhoria em I LIGADO mas a degradação em eu vazamento em comparação com o transistor com 0,9 nm t Si .

a Medido I DS - V GS e eu G - V GS curvas de pMOSFETs Ge orientados (001) com 0,5 e 0,9 nm t Si . b eu DS - V GS curvas dos dispositivos

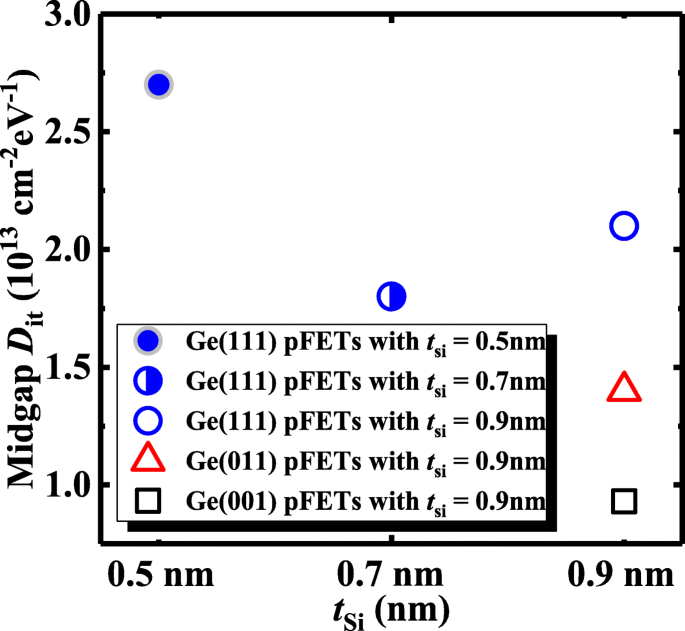

O midgap D it características de Ge pMOSFETs são estudadas pelo método em [16], e valores de D it são calculados por D it =[SSlog (e) / ( kT / q ) - 1] C G / q , [16] onde q é a carga do elétron, k é a constante de Boltzmann, T é a temperatura absoluta e C G é a capacitância medida da porta por unidade de área. A Figura 12 mostra D it em função da espessura do Si amorfo com várias orientações de superfície Ge. Para superfície orientada (111), um dispositivo com t de 0,7 nm si tem o menor D it valor. Com o t de 0,9 nm Si , Dispositivo orientado (001) tem o menor D it em comparação com os transistores em outras orientações.

D it versus a espessura do Si amorfo com várias orientações de superfície Ge

Finalmente, comparamos as principais características elétricas dos Ge pMOSFETs nas diferentes orientações na Tabela 1. Com um t fixo Si , Ge (001) pMOSFET tem o desempenho elétrico melhorado em comparação com as outras duas orientações. A corrente da unidade pode ser aumentada reduzindo o t Si de 0,9 nm a 0,5 nm, o que é devido a que o mais fino t Si fornece uma CET significativamente reduzida sem causar degradação em μ eff .

Conclusões

Os Ge pMOSFET passivados por Si amorfo são demonstrados nos substratos orientados (001) -, (011) - e (111). Com um t Si de 0,9 nm, o I melhorado LIGADO e as características SS são obtidas em pMOSFETs Ge orientados (001) em comparação com os dispositivos nas orientações (011) e (111), devido ao maior μ eff e midgap inferior D it . Ge (001) pMOSFETs com 0,9 nm t Si atingir um pico de mobilidade de 278 cm 2 / V s em um Q inv de 3,5 × 10 12 cm −2 , que é 2,97 vezes maior do que a mobilidade universal Si. É demonstrado que eu LIGADO dos dispositivos é melhorado com a diminuição de t Si devido à redução da TEC. Mas Ge pMOSFETs com t mais espesso Si exibem o balanço do sublimiar superior e o piso de vazamento, devido ao intervalo médio D it pode ser reduzido aumentando t Si .

Abreviações

- ALD:

-

Deposição de camada atômica

- BF 2 + :

-

Íon fluoreto de boro

- CET:

-

Espessura capacitiva efetiva

- Ge:

-

Germânio

- GeO x :

-

Óxido de germânio

- HF:

-

Acido hidrosulfurico

- HfO 2 :

-

Dióxido de háfnio

- HRTEM:

-

Microscópio eletrônico de transmissão de alta resolução

- IL:

-

Camada interfacial

- MOSFETs:

-

Transistores de efeito de campo semicondutores de óxido metálico

- Ni:

-

Níquel

- Si:

-

Silício

- SS:

-

Balanço de sublimiar

- TaN:

-

Nitreto de tântalo

- TDMAHf:

-

Tetraquis (dimetilamido) háfnio

Nanomateriais

- KUHMUTE redesenha mobilidade com impressão 3D SLS

- Impressão 3D de alta velocidade com AFPM

- Impressão 3D de alta velocidade com AION500MK3

- Alto desempenho de PEDOT:Células solares PSS / n-Si baseadas em superfície texturizada com eletrodos AgNWs

- Conversor de polarização com birrefringência controlável baseado em metassuperfície híbrida totalmente dielétrica-grafeno

- Célula solar híbrida de silício orgânico nanoestruturado de alto desempenho com estrutura de superfície modificada

- Uma referência de voltagem sem resistor de baixa potência em nanoescala com alto PSRR

- Nanofolhas porosas de ZnO com modificação de superfície parcial para separação de cargas aprimorada e alta atividade fotocatalítica sob irradiação solar

- Ge pMOSFETs com passivação GeOx formada por ozônio e pós-oxidação de plasma

- Novos insights sobre fatores que limitam o transporte da transportadora em filmes in2O3 muito finos e amorfos com dopagem de Sn-dopado com alta mobilidade de salão