Detector de ampla faixa de efeito de carregamento induzido por plasma para processos CMOS BEOL avançados

Resumo

Este trabalho propôs um detector de carga induzida por plasma modificado (PID) para ampliar a faixa de detecção, para monitorar o possível dano do plasma através de um wafer durante processos avançados de CMOS BEOL. Novos projetos de antenas para padrões de danos induzidos por plasma com capacitores estendidos são investigados. Adaptando os novos detectores PID, os níveis máximos de carga dos detectores foram aprimorados.

Introdução

Nos últimos anos, a evolução da tecnologia de processo de semicondutor continua a reduzir a dimensão crítica em circuitos integrados de grande escala [1,2,3]. Os processos lógicos FinFET avançados tornaram-se mais complexos para a realização de transistores compactados em chips de Si multifuncionais e mais poderosos. Etapas de ataque de íon reativo aprimoradas por plasma [4, 5] tornam-se inevitáveis em processos de nanoescala avançados para alcançar estruturas de alta razão de aspecto que são essenciais para circuitos de alta densidade de empacotamento [6]. Para nós de tecnologia CMOS além de 45 nm, as portas do transistor mudaram da porta de poli-silício convencional com dióxido de silício para pilhas de portas de metal high-k [7, 8]. Essa mudança torna os dispositivos mais suscetíveis aos danos induzidos pelo plasma e pode levar a danos latentes imprevistos às camadas dielétricas de alto k. [9]. Nos processos de fabricação de FinFETs de última geração, várias etapas de plasma de RF, como corrosão, deposição e processos de limpeza, são inevitáveis, o que cria frequências mais altas de eventos de carga induzida por plasma [10]. Podem ocorrer cargas positivas e negativas em estruturas metálicas. À medida que essas cargas fluem através dos caminhos condutores feitos de linhas de metal pré-existentes, via e contatos, a descarga indesejável através de partes vulneráveis dos circuitos, particularmente através do dielétrico da porta do transistor, pode levar a preocupações significativas de confiabilidade. Por exemplo, na etapa de corrosão a seco, íons de choque e materiais pulverizados na superfície de reação causam mais defeitos nas aletas em massa [11, 12]. Para evitar que o evento de carregamento de plasma leve a danos irreversíveis aos circuitos, são fornecidas regras de projeto que limitam o tamanho das estruturas metálicas. Outro exemplo de alívio do PID inclui o uso de diodos de proteção, que poderiam desviar a corrente de carga do plasma de circuitos sensíveis [13]. A introdução do óxido de porta In-Situ Steam Generation (ISSG) relatou uma melhora em sua tolerância a danos de plasma [14]. Além disso, o corte da câmara e a modificação do processo de deposição do PECVD-Ti também aliviaram o dano induzido pelo plasma [15]. A maioria desses métodos, entretanto, resulta em limitações indesejáveis na flexibilidade do projeto do circuito ou nas compensações de processamento.

Convencionalmente, os padrões de teste on-wafer têm sido usados para monitorar os níveis de dano induzido por plasma (PID) [16]. O parâmetro mais comum e amplamente usado para monitorar PID no wafer são as características de tempo de quebra (TDDB) das portas do transistor com grandes estruturas de antena. O dano latente nos dielétricos da porta pode ser revelado medindo a degradação da camada dielétrica da porta sob tensão ou testes de estresse de corrente. Conseqüentemente, esses padrões não são capazes de fornecer feedback em tempo real sobre os processos de plasma [17]. Em nossos trabalhos anteriores, um detector de efeito de carga induzido por plasma em wafer é demonstrado em tecnologias FinFET avançadas. O detector PID usa estrutura de acoplamento capacitivo para induzir uma resposta na porta flutuante [18,19,20]. Portanto, não há dano à camada dielétrica da porta, como ocorre em um detector PID convencional. Nesses novos detectores, mede-se as curvas I – V de deslocamento para descobrir a intensidade, a duração e também a polaridade das cargas na porta da antena. Verificou-se que esses detectores podem estar sujeitos ao efeito de saturação à medida que a intensidade do plasma em certos locais de registro excede os níveis críticos. Para estender a faixa dinâmica do detector PID, novos projetos de porta de antena foram investigados neste trabalho, onde a ampliação das faixas de detecção é demonstrada com sucesso.

Métodos

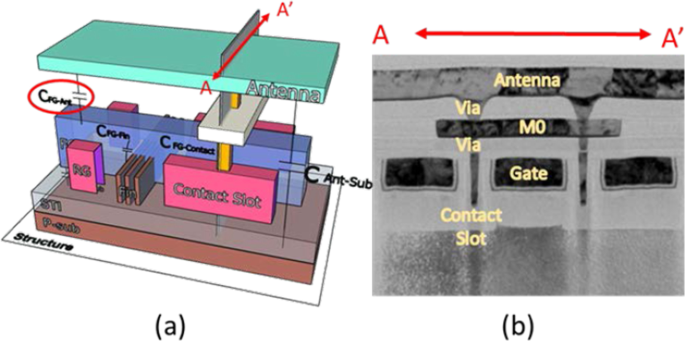

O esquema 3D do detector de dano induzido por plasma (PID) com um capacitor parasita conectado ao nó da antena é mostrado na Fig. 1a. Diferente da estrutura de monitoramento PID, este detector utiliza um longo slot de contato para acoplar a tensão da antena na porta flutuante. A fotografia TEM em corte transversal é mostrada na Fig. 1b. Conforme mostrado na figura, as ranhuras de contato que coletam cargas são capacitivamente acopladas à porta flutuante.

a As ilustrações 3D do detector PID in-situ relatado anteriormente e o capacitor da antena são destaque nesta estrutura. b A foto TEM do detector PID, onde o comprimento da porta deste detector é de 140 nm

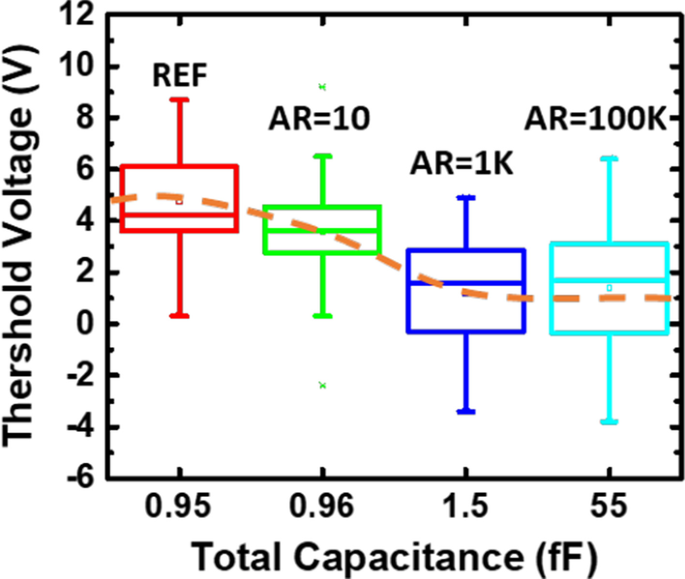

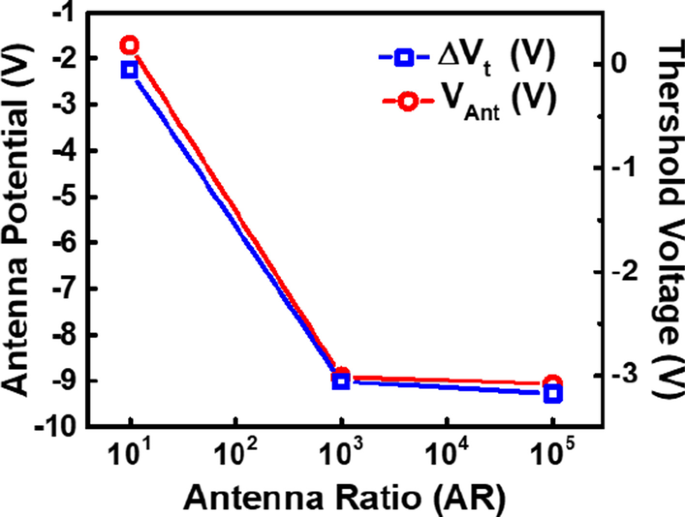

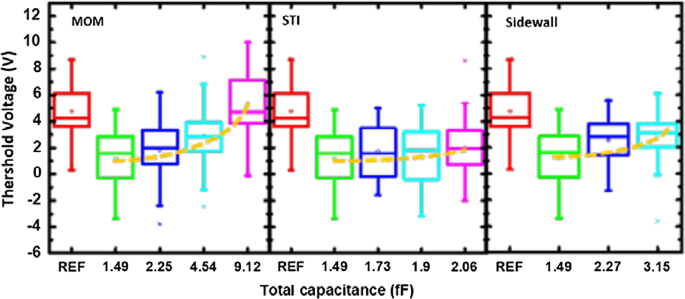

A Figura 2 compara as distribuições de tensão de limiar registradas desses detectores em um wafer de 12 polegadas. A mudança de voltagem de limite negativo indica que cargas negativas foram coletadas na antena, atraindo cargas positivas para a porta flutuante, resultando em mudanças de voltagem de limite negativo. Verificou-se que conforme a área da antena aumenta, o aumento da capacitância total leva à diminuição das tensões gerais da antena, portanto, menor o deslocamento em V t .

Faixa de tensão limite de amostras com diferentes tamanhos de antena e a capacitância total correspondente na antena

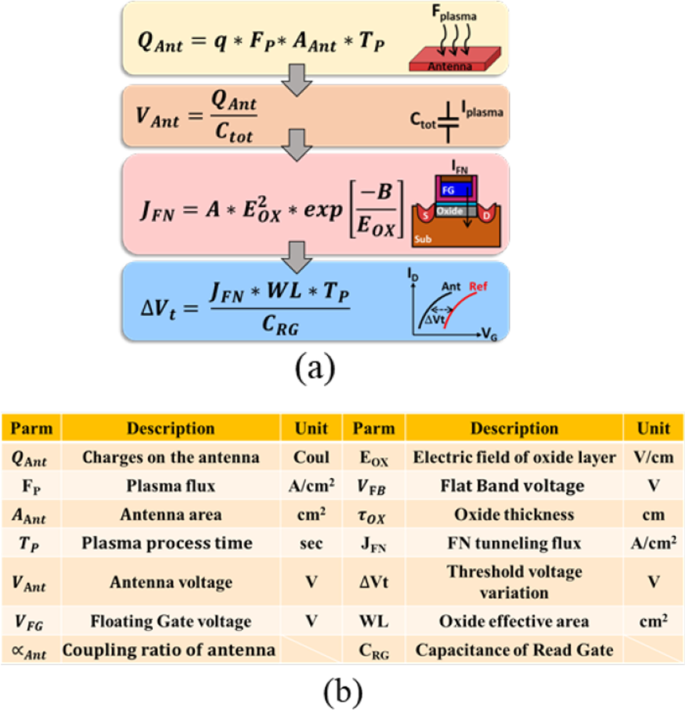

Aqui, na Fig. 3a, o fluxograma que explica os princípios básicos de operação do detector PID é delineado. Como a carga do plasma ( Q Formiga ) são coletados na antena, o potencial da porta da antena, V Formiga , varia. V Formiga é então acoplado à porta flutuante (FG), promovendo o tunelamento de elétrons para dentro ou para fora de FG. Após os processos de plasma, V t desses detectores podem se tornar mais negativos ou mais positivos com base na polaridade de Q Formiga . V t pode ser calculado pelo modelo de corrente de tunelamento FN com o parâmetro listado na Fig. 3b.

a O fluxograma das cargas de plasma ( Q Formiga ) coletado na antena para deslocar V t . Com base no modelo de tunelamento FN, Δ V t pode ser calculado. b A lista de parâmetros com suas definições

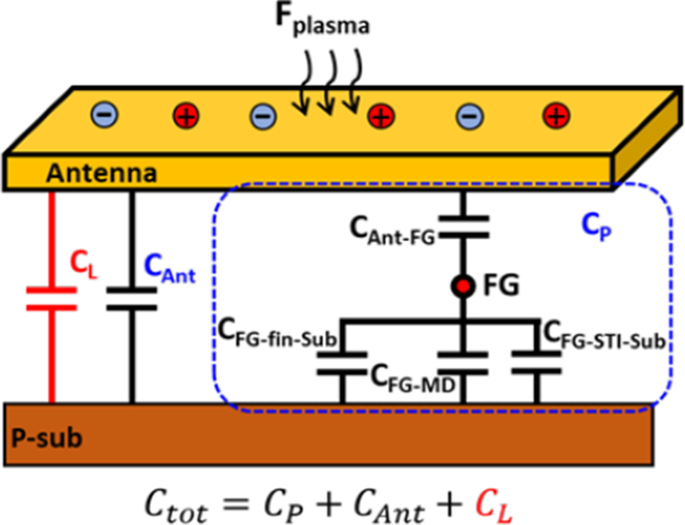

A Figura 4 ilustra todas as capacitâncias possíveis no detector PID baseado em FG. Da Fig. 5, verifica-se que à medida que a área da antena aumenta, Δ V t tende a saturar. Como V Formiga atinge os níveis máximos, Q Formiga começa a vazar quando o nível de tensão está muito alto. Para evitar que o nível de fluxo de plasma exceda a limitação do detector, a capacitância da antena é deliberadamente aumentada pela adição de capacitores de carga que podem reduzir a proporção da capacitância da antena na capacitância total.

Composição da capacitância na estrutura da antena com o capacitor de carga adicional, que é projetado para modificar a sensibilidade dos detectores PID. Onde C P é a capacitância parasita geral na porta flutuante

Tanto o nível de tensão limite quanto o nível de tensão da antena projetada saturam os padrões com área de antena aumentada

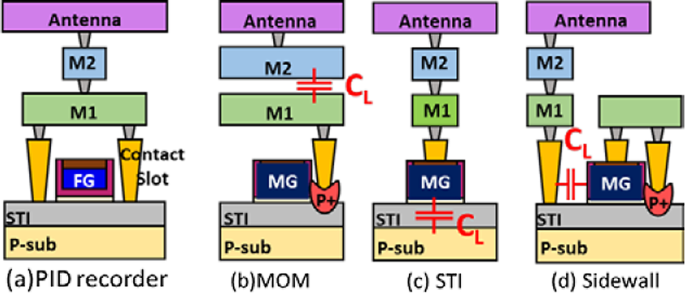

A Figura 6a mostra a estrutura 2D do detector PID in-situ relatado anteriormente, e três estruturas de realização de capacitores adicionais são apresentadas. Eles são capacitores MOM, que usam a maior área de sobreposição de camadas de metal para aumentar a capacitância total na Fig. 6b, capacitores STI, que aumentam a capacitância ajustando o comprimento da porta de metal na Fig. 6c, e capacitores de parede lateral, que usam a área de sobreposição da porta de metal e contato para formar o capacitor adicional Fig. 6d.

Ilustração em corte transversal de a o detector PID in-situ, e aqueles com um capacitor adicional de carga realizado por b MOM, c STI e d parede lateral, respectivamente

Resultados experimentais e discussão

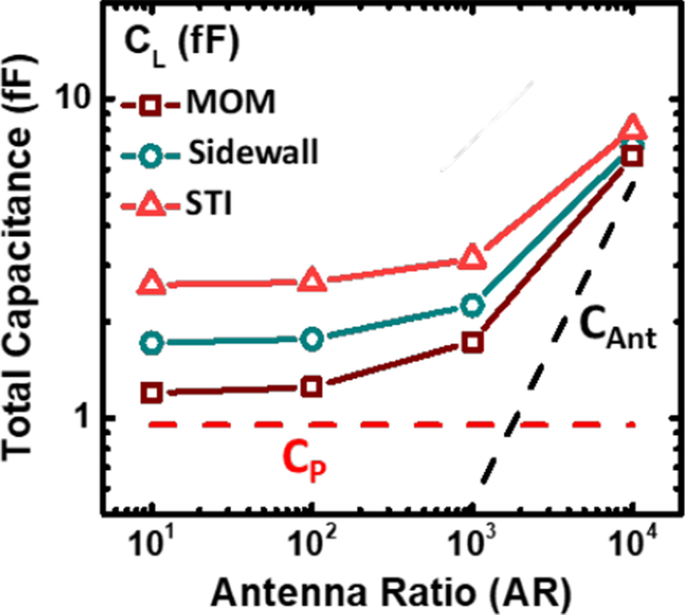

A Figura 7 compara as relações de capacitância total versus antena quando diferentes tipos de capacitores de carga são adicionados. A capacitância total é dominada pela capacitância da antena quando a proporção da antena é maior que 1 K.

Comparação da capacitância total versus as relações da antena à medida que os três tipos de capacitores de carga são adicionados

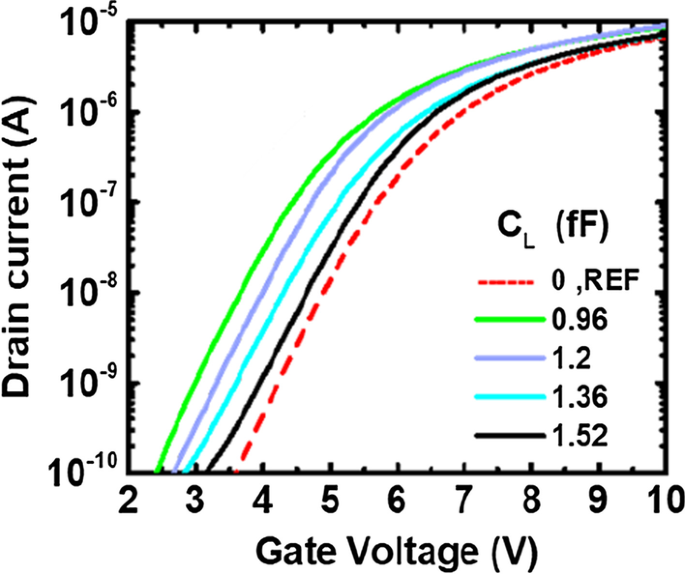

Quando a capacitância de carga adicionada torna-se comparável à capacitância da antena, a capacitância total pode então ser afetada pelos capacitores de carga. Já que a quantidade máxima de cargas cobradas pela antena é fixa; aumentando a capacitância total, Δ V é esperada diminuição, de acordo com Δ Q = C Δ V . Assim, a sensibilidade da faixa de detecção poderia ser suprimida, evitando o efeito de saturação quando o nível de carga do plasma ultrapassar seus limites originais. As características da corrente de drenagem para dispositivos de AR =10 com diferentes capacitores STI são comparadas na Fig. 8. Quando um capacitor de carga maior é adicionado, a porcentagem da capacitância da antena na capacitância total é reduzida. Sob o mesmo fluxo de carga de plasma, as cargas totais de plasma após um período são proporcionais à área da antena. Portanto, quando a capacitância geral aumenta, V Formiga deverá ser reduzido, permitindo a detecção de altos níveis de fluxo de plasma. Conforme mostrado na Fig. 8, deslocamentos menores são encontrados nas curvas I – V para as amostras com capacitores de carga adicionais.

Curva I – V de tamanhos diferentes de capacitor STI com AR =10. Quando a capacitância externa é maior, a curva I – V está mais próxima daquela das células de referência

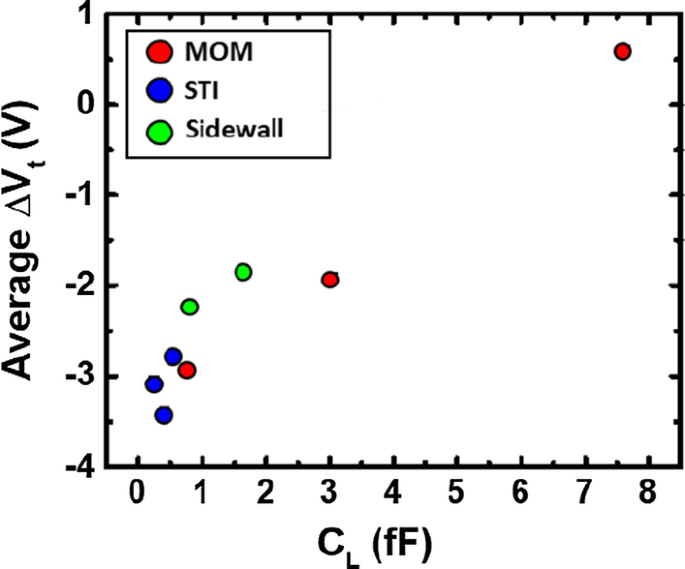

Os gráficos de caixa das tensões de limiar medidas a partir de amostras com AR =1 K e diferentes tamanhos de capacitores MOM, STI e Sidewall são comparados na Fig. 9 Quando a capacitância de carga é aumentada, menos mudança de tensão de limiar é observada em média. No projeto experimental, C L pela estrutura de STI é muito pequena para mostrar o impacto do nível de carregamento. A comparação na Fig. 10 sugeriu que três maneiras de adicionar capacitores de carga também podem reduzir efetivamente a resposta média à carga de plasma. O capacitor de carga adicional pode expandir com sucesso a faixa de detecção do detector PID, enquanto a sensibilidade dos detectores é reduzida. Para alcançar uma ampla faixa de detecção de nível de carga de plasma, uma série de detectores PID com diferentes níveis de C L pode ser projetado em uma matriz 1-D para detectar níveis de carga de plasma na extremidade superior e inferior.

As tensões limite medidas em amostras com diferentes tamanhos de capacitores MOM, STI e Sidewall são comparadas. Todos os dispositivos têm o mesmo AR de 1 K

Comparação da média Δ V t versus C L implementado pelos três tipos de estruturas de capacitores, onde Δ V t é definido como o V t diferença entre uma célula detectora e a célula de referência. Os dados sugerem que a sensibilidade reduzida pode ser obtida como C L aumentou

Conclusões

Este estudo investiga um novo projeto de porta de antena para estender a faixa de detecção de níveis de carga induzida por plasma nos detectores de monitoramento PID. Ao adicionar um capacitor de carga, a alta tensão da porta da antena sujeita a vazamento de carga pode ser evitada, permitindo que um nível mais alto de nível de carga seja registrado nos detectores PID. Este novo design amplia efetivamente a faixa de detecção de níveis de carga de plasma em processos CMOS BEOL avançados.

Disponibilidade de dados e material

Não aplicável.

Abreviações

- PID:

-

Dano induzido pelo plasma

- V t :

-

Tensão de limiar

- Q Formiga :

-

Cargas na antena

- V Formiga :

-

Voltagem da antena

- MOM:

-

Metal-óxido-metal

- AR:

-

Proporção da antena

- C L :

-

Capacitância de carga

- C P :

-

Capacitância parasita

- C Formiga :

-

Capacitância da antena

Nanomateriais

- Circuito de porta CMOS

- Python para loop

- Pesquisadores da IBM levam para casa o prêmio de inovação para pesquisa de semicondutores

- Tecnologias de Deposição de Camada Atômica Avançada para Micro-LEDs e VCSELs

- Bioflavonóide direcionado ao receptor de folato Nanopartículas de quitosana carregadas com genisteína para efeito anticâncer avançado em cânceres cervicais

- O efeito do plasma sem equilíbrio de contato nas propriedades estruturais e magnéticas de Mn Х Fe3 - X О4 Spinels

- Gravador de divisão de carga in situ (CSIR) para exame em tempo real do efeito de carregamento de plasma em processos FinFET BEOL

- Efeito de campo ferroelétrico Efeito de comutação assimétrica resistiva induzida em BaTiO3 / Nb:SrTiO3 Heterojunções epitaxiais

- Síntese e investigação de nanofios de CuGeO3 como materiais de ânodo para baterias de íon de sódio avançadas

- Projeto de padrão de teste para dano induzido por plasma em dielétrico intermetal em processos FinFET Cu BEOL