Efeitos das variações de gravação na formação do canal Ge / Si e desempenho do dispositivo

Resumo

Durante a formação de estruturas Ge fin em um substrato de silício sobre isolante (SOI), descobrimos que o processo de corrosão seca deve ser cuidadosamente controlado. Caso contrário, isso pode levar a sobredimensionamento de Ge ou a formação de um perfil indesejável de aleta de Ge. Se o processo de corrosão não for bem controlado, a estrutura Ge / SOI superior é removida e apenas a camada de barbatana de Si permanece. Nesse caso, o dispositivo apresenta características anormais. O processo de gravação está emergindo como uma etapa crítica no dimensionamento e embalagem do dispositivo e afeta as tentativas de aumentar a densidade da embalagem e melhorar o desempenho do dispositivo. Portanto, sugere-se que a otimização da operação do reator de plasma seja realizada por meio de simulações, a fim de não só ajustar os parâmetros do processo utilizados, mas também modificar o hardware empregado. Vamos desenvolver dispositivos sem junção Ge, empregando parâmetros de fabricação atualizados. Além disso, queremos eliminar os deslocamentos desajustados na interface ou reduzir os deslocamentos de rosqueamento aplicando o processo de recozimento térmico cíclico para atender ao objetivo de obter estrutura suspensa de camadas epitaxiais de Ge com alta qualidade.

Histórico

Uma maneira de aumentar a velocidade de resposta de dispositivos semicondutores e reduzir seu consumo de energia é usar um semicondutor com alta mobilidade de portadora. Exemplos de tais materiais incluem Ge, bem como suas ligas e compostos. No entanto, quando uma estrutura é formada pelo empilhamento de uma camada de um material semicondutor no topo de um substrato de um semicondutor diferente, podem surgir problemas. Por exemplo, a diferença nos tamanhos de rede do substrato semicondutor e a camada sobreposta de um material semicondutor diferente pode causar deslocamentos, o que pode ter um efeito adverso no desempenho do dispositivo. Convencionalmente, a fim de fabricar dispositivos semicondutores à base de Ge que incluem um substrato de Si, uma camada tampão mais espessa ou camada sacrificial (por exemplo, uma camada tampão de Si / Ge) é formada no substrato de silício. Posteriormente, uma camada epitaxial de Ge é cultivada na camada tampão de Si / Ge. Em seguida, os processos de corrosão anisotrópica e isotrópica são realizados sequencialmente para remover uma parte da camada tampão e reter a camada epitaxial de Ge. Os dispositivos VLSI devem mostrar uma alta corrente de unidade, baixa corrente de fuga em estado desligado e baixa tensão de alimentação, a fim de garantir alto desempenho, incluindo baixo consumo de energia em espera e dissipação de energia dinâmica reduzida. Atualmente, a mobilidade aumentada de tensão, high-k / metal gate e arquitetura de dispositivo tridimensional (3D) no nó de 22 nm [1] são algumas das tecnologias sendo usadas para o escalonamento contínuo de metal-óxido-semicondutor complementar ( CMOS) dispositivos com um canal Si. Além de características como alta mobilidade, novas arquiteturas de dispositivo como as de gate-all-around (GAA) [2] e transistores de efeito de campo ultrafinos (FETs) [3] são necessárias para melhorar o controle eletrostático no sub Nós -10 nm. Foram demonstrados pFETs GAA [4] e nFETs [5] baseados em Ge com operação em modo de inversão (INV). No entanto, a formação de junções em dispositivos Ge INV é uma questão crítica devido à baixa solubilidade de dopante, rápida difusão de dopante e baixo orçamento térmico. Para resolver esses problemas, dispositivos sem junção (JL) [6] que usam um canal dopado pesado com o mesmo tipo de portadora das regiões de fonte / dreno (S / D) têm sido sugeridos como alternativas. No entanto, o rápido dimensionamento dos transistores requer o desenvolvimento de dispositivos novos e mais eficazes que possam alcançar os transistores modernos. Nos últimos anos, os JL-FETs têm se mostrado promissores como transistores de próxima geração. O JL-FET é basicamente um resistor no qual a densidade da portadora móvel pode ser controlada pela porta. No estado LIGADO, existe uma grande corrente de corpo, devido à concentração de dopagem relativamente alta na região do canal; a corrente de acumulação de superfície é adicionada a esta corrente. O nível de dopagem no JL-FET precisa ser alto a fim de alcançar uma unidade de corrente adequada, enquanto a seção transversal do dispositivo precisa ser pequena o suficiente para que o dispositivo possa ser desligado . No entanto, no caso de JL-FETs altamente dopados, os portadores sofrem um espalhamento significativo de impurezas, devido ao qual a corrente de transmissão é significativamente degradada [7]. Além disso, os JL-FETs têm as vantagens de serem simples de fabricar e ter alta mobilidade de carga e baixa capacitância de porta, em contraste com dispositivos INV [8,9,10,11,12]. Recentemente, pMOSFETs de porta dupla [13] e porta tripla [14] Ge JL-FET foram demonstrados em substratos isolantes de germânio e Si em massa, respectivamente.

Como os dispositivos microeletrônicos continuam a encolher e os requisitos de processo se tornam cada vez mais rigorosos, a modelagem e simulação de plasma se tornam cada vez mais atraentes como uma ferramenta para projeto, controle e otimização de reatores de plasma [15]. Diversas técnicas são usadas para simular o comportamento dos processos de plasma com base na disparidade em escalas de comprimento e tempo. Uma das técnicas de simulação, dinâmica de fluidos computacional (CFD), é amplamente usada para prever os campos de fluxo para recursos de projeto de engenharia e para extrapolar as limitações experimentais. Sua modelagem tem sido aplicada para investigar o fenômeno de mistura em fluxo [16], mas raro estudo em processo de corrosão. Portanto, este estudo se propôs a caracterizar em detalhes o campo de fluxo térmico de reatores de plasma para o processo de corrosão, e então deduzir parâmetros numéricos que podem ser benéficos aos experimentos.

Neste trabalho, o ataque químico foi realizado para formar camadas epitaxiais de Ge suspensas sobre Si, bem como outros semicondutores de liga para integração de dispositivos. Os resultados simulados serão validados por experimentos; portanto, as condições iniciais e de contorno, bem como os parâmetros no modelo numérico, serão modificados para aumentar a confiabilidade dos dados. Antecipamos que os parâmetros ideais podem ser obtidos por experimentos e simulações para melhorar as técnicas de corrosão e cumprir esse desenvolvimento de transistor realizando um processo de fabricação de maior qualidade, bem como um custo de produção mais baixo.

Métodos / Experimental

Os substratos iniciais foram wafers SOI com uma camada superior de silício de 70 nm (tipo p, 9–18 Ω cm). Os wafers foram limpos usando os processos RCA standard clean 1 (SC-1) e RCA standard clean 2 (SC-2), a fim de remover quaisquer compostos orgânicos, metais indesejados e partículas presentes. Isso foi seguido por enxágue em água desionizada e secagem em N 2 . O filme Ge foi depositado em um reator epitaxial de deposição de vapor químico de baixa pressão (Epsilon 2000, ASM) usando 10% GeH 4 como o precursor. O hidrogênio foi usado como gás de arraste. Antes da deposição do filme de Ge, um pré-tratamento à base de HCl in situ foi realizado a 850 ° C e 10 Torr para preparar a superfície do wafer. A temperatura do substrato foi então alterada para 400 ° C para crescer um filme Ge no wafer SOI usando 10% GeH 4 . As espessuras dos filmes de Ge depositados foram determinadas usando microscopia eletrônica de transmissão (TEM, emissão térmica tipo Schottky, 0,5–200 kV). As cristalinidades dos filmes de Ge foram examinadas usando análise de difração de raios-X (XRD) (D8A, Bruker, radiação CuKα, λ =1,5408 Å, 20-70 °). Além disso, varreduras Ω – 2θ foram realizadas em torno do pico de difração (004) usando um sistema X’Pert MRD (PANalytical). Um colimador de cristal cortado em canal Ge {400} duplo foi usado para selecionar a radiação CuKα1. Durante as medições de XRD padrão, a amostra foi fixada em uma posição horizontal, e a fonte e o braço detector do difratômetro foram movidos no modo θ – θ. O mapeamento do espaço recíproco foi realizado no modo de resolução média usando o colimador de cristal acima mencionado; Fendas de 0,4 mm de largura estavam presentes no braço do detector na frente do contador de cintilação. As espessuras das camadas de Ge foram determinadas por meio de medições de elipsometria (M2000, J. A. Woollam Co., λ =193–1690 nm). A barbatana foi formada por ataque de plasma anisotrópico usando Cl 2 / HBr gas. Após a formação do ZrO 2 / TiN gate, o S / D foi implantado com B (1 × 10 15 cm −2 , 15 keV) e ativado por recozimento térmico rápido a 550 ° C por 30 s.

Gravura a seco altamente seletiva do mecanismo de germânio

As reações de elétrons e neutras são isotrópicas, enquanto as reações de íons são altamente direcionais e variam com a polarização aplicada. Ajustando a potência de polarização, os íons podem ser acelerados ao longo da direção desejada para auxiliar na reação de corrosão. É geralmente aceito que o Br não reage espontaneamente com o Si e que os íons energéticos são necessários para que a reação ocorra. Os átomos de Br e Cl assistidos por íons podem reagir com átomos de Ge ou Si espontaneamente sob ativação para formar os produtos voláteis GeBr 4 , GeCl 4 , SiBr 4 e SiCl 4 , que são dessorvidos da superfície do substrato e podem ser bombeados para fora. Esta reação química assistida por íons de Si com Br mostrou ser altamente anisotrópica. Taxas de corrosão vertical mais altas foram obtidas usando HBr para variações de poder de polarização, o que confirma que a adição de HBr em Cl 2 pode aumentar a taxa de corrosão [17]. Uma vez que plasma baseado em Cl e Br etch Ge e Si por um mecanismo assistido por íons, a energia de íons como Br + , Br 2+ , HBr + , Cl + e Cl2 + pode ser controlado enviesando o suporte de substrato. Não há nenhuma mudança pronunciada na taxa de corrosão lateral, variando o poder de polarização para a corrosão na superfície superior e na área de estreitamento. Rebaixos foram encontrados nas estruturas de aletas atacadas com misturas de HBr, na área de estrangulamento, uma vez que o ataque lateral foi potencializado pelos defeitos ao longo da interface Ge / Si. E também a máscara influencia potencialmente a evolução da forma devido ao impacto da parede lateral do fluxo de íons. Este fenômeno é amplificado conforme o perfil se torna mais profundo e conforme o componente de velocidade lateral do íon aumenta. Por causa da alta dependência angular do processo de corrosão HBr-plasma [18], assim, pode-se concluir que a estrutura do cristal é relativamente mais fraca na interface Ge / Si por causa dos átomos parcialmente ligados dos deslocamentos desajustados e os relativamente fracos Ligações Ge-Ge e Ge-Si. Ajustando a proporção de HBr / Cl 2 e poder de polarização, diferentes tipos de estruturas semelhantes a aletas podem ser obtidos durante a fabricação do dispositivo Ge. As propriedades de gravação de Ge e Si são muito semelhantes. Os gases que gravam o Si geralmente gravam o Ge a uma taxa maior. Foi demonstrado que as forças das ligações Ge e Si são Ge-Ge =263,6 ± 7,1 kJ mol −1 e Si-Si =325 ± 7 kJ mol −1 [2]. Diferentes poderes de polarização foram aplicados para ajustar a taxa de corrosão vertical por aceleração direcional dos íons. As imagens foram gravadas após o processo de empilhamento de portas. A taxa de corrosão vertical foi calculada a partir da altura do filme em relação ao substrato de óxido. As taxas de corrosão lateral foram determinadas a partir de duas partes da barbatana:a corrosão lateral na superfície superior da nadadeira e a corrosão na área de estrangulamento perto da interface Ge / Si. Em resumo, o poder de polarização foi experimentalmente considerado o parâmetro mais crítico no processo de corrosão e, portanto, em afetar as características do dispositivo de acordo.

Neste estudo, todos os processos de corrosão foram realizados em um reator TCP 9600 da Lam Research. Este é um reator de plasma acoplado a transformador que permite o controle separado da energia da bobina (eletrodo superior) e da polarização do substrato (eletrodo inferior). O resfriamento do lado posterior do hélio foi incorporado para permitir que a temperatura do substrato seja controlada de forma mais eficaz. As amostras foram montadas em um painel de 6 pol. Wafer portador de Si com graxa para vácuo antes de ser introduzido na câmara de corrosão. HBr / Cl 2 a química foi explorada para o processo de corrosão anisotrópica. A pressão do processo foi controlada a 10 mTorr. A configuração experimental detalhada e as condições são ilustradas no estudo de Hsu et al. [4].

Modelo Físico

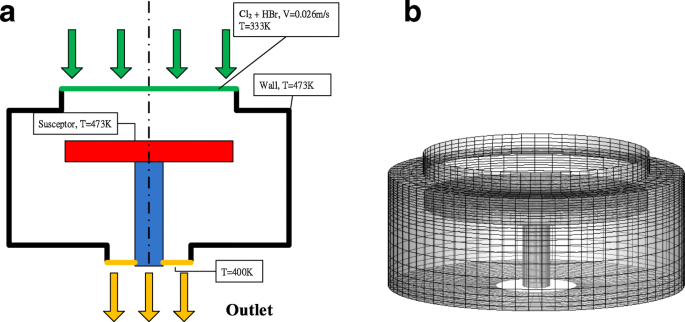

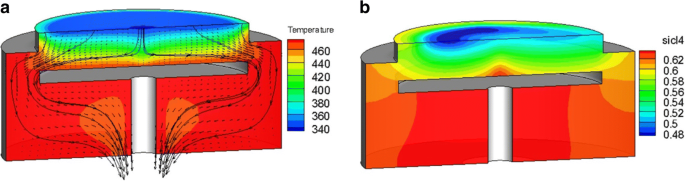

CFD é usado para acessar as informações internas dentro do reator e o fluxo é considerado laminar com a condição de limite de deslizamento devido ao maior número de Knudsen na câmara (Fig. 1). Na presente simulação, o fluxo térmico do plasma é considerado uma mistura nas equações de momentum; o transporte de partículas é considerado nas equações que regem as espécies e as reações químicas estão envolvidas na parede do suscetor. Um caso modelo para simulação é ilustrado na Fig. 3. O gás de entrada é uma mistura de cloro (Cl 2 ) e brometo de hidrogênio (HBR). A velocidade da mistura na entrada é de 0,026 m / s com temperatura mantida em 333 K. O susceptor e a parede da câmara são aquecidos à temperatura de operação 473 K. Este fluxo de plasma conduzido por polarização de potencial elétrico e tem reações químicas na superfície do susceptor em um uniforme, repetível e, finalmente, para ser descarregado do reator. Após construir a modelagem sólida pelo software CAD, o sistema de malha foi construído em grades estruturadas com 50.000 nós, conforme mostrado na Fig. 3. A equação de conservação transitória para o transporte de uma quantidade escalar ϕ é demonstrada pela seguinte equação escrita em integral forma para um volume de controle arbitrário V da seguinte forma [19]:

Modelo físico para simulação numérica de reator de plasma. a O esboço da câmara do reator com as condições de contorno prescritas. b Sistema de malha para simulações numéricas

$$ \ frac {d} {dt} \ underset {V} {\ oint} \ rho \ varphi \; dV + \ oint \ kern0.27em \ rho \ varphi \ overset {\ rightharpoonup} {v} \ cdot \ mathrm { d} \ overrightarrow {\ mathrm {A}} =\ oint \ Gamma \ mathrm {\ nabla} \ varphi \ cdot \ mathrm {d} \ overrightarrow {\ mathrm {A}} + {\ int} _ {\ mathrm { V}} {\ mathrm {S}} _ {\ varphi} \ mathrm {dV} $$ (1 *)

onde ρ indica densidade; \ (\ overset {\ rightharpoonup} {v} \) é o vetor velocidade; \ (\ overset {\ rightharpoonup} {A} \) é o vetor da área da superfície; V é o volume; Γ é o coeficiente de difusão para ϕ e S ϕ é o termo de origem de ϕ por unidade de volume. O símbolo ϕ pode ser substituído por 1 para a equação de continuidade, u , v e w são as equações de momento nas direções X, Y e Z, e Ci para as equações de transporte de espécies na câmara do reator, respectivamente. Eq. (1 *) pode ser expresso em coordenadas generalizadas usando a abordagem do método de volumes finitos para simulação. Depois de combinar as condições de contorno, a Eq. (1 *) pode ser linearizado e expresso no domínio computacional como um conjunto de equações algébricas, que podem ser resolvidos pelo algoritmo SIMPLE usando a técnica CFD [19]. Observou que a maioria dos dispositivos de fabricação de semicondutores operam muito abaixo da pressão atmosférica. Em tais pressões baixas, o fluxo de fluido está no regime de deslizamento e as condições de limite não deslizantes normalmente usadas para velocidade e temperatura não são mais válidas. O presente fluxo de plasma a pressão muito baixa está no regime de deslizamento, que está entre o fluxo molecular livre e o regime contínuo [20]. Portanto, as condições de limite de deslizamento para velocidade e temperatura para modelagem de fluxo de fluido são impostas em nossas simulações numéricas.

Os materiais semicondutores Si (s) e Ge (s) são gravados na superfície do susceptor aquecido, governados pelas seguintes reações de superfície:

$$ {\ mathrm {Cl}} _ 2+ \ mathrm {Si} ={\ mathrm {SiCl}} _ 4 $$ (2 * .1) $$ 4 \ mathrm {HBr} + \ mathrm {Si} ={\ mathrm {SiBr}} _ 4 + 2 {\ mathrm {H}} _ 2 $$ (2 * .2) $$ 2 {\ mathrm {Cl}} _ 2+ \ mathrm {Ge} ={\ mathrm {GeCl}} _ 4 $$ (2 * .3) $$ 4 \ mathrm {HBr} + \ mathrm {Ge} ={\ mathrm {GeBr}} _ 4 + 2 {\ mathrm {H}} _ 2 $$ (2 * .4)

As reações químicas são semelhantes para a corrosão de Si na Eq. (2 * .1) e Eq. (2 * .2), ou Ge etching na Eq. (2 * .3) e Eq. (2 * 0,4). Assim, o processo de corrosão do Si pela mistura de cloro e brometo de hidrogênio é demonstrado nas simulações a seguir.

Resultados e discussão

Caracterização do material

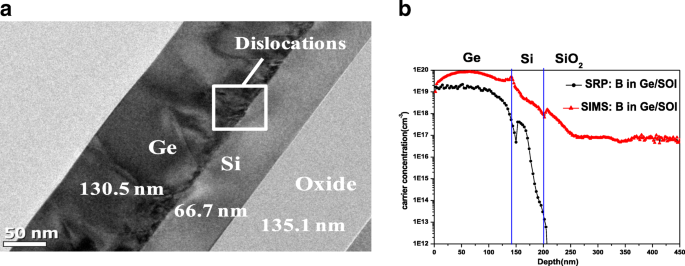

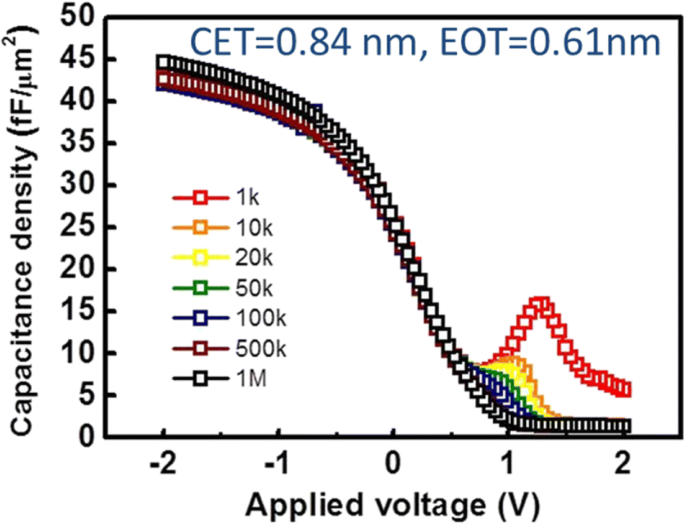

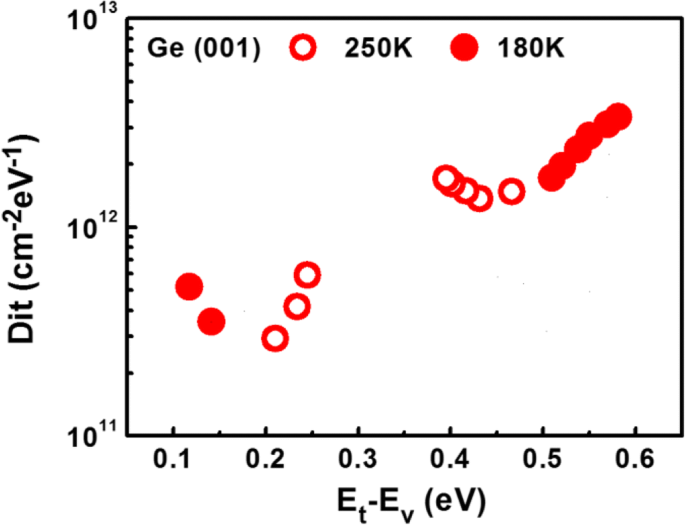

Imagens TEM de seção transversal da camada Ge formada no substrato SOI são mostradas na Fig. 2a. Como pode ser visto, deslocamentos desajustados estão presentes na interface Ge / Si; estes, por sua vez, resultam em deslocamentos de rosca no filme epitaxial de Ge. Acredita-se que esses deslocamentos de rosqueamento acomodem a incompatibilidade térmica entre Ge e Si. A maioria dos deslocamentos de threading terminaram dentro de 80 nm da interface; no entanto, muitos também se propagaram para a superfície do filme. O filme epitaxial de Ge no substrato SOI foi implantado com boro e posteriormente ativado, a fim de examinar a distribuição do dopante e o nível de ativação. Para a parte superior de 130 nm da camada de Ge, a taxa de ativação de boro foi de ∼ 85%, conforme mostrado no PCOR-SIMS e perfis de resistência ao espalhamento (SRP). (ver Fig. 2b). A concentração do orifício caiu significativamente no caso da parte inferior da camada Ge próxima à interface Ge / Si, devido à presença de defeitos e aos limites de medição do SRP. No caso dos dispositivos fabricados, o Ge defeituoso próximo à interface Ge / Si foi removido por corrosão seletiva; portanto, as medições PCOR-SIMS e SRP realizadas no canal devem ser precisas. O nível máximo de ativação de ~ 3 × 10 19 cm −3 é totalmente consistente com o limite de ativação convencional. Observe que, devido à ativação em baixa temperatura (550 ° C) realizada durante a implantação do boro, o S / D próximo ao canal de Si parasita era altamente resistivo (Fig. 2); isso evitou a condução de Si parasita. A Figura 3 mostra as características de capacitância-tensão (CV) do TiN / ZrO 2 / Condensadores semicondutores isolantes de metal Ge (MISCAPs). Para prevenir a formação de um GeO instável x camada durante a deposição dielétrica de alto k e processo de recozimento pós-deposição, o material à base de nitreto Ge 3 N 4 e não GeO 2 foi inserido como a camada de interface na superfície Ge (001) por meio de um NH 3 / H 2 tratamento de plasma remoto. O ZrO 2 camada foi depositada a 250 ° C por 20 ciclos por deposição da camada atômica. As curvas CV medidas não indicam dispersão de frequência ou alongamento de 1 KHz a 1 MHz e são consistentes. A perda, que cria níveis de armadilha perto do ZrO 2 / Ge interface, desloca a energia de ativação térmica para a geração de portadores minoritários daquela correspondente à energia do bandgap p-Ge para a energia do midgap. A espessura de óxido equivalente (EOT) é de 0,6 nm e o D it (Densidade de interceptação de interface) o valor é ~ 3 × 10 12 cm 2 eV −1 próximo ao midgap, conforme medido pelo método de condutância de baixa temperatura (veja o detalhe da Fig. 4).

a A imagem TEM do tipo p Ge em substrato SOI. b Os perfis SIMS e SRP da camada epi-Ge dopada com boro in situ no SOI. A concentração do orifício é baixa no Ge defeituoso de fundo perto da interface Ge / Si

Características C-V do TiN / ZrO 2 / Ge MISCAPs com EOT ~ 0,6 nm

Dit medido pelo método de condutância de baixa temperatura

Simulação para os parâmetros de operação do reator

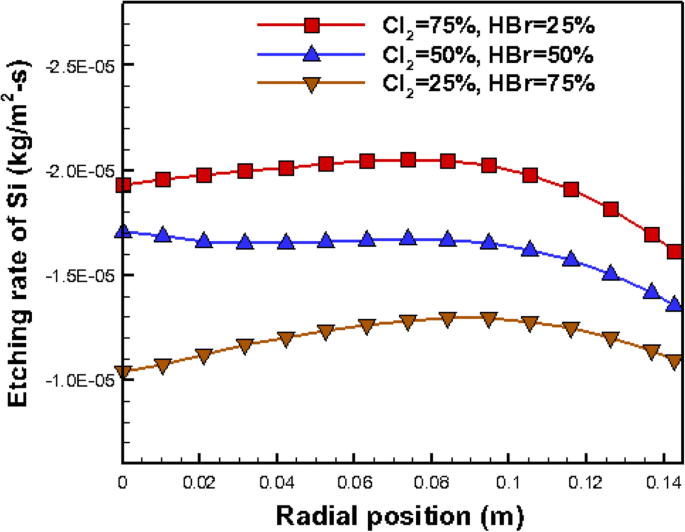

Um modelo típico de fluxos de plasma laminar constantes foi simulado em computadores pessoais de alta velocidade. O gás de entrada é uma mistura de Cl 2 , que tem uma fração de massa de 0,75, e HBr, que tem uma fração de massa de 0,25. A Figura 5a ilustra contornos do influxo de baixa temperatura, operando em temperatura mais alta no interior e as linhas de caminho de partículas na câmara do reator. A Figura 5b mostra os contornos da fração de massa do produto SiCl4, que possui baixa concentração acima do susceptor e alta concentração abaixo do susceptor para a saída. Além disso, maior fração de massa de Cl 2 obtém um bom desempenho na corrosão, e este know-how foi validado por simulações presentes como mostrado na Fig. 6. O eixo horizontal representa ao longo de uma posição radial no susceptor e o eixo vertical indica a taxa de corrosão (kg / m 2 s) de Si. A Figura 6 mostra que o melhor processo de corrosão é arquivado pela mistura de entrada de 75% Cl 2 e 25% de HBr, mistura essa que foi adotada para os experimentos deste estudo.

Contornos de parâmetros de plasma dentro do reator. a Distribuição de temperatura e linhas de caminho de partículas r. b Contornos da fração de massa do produto SiCl 4

Taxas de corrosão de Si no susceptor de misturas de gases de entrada com várias frações

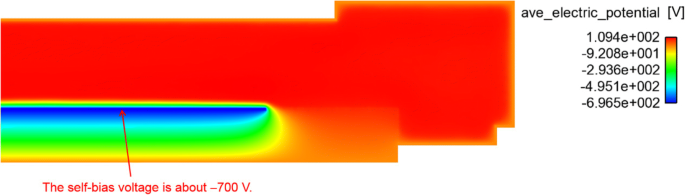

Outro caso que mostra a viabilidade de experimentos auxiliados por computador é a distribuição de potencial elétrico na câmara para corrosão por plasma. Com base no mecanismo subjacente deste processo de corrosão, um modelo de simulação 2D foi desenvolvido para a distribuição da densidade de potência do plasma como mostrado na Fig. 7 e foi usado para ajustar os dados de medição, a fim de confirmar a precisão do modelo e auxiliar o experimento.

Simulação de distribuição de potencial elétrico para corrosão de plasma na câmara

Conforme proposto por Sugai [21], a tensão de polarização automática pode estar relacionada às capacitâncias da bainha do eletrodo de RF (C K ) e eletrodo de aterramento (C A ), e expresso da seguinte forma:

$$ {V} _ {\ mathrm {DC}} =\ frac {C _ {\ mathrm {K}} - {C} _ {\ mathrm {A}}} {C _ {\ mathrm {K}} + {C } _ {\ mathrm {A}}} \ {V} _ {\ mathrm {RF}} $$ (3 *)

De acordo com as presentes simulações, conforme mostrado na Fig. 7, a tensão de polarização automática é de cerca de - 700 V, que está perto do valor teórico, - 650 V, conforme calculado a partir da Eq. (3 *). Portanto, sugere-se que a otimização seja realizada por meio de simulações, a fim de não só ajustar os parâmetros do processo utilizados, mas também modificar o hardware empregado. Isso ajudará a garantir a uniformidade em toda a execução e resultará em processos de alta qualidade e baixo custo que são otimizados.

Fabricação e caracterização de dispositivos

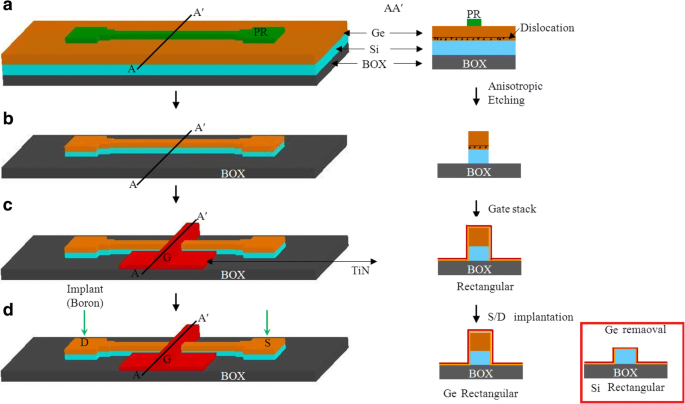

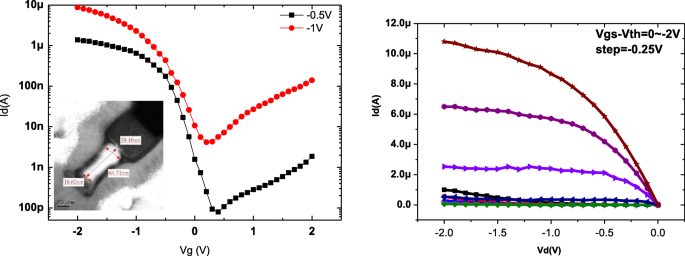

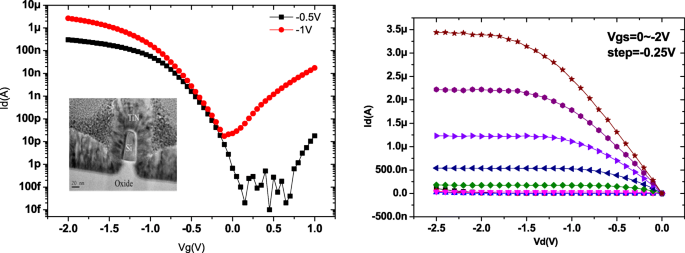

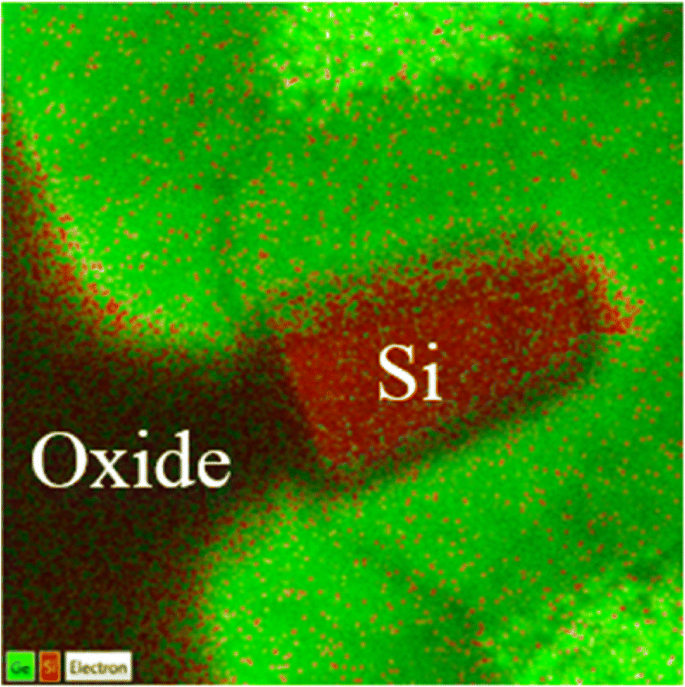

A camada epitaxial Ge foi padronizada em aletas com os tamanhos de recursos desejados usando litografia de feixe eletrônico. A barbatana foi formada por ataque anisotrópico com Cl 2 / Plasma baseado em HBr para remover o Ge de alto defeito perto da interface Ge / Si. A nadadeira flutuante de Ge no SOI foi formada com a maior seletividade de corrosão do Ge do que do Si e a taxa de corrosão aprimorada da região defeituosa [4]. A SiO 2 A camada de cobertura foi então depositada e tornou-se o espaçador após a padronização da porta. Depois de definir a região ativa, as pilhas de portas de ZrO 2 camada foram formadas por ALD, respectivamente. As seções transversais do canal de dispositivos fabricados são mostradas na Fig. 8. A largura da aleta ( W fin ) é usado para a concentração de canal de 8 × 10 19 cm - 3 que é extraído usando o método van der Pauw em uma camada cobertor Ge epi em SOI. Observe que a controlabilidade do canal diminui com o aumento da concentração do canal e o aumento de W fin [12, 13]. A grande concentração de canal requer o pequeno W fin para manter o SS baixo. Por fim, os eletrodos de porta foram definidos e depositados. A Figura 9 mostra as características de saída e transferência de um Ge FinFET triangular com largura de aleta ( W fin ) de 18 nm e comprimento de porta ( L g ) de 90 nm. O eu em / eu desligado proporção do Ge JL-FET é tão alta quanto 10 5 e a oscilação de sublimiar (SS) é ~ 100 mV dec - 1 . As características de transferência do Si JL-FET são mostradas na Fig. 10. O I em / eu desligado proporção do Si JL-FET é alta como ~ 10 8 , seu SS é 90 mV dez - 1 , é L g é 80 nm, e seu W fin é de 20 nm. A Figura 8 também mostra que a amplitude da tensão da porta, Δ V g , é de aproximadamente 0,5 V e próximo ao bandgap de Ge ( E g / q =0,66 V). Isso confirma que o eu d - V g curvas mostradas na Fig. 8 são para um Ge FinFET. No entanto, a amplitude da tensão da porta, Δ V g , mostrado na Fig. 6 é de aproximadamente 1,8 V e perto do bandgap de Si ( E g / q =1,1 V) mas não o de Ge ( E g / q =0,66 V). Assim, o eu d - V g curvas mostradas na Fig. 9 são para um Si JL-FET e não um Ge JL-FET. Esta observação é baseada na física do dispositivo semicondutor e é suportada pelo I experimentalmente determinado d - V g curvas do Ge e Si FinFETs, bem como os mapas de seção transversal TEM / EDS Si. Duas coisas são evidentes nas inserções na Fig. 11. As inserções mostram as características de saída e transferência do inesperado Si JL-FET após o overetching de Ge; o eu em / eu desligado proporção deste dispositivo é tão alta quanto 10 8 . No entanto, sua corrente LIGADA é de apenas 17 μA μm - 1 em - 1 V. O alto I em / eu desligado a proporção é atribuível à camada de Si e não à camada de Ge. Quando apenas a camada de Si é deixada, o dispositivo é na verdade um Si JL-FET em vez de um Ge JL-FET.

Esquema da fabricação do dispositivo. a Padrões de barbatanas. Os materiais de partida são Ge (130 nm) na CAIXA. b Gravura anisotrópica e listras fotorresistentes. c Formação de portas por deposição de camada atômica de ZrO 2 e deposição de TiN. d Implantação de boro autoalinhada em S / D para bom contato. Nota:o lado esquerdo é o esquema 3D e o lado direito é a vista transversal correspondente

eu d - V ge eu d - V d curva para o Ge FinFET

eu d - V ge eu d - V d para o Si FinFET depois que o Ge superior é descuidadamente gravado. Embora eu em / eu desligado pode chegar a 10 8 , seu valor atual é muito baixo

Mapeamento TEM para a estrutura do canal que passa por um processo de sobredimensionamento

Conclusões

Confirmamos a relação entre o modelo de simulação e os dados de medição. Portanto, sugere-se que a otimização seja realizada por meio de simulações, a fim de não só ajustar os parâmetros do processo utilizados, mas também modificar o hardware empregado. Com o auxílio de simulações numéricas para determinar os parâmetros operacionais do reitor, mostramos que os parâmetros do processo de corrosão para formação de canais Ge / Si podem ser otimizados por meio de experimentos, a fim de melhorar o processo de corrosão e auxiliar no desenvolvimento de transistores por melhorando a qualidade de fabricação e diminuindo o custo de produção. Os resultados experimentais indicaram que a técnica de corrosão seca desenvolvida para Ge FinFETs também é extremamente útil para a fabricação de dispositivos CMOS de aletas altas.

Nanomateriais

- Tecnologias de Deposição de Camada Atômica Avançada para Micro-LEDs e VCSELs

- Engenharia de processo de revestimento por imersão e otimização de desempenho para dispositivos eletrocrômicos de três estados

- Características interfaciais, elétricas e de alinhamento de banda de pilhas de HfO2 / Ge com camada intermediária de SiO2 formada in situ por deposição de camada atômica aprimorada com plasma

- Dopagem Substitucional para Mineral Aluminossilicato e Desempenho Superior de Divisão de Água

- Características ópticas e elétricas de nanofios de silício preparados por corrosão eletrolítica

- Os efeitos da relação Li / Nb na preparação e desempenho fotocatalítico de compostos Li-Nb-O

- Ajustando as morfologias de superfície e propriedades dos filmes ZnO pelo projeto da camada interfacial

- Preparação e desempenho fotocatalítico de fotocatalisadores de estrutura oca LiNb3O8

- Os efeitos de acoplamento de polaritons de plasma de superfície e ressonâncias de dipolo magnético em metamateriais

- Gravação a Laser e Gravação a Laser